Знакомство с превосходными проектами с открытым исходным кодом Verilog/FPGA (39) — NVMe

NVME

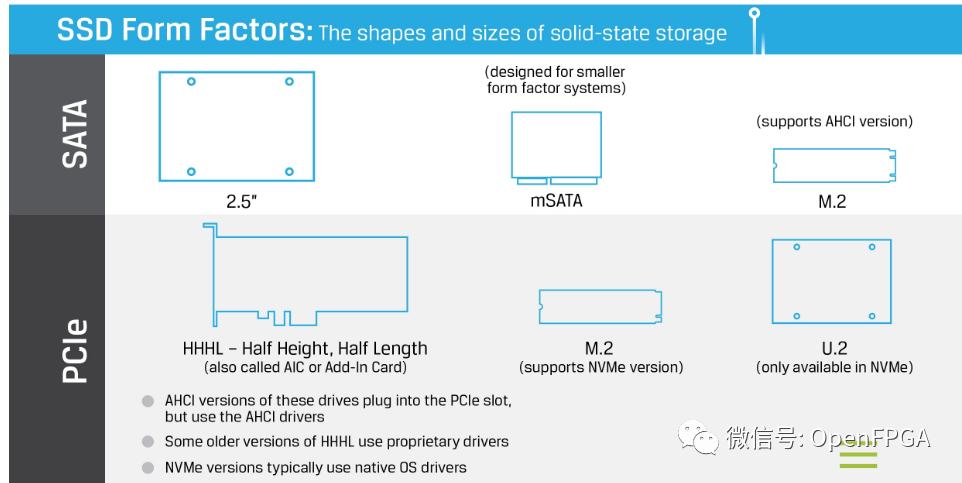

NVM Express (NVMe) или спецификация интерфейса хост-контроллера энергонезависимой памяти (NVMHCIS) — это спецификация интерфейса открытого логического устройства для доступа к энергонезависимым носителям информации компьютера, подключенным через шину PCI Express. Аббревиатура NVM означает энергонезависимую память, обычно флэш-память NAND, которая поставляется в различных физических форм-факторах, включая твердотельные накопители (SSD), карты расширения PCIe и M.2 (преемник mSATA). .

Архитектурно логика NVMe физически хранится внутри и выполняется микросхемой контроллера NVMe, которая физически совмещена с носителем данных (обычно SSD). Изменения версии NVMe (например, с 1.3 на 1.4) включаются в носитель данных и не влияют на компоненты, совместимые с интерфейсом PCIe, такие как материнские платы и процессоры.

Различия во внешнем виде между SATA и NVME Источник изображения: официальный сайт Kingston

FPGA реализует NVME

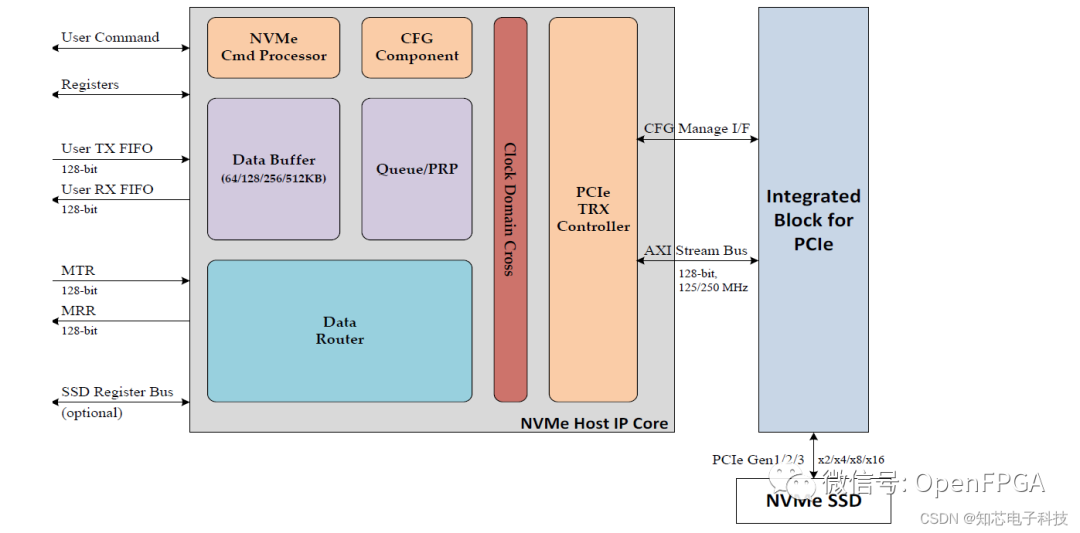

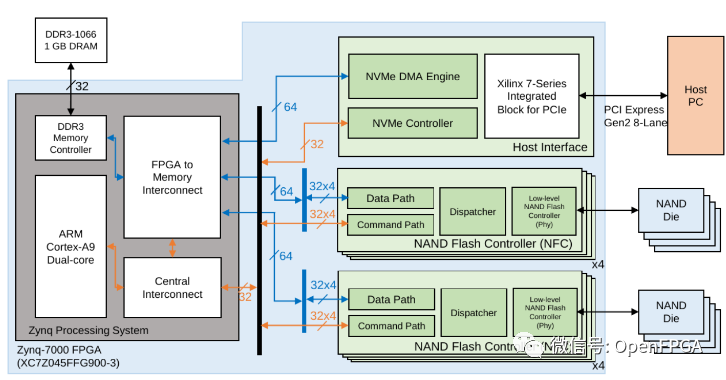

Протокол NVMe основан на протоколе PCIe и обеспечивает высокоскоростную передачу данных между хостом NVMe и SSD-накопителем NVMe. Простая архитектура, реализованная FPGA, выглядит следующим образом:

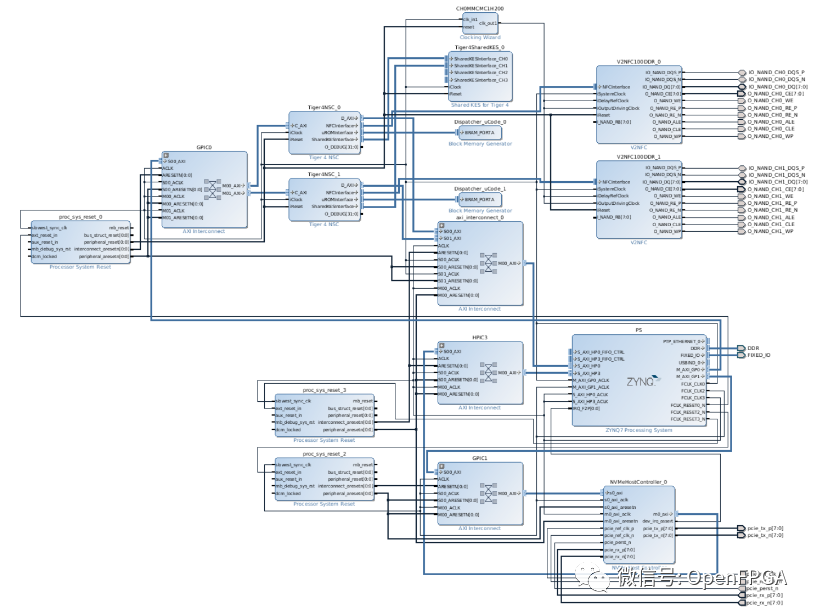

FPGA осуществляет управление NVME (см. водяной знак для источника изображения)

Ниже представлены несколько реализаций протокола NVME с открытым исходным кодом.

OpenSSD+nvme storage

❝https://github.com/Cosmos-OpenSSD/Cosmos-plus-OpenSSD ❞

❝https://github.com/giuseppedongiovanni/nvme_comp_storage ❞

представлять

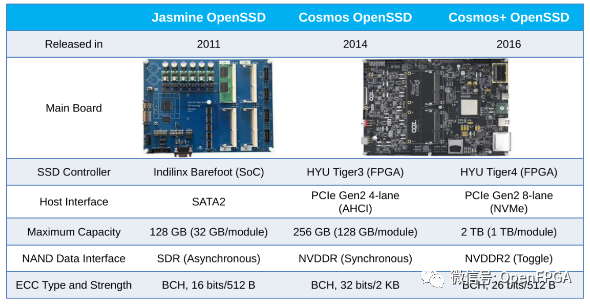

История развития OpenSSD такова:

Проект nvme_comp_storage — это система хранения данных на базе OpenSSD. Подробная архитектура выглядит следующим образом:

Оба проекта имеют исключительно подробную документацию, ссылка на которую приведена ниже:

❝https://github.com/Cosmos-OpenSSD/Cosmos-plus-OpenSSD/tree/master/doc ❞

❝https://github.com/giuseppedongiovanni/nvme_comp_storage/blob/master/Project_Documentation.pdf ❞

Среди них у OpenSSD есть официальный сайт. На момент публикации этой статьи доступ к официальному сайту ограничен~.

antmicro for nvme

❝https://github.com/antmicro/nvme-verilog-pcie ❞

❝https://github.com/antmicro/openssd-nvme ❞

Этот проект аналогичен вышеуказанному проекту,Разница лишь в том, что весь код в этом проекте от нижнего уровня PCIe приезжать до верхнего уровня написан мной (в проекте PCIe есть достоинство),Проекты, которые не хотят полагаться на официальную интеллектуальную собственность,Этот проект имеет большое справочное значение.

Неординарный проект этого президента не будет описываться подробно.

NVMe

❝https://github.com/mcrl/NVMe ❞

представлять

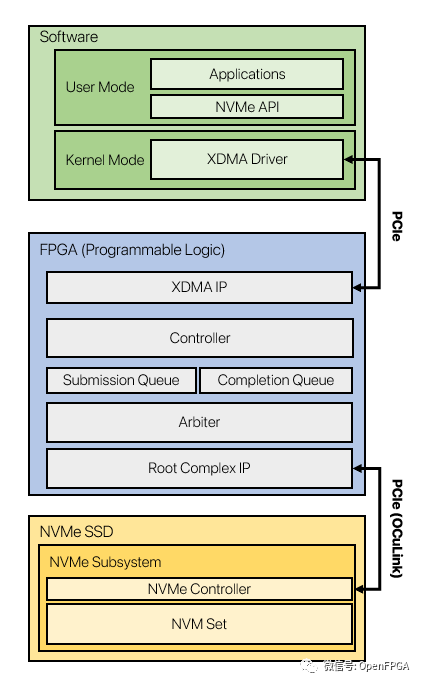

Этот проект основан на контроллере NVME AMD-XILINX FPGA XDMA. Подробная структура файла выглядит следующим образом:

NVMe/

├── hw/ (RTL codes)

│ ├── COMSTRAINTS/ (Constraints : Board connections)

│ ├── IP/ (IPs : ILA, XDMA IP, Board design)

│ ├── RTL/ (NVMe Hardware Driver RTL codes)

│ ├── scripts/

│ ├── SIM/

│ └── SYNTH/ (NVMe Hardware Driver Project directories)

├── sw/ (NVMe suFile Library)

├── SIM/

├── README.md

├── LICENSE

└── CMakeLists.txt

Контроллер NVMe с аппаратным ускорением

❝https://github.com/FDU-ME-ARC/NVMeCHA ❞

представлять

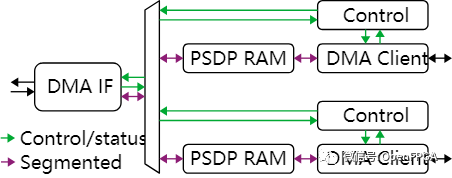

NVMeCHA — это контроллер NVMe со сверхнизкой задержкой и высокой пропускной способностью с высокопараллельной, конвейерной и масштабируемой архитектурой, включающей контроллер управления и несколько контроллеров ввода-вывода с полной аппаратной автоматизацией. Контроллер управления представляет собой совместную программно-аппаратную разработку, в которой сложная обработка команд управления NVMe управляется программным обеспечением, а передача данных через PCIe осуществляется аппаратно. Эта гибридная архитектура сочетает гибкость программного обеспечения с эффективностью оборудования, сокращая ресурсы ЦП и повышая производительность. Контроллер ввода-вывода имеет высокопараллельную и конвейерную аппаратную архитектуру, позволяющую обрабатывать множество команд ввода-вывода NVMe параллельно без какого-либо вмешательства программного обеспечения. Каждый контроллер ввода-вывода соответствует паре очередей ввода-вывода NVMe.

Проект проверяется на плате Xilinx KCU105 FPGA, которая подключается к компьютеру через интерфейс PCIe gen3 x8. По оценкам с помощью инструмента тестирования SPDK-Perf, максимальная пропускная способность чтения и записи контроллера NVMe может достигать 7,0 ГБ/с, что составляет 89% теоретической пропускной способности PCIe. Максимальная пропускная способность чтения/записи 4 КБ может достигать 1,7 миллиона операций ввода-вывода в секунду (MIOPS). Средняя задержка чтения/записи для размера 4 КБ составляет всего 2,4 мкс/3,2 мкс.

В рамках этого проекта также публикуется статья: Транзакции IEEE по автоматизированному проектированию интегральных схем и систем, номер документа: 10.1109/TCAD.2021.3088784.

pl-nvme

❝https://github.com/DUNE/pl-nvme ❞

❝https://github.com/yu-zou/DirectNVM ❞

представлять

Этот проект похож на приведенный выше проект, но производительность не такая высокая, как у вышеупомянутой архитектуры.

Проект содержит исходный код системы Dune NvmeStorage, а также простую среду тестирования NVMe, которая позволяет проверять интерфейс с использованием низкоуровневых FPGA Xilinx.

Содержит исходный код FPGA, среду моделирования или прошивку Nvme test FPGA, а также хост-программу nvme_test.

Подвести итог

Поскольку часть NVME по сути тесно связана с FPGA PCIe, она, по сути, появляется одновременно с проектом PCIe. Тем, кто хочет реализовать ее снизу, настоятельно рекомендуется проект antmicro.

Реализуйте загрузку файлов с использованием минимального WEB API.

Демо1 Laravel5.2 — генерация и хранение URL-адресов

Spring boot интегрирует Kafka и реализует отправку и потребление информации (действительно при личном тестировании)

Мысли о решениях по внутренней реализации сортировки методом перетаскивания

Междоменный доступ к конфигурации nginx не может вступить в силу. Междоменный доступ к странице_Page

Как написать текстовый контент на php

PHP добавляет текстовый водяной знак или водяной знак изображения к изображениям – метод инкапсуляции

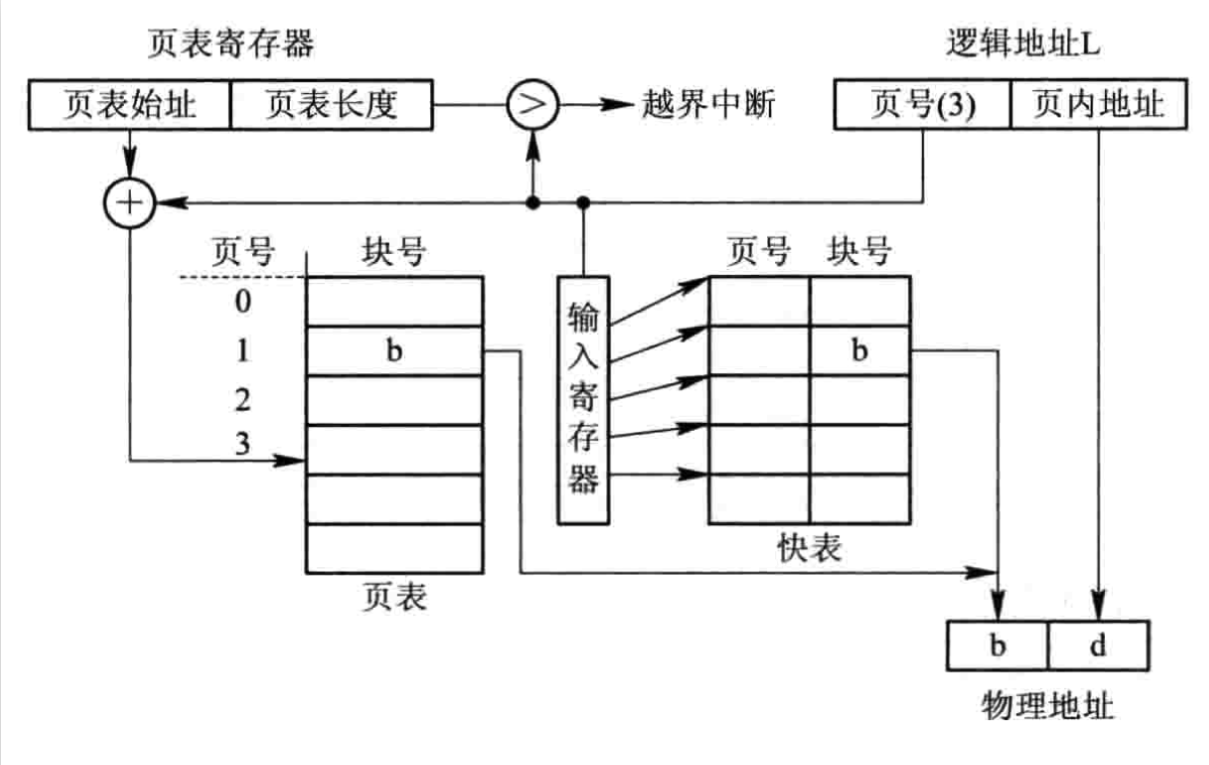

Интерпретация быстрой таблицы (TLB)

Интерфейс WeChat API (полный) — оплата WeChat/красный конверт WeChat/купон WeChat/магазин WeChat/JSAPI

Преобразование Java-объекта в json string_complex json-строки в объект

Примените сегментацию слов jieba (версия Java) и предоставьте пакет jar

matinal: Самый подробный анализ управления разрешениями во всей сети SAP. Все управление разрешениями находится здесь.

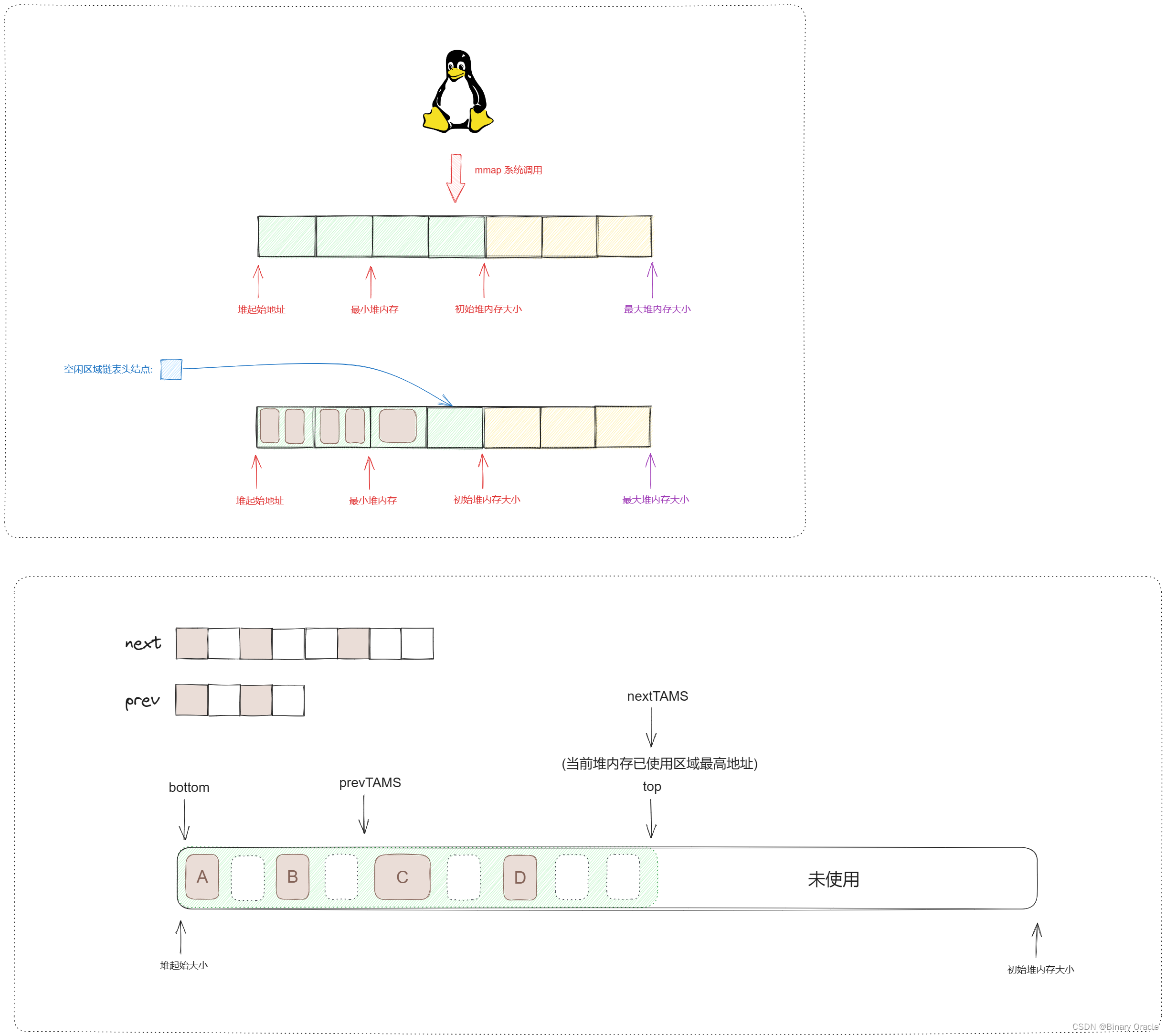

Коротко расскажу обо всем процессе работы алгоритма сборки мусора G1 --- Теоретическая часть -- Часть 1

[Спецификация] Результаты и исключения возврата интерфейса SpringBoot обрабатываются единообразно, поэтому инкапсуляция является элегантной.

Интерпретация каталога веб-проекта Flask

Что такое подробное объяснение файла WSDL_wsdl

Как запустить большую модель ИИ локально

Подведение итогов десяти самых популярных веб-фреймворков для Go

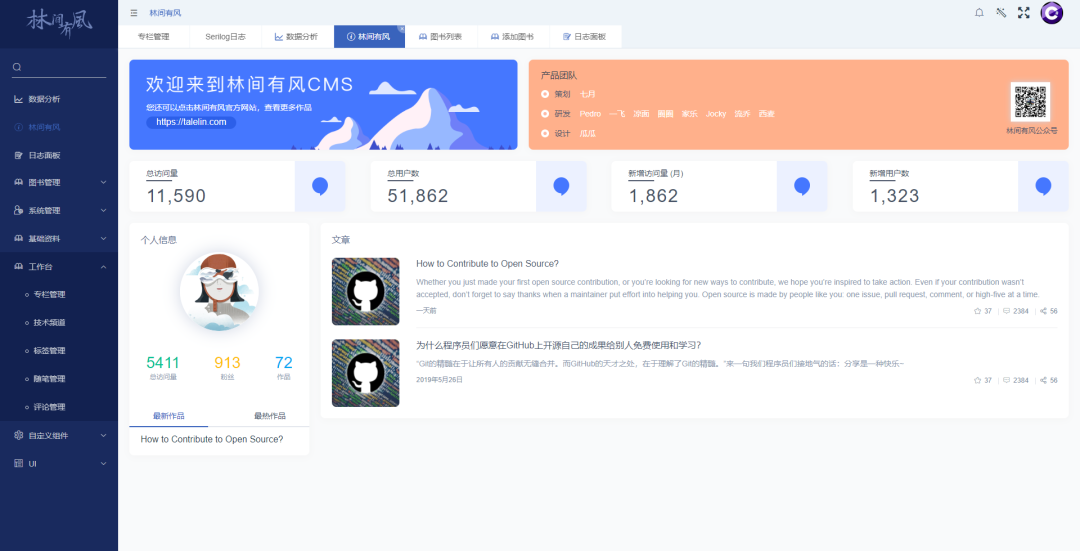

5 рекомендуемых проектов CMS с открытым исходным кодом на базе .Net Core

Java использует httpclient для отправки запросов HttpPost (отправка формы, загрузка файлов и передача данных Json)

Руководство по развертыванию Nginx в Linux (Centos)

Интервью с Alibaba по Java: можно ли использовать @Transactional и @Async вместе?

Облачный шлюз Spring реализует примеры балансировки нагрузки и проверки входа в систему.

Используйте Nginx для решения междоменных проблем

Произошла ошибка, когда сервер веб-сайта установил соединение с базой данных. WordPress предложил решение проблемы с установкой соединения с базой данных... [Легко понять]

Новый адрес java-библиотеки_16 топовых Java-проектов с открытым исходным кодом, достойных вашего внимания! Обязательно к просмотру новичкам

Лучшие практики Kubernetes для устранения несоответствий часовых поясов внутри контейнеров

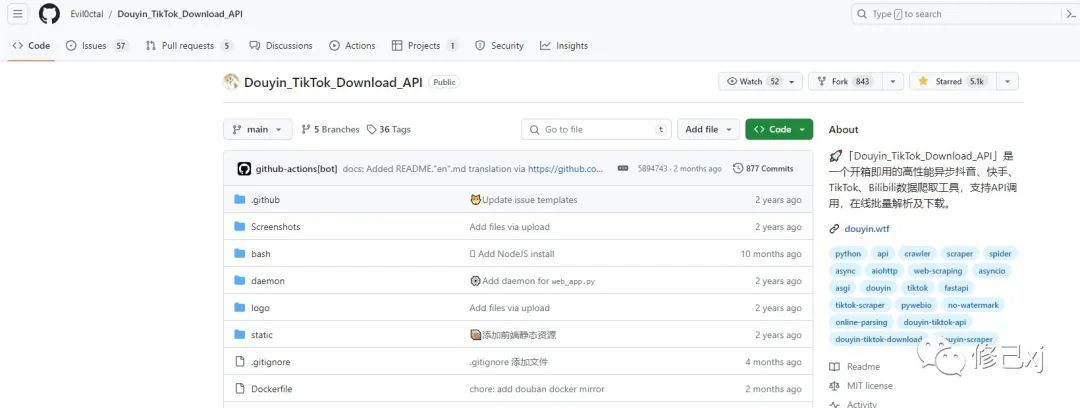

Введение в проект удаления водяных знаков из коротких видео на GitHub Douyin_TikTok_Download_API

Весенние аннотации: подробное объяснение @Service!