Введение в превосходные проекты Verilog/FPGA с открытым исходным кодом (21) - Сверточная нейронная сеть (CNN)

представлять

В глубоком обучении сверточная нейронная сеть (CNN или ConvNet) — это тип искусственной нейронной сети (ИНС), наиболее часто используемый для анализа визуальных изображений.

CNN также называют инвариантными по сдвигу или пространственно-инвариантными искусственными нейронными сетями (SIANN). Они основаны на архитектуре с общим весом ядер или фильтров свертки, которая скользит по входным функциям и обеспечивает функции, называемые функциями отображения трансляционного эквивариантного ответа. У них есть приложения для распознавания изображений и видео, систем рекомендаций, классификации изображений, сегментации изображений, анализа медицинских изображений, обработки естественного языка, интерфейсов «мозг-компьютер» и финансовых временных рядов.

CNN — это регуляризованная версия многослойного перцептрона. Многослойный персептрон обычно представляет собой полностью связную сеть, т. е. каждый нейрон одного слоя связан со всеми нейронами следующего слоя. «Полная связность» этих сетей делает их склонными к переобучению данных. Типичные способы регуляризации или предотвращения переобучения включают в себя: наложение штрафов на параметры во время обучения (например, снижение веса) или сокращение связности (пропуск соединений, выпадение и т. д.). CNN используют различные методы регуляризации: они используют иерархические шаблоны в данных и используют меньшие, более простые шаблоны, запечатленные в фильтре для сборки узоров возрастающей сложности. Таким образом, по шкале связности и сложности CNN находятся на нижнем полюсе.

По сравнению с другими алгоритмами классификации изображений, CNN используют относительно небольшую предварительную обработку. Это означает, что сеть учится оптимизировать фильтры (или ядра) посредством автоматического обучения, тогда как в традиционных алгоритмах эти фильтры разрабатываются вручную. Эта независимость от предварительных знаний и вмешательства человека в извлечение признаков является основным преимуществом.

cnn_hardware_acclerator_for_fpga

https://github.com/sumanth-kalluri/cnn_hardware_acclerator_for_fpga

https://thedatabus.io/introduction

Это полностью параметрическое Verilog Внедрите CNN, чтобы сомневаться FPGA начальствоизсвертканервсетьрассуждение

Программные инструменты:

Дизайн - Xilinx Vivado 2017

Проверка — инструменты командной строки Python 3.6 и Xilinx ISE 14.7

convolution_network_on_FPGA

https://github.com/hunterlew/convolution_network_on_FPGA

описывать

В этом проекте используется ISE 14.7 и vertix-7 FPGA Строить. Используются определенные сложности при выполнении стратегий. 7 Прямой расчет сети слоев. Сначала используйте MatConvNet в MSTAR Тренируйтесь на наборе данных SAR целевая классификационная сеть и использование ранняя остановка. Затем используйте Matlab Преобразуйте веса и введите в FPGA Можно загрузить COE документ. Далее, нативный дизайн verilog Модель, написанная для завершения прямого расчета. Использование системы 16 данные с фиксированной точкой для обеспечения точности. Оказывается, это стоит меньше 1 мс, лучше, чем у других вычислительных платформ.

ускоряться

Для первого преобразования требуется FPGA Существует компромисс между ресурсами и скоростью, принимая во внимание размер входных данных и веса при первом преобразовании: если слой больше, то слой должен использовать структуру сдвигового регистра. Еще одно преобразование: слой требует только использования структуры трубы. Обратите внимание, что иметь 18 файлы с m_conv_1 Именованный, с указанием первого conv Есть 18 сдвиговый регистр.

Для ограничений пропускной способности второй уровень преобразования использует схему распараллеливания группировки каналов. использовать v7-415t и v7-485t FPGA Для сравнения они используют разные номера групп (4 vs 1). Можно отметить, что файл CNN_top.v планировать в,Содержит группировку каналов управленияикомбинированные сигналы“ram_ready”。

CNN-FPGA

https://github.com/QShen3/CNN-FPGA

Имеются следующие модули:

Conv2d

проиллюстрировать:

Модуль свертки может выполнять двумерную свертку. Поддерживает несколько ядер свертки, различную длину синхронизации, возможность включения заполнения края 0 и т. д.

Настраиваемые параметры:

PADDINGENABLE Если край заполнен 0, 1 означает да, 0 означает нет 0

Ввод и вывод:

Max_pool

проиллюстрировать:

Модуль максимального пула может выполнять максимальные операции пула на входе.

Настраиваемые параметры:

Ввод и вывод:

FPGA-CNN

https://github.com/dem123456789/FPGA-CNN

CNN реализован с помощью FPGA:

CNN.v — это проект верхнего уровня, инициализирующий A, B и I. Шаблон представляет собой модуль слоя 16x16.

SixteenbySixteen.java генерирует код Verilog

clacc

https://github.com/taoyilee/clacc

Первоначально это был курсовой проект по аппаратному обеспечению глубокого обучения в Университете Цинхуа, лекции по которому читал профессор Линь Юньлун. Этот курс эквивалентен CS231n Стэнфордского университета (http://cs231n.stanford.edu/).

Глубокое обучение затруднение (сверточная нейронная сеть)

Это в Verilog Реализация похожа на MIT Eyeriss глубокое обучениеускорятьсяустройство

Примечание: clacc означает сверточный слой сложности.

RTL-Implementation-of-Two-Layer-CNN

https://github.com/Haleski47/RTL-Implementation-of-Two-Layer-CNN

https://github.com/Di5h3z/ECE-564-Convolutional-Neural-Network-Accelerator

Двухслойная CNN с детальным проектированием

Детальная проектная документация:

https://github.com/Haleski47/RTL-Implementation-of-Two-Layer-CNN/blob/master/report/Apar%20Bansal%20ECE564%20Project.pdf

NTHU-ICLAB

https://github.com/LeoTheBestCoder/NTHU-ICLAB

Это очень подробный проект, предоставленный IC LAB Университета Цинхуа, который постепенно внедряет CNN и поставляется с тестовым проектом.

Ниже приведены функции каждого шага, и каждый шаг имеет подробную проектную документацию.

Окончательная реализация: классификация цифр с использованием CNN.

ES203-COA-CNN

https://github.com/akcgjc007/ES203-COA-CNN

Конкретный процесс реализации:

кодпредставлять:

https://www.youtube.com/watch?v=3J2X-j0z2M8

результат:

MNIST_CNN_HDL

https://github.com/makifozkanoglu/MNIST_CNN_HDL

https://github.com/flystandard1/CNN_hardware_ECE1718_UofT

через оборудованиеускорятьсяпродвигать CNN-mnist производительность

Папка «design_files» содержит все файлы дизайна в оборудовании.

Папка «verification_files» — это среда проверки файлов дизайна.

В папке «веса» находятся mnist и Вес входного изображения

CNN-Implementation-in-Verilog

https://github.com/boaaaang/CNN-Implementation-in-Verilog

использовать Python & Verilog Реализация сверточной нейронной сети

Блок-схема реализации:

Моделирование формы волны

CNN_Core

https://github.com/0x5b25/CNN_Core

- использовать Altera Avalon-MM автобус

- использовать quartus prime ide существовать Stratix IV компилировать наитест。

- Дополнительную информацию о достоинствах можно найти в файле Instructions.txt.

CNN-Accelerator-VLSI

https://github.com/lirui-shanghaitech/CNN-Accelerator-VLSI

Подробные требованиясуществовать./resource/Project_2.0.pdfЕстьподробныйпредставлять。

Некоторые из основных требований перечислены ниже:

- Разрядность входной карты признаков и вес равны 8 бит, вывод 25 битовые данные.

- Пропускная способность входной карты объектов составляет 8x8 бит.,Весовая полоса пропускания также составляет 8x8 бит (одновременно можно считывать максимум 8 входных карт признаков и 8 весов).

- Выходная полоса пропускания составляет 2x25 бит (максимум 2 вывода, записываемых в основную память одновременно)

Результат следующий:

Примечание. Некоторые файлы, необходимые для этого проекта, не являются общедоступными, однако этот проект можно синтезировать в FPGA.

CNN-FPGA

https://github.com/omarelhedaby/CNN-FPGA

В ЗИНКЕ Реализация CNN на FPGA, классификация рукописных цифр в базе данных MNIST

сеть Conv2D->Tanh Activation->AvgPool->Conv2D->Tanh Activation->AvgPool->Conv2D->Tanh Activation->Полностью связный слой->Relu->Полностью связный слой->Softmax

Проект очень полный. Хотя файл Readme не очень полный, он содержит файлы детального проектирования, моделирования и проверки.

https://github.com/omarelhedaby/CNN-FPGA/blob/master/Hardware%20Documentation.pdf

Image-Classification-using-CNN-on-FPGA

https://github.com/padhi499/Image-Classification-using-CNN-on-FPGA

Введение

существовать FPGA начальствоиспользовать CNN Выполнить классификацию изображений

Проект о существовании FPGA Создайте обученный нейронный n/w(CIFAR-10 Набор данных), используя концепции глубокого обучения (CNN — сверточная нейронная сеть) на изображениях I/P Классифицировать.

иметь 6 Слои (свертка скользящего окна, ReLU Активация, максимальное объединение, выравнивание, полное подключение и Softmax активация) определяет нашу I/P Категория изображения. Ядра/фильтры, используемые для извлечения изображений из I/P Выполните обнаружение функции. изображение I/P Может быть в оттенках серого/цвета.

Используемые инструменты

- Vivado v17.4

- Matlab vR2018.a

DigitalRecognition

https://github.com/suisuisi/FPGAandCNN

posture_recognition_CNN

https://github.com/cxdzyq1110/posture_recognition_CNN

Введение

Распознавание жестов на основе CNN

Важно помочь машинам понять, что мы, люди, делаем с помощью камер. После достижения,Машина может по-разному реагировать на различные позы человека. Но этот процесс также очень труден,Потому что обычно этот процесс не успевает за скоростью и потребляет энергию,Это также требует очень большого объема памяти.

Здесь мы фокусируемся на распознавании жестов в реальном времени и пытаемся дать машине «знать», какие жесты мы делаем. Система распознавания жестов DE10-Nano SoC FPGA Он состоит из комплекта, камеры и монитора HDMI. SoC FPGA Захват видеопотока с камеры через CNN Модель распознает человеческую позу и, наконец, проходит HDMI В интерфейсе отображается исходное видео и результаты классификации (стоя, ходить, махание). и т. д.).

Мы загружаем наши проекты, в том числе Matlab、Python и Quartus。

Версия программного обеспечения:

- Matlab r2017b

- Python 3.6.3

- Anaconda 5.1.0

- TensorFlow-gpu 1.3.0

- Quartus 14.0

В то же время существование данного репозитория содержит статьи автора иметь,В документе содержится Детальный дизайн。

NPU_on_FPGA

https://github.com/cxdzyq1110/NPU_on_FPGA

Цель Вычислительный блок NPU реализован на базе FPGA. Умение выполнять матричные операции (ADD / ADDi / ADDs / MULT / MULTi / DOT и др.), операции обработки изображений (CONV / POOL и др.), нелинейное картографирование (RELU / TANH / СИГМ и др.).

- преимущество Учитывая гибкость,Легко изменить структуру сети,Подходит для реализации небольших CNN/RNNсетей.

- Дефекты: Из-за последовательного выполнения инструкций и отсутствия Кэша частое чтение и запись внешней памяти приводит к низкой производительности вычислений.

Этот проект также принадлежит тому же автору, что и вышеупомянутый проект Цель.,Детальный дизайн,полный проект,Это стоит сделать.

neural-engine

https://github.com/hollance/neural-engine

самый новый iPhone и iPad Оба имеют Neural Engine — специальный процессор, позволяющий машинному обучение модели становится очень быстрым,А вот как на самом деле работает этот процессор,Публика знает очень мало.

Apple Нейронный двигатель (или ANE) — это тип NPU, что означает блок нейронной обработки. это как графический процессор, но NPU нетускорятьсяграфика,Скорееускорятьсясверткаи Умножение матриц и другие нейронныесетьдействовать。

ANE не единственный НПУ - кроме Apple Кроме того, многие компании разрабатывают собственные AI Вернуться к чипу устройства. Помимо нейронного двигателя, наиболее известная NPU Это из Гугла ТПУ (или Tensor Processing Unit)。

Этот проект не является проектом по внедрению CNN, а касается Apple. Нейронный двигатель (или ANE)представлятьи сопутствующие коллекции документации。

Подвести итог

Сегодня у президента есть N проектов CNN,Предыдущие проекты были относительно «тонкими»,Подходит только для изучения CNNдизайн,Для практики больше подходят проекты начиная с NTHU-ICLAB (включительно).,Поскольку эти проектыиметь Детальный дизайн Документация и платыпроверятьпроцесс。

Объединение предыдущих проектов ТПУ и сегодняшних смежных проектов,Всем больше не стоит бояться нервов,В следующей статье мы возглавим некоторые проекты DNN,Завершите эту серию.

сравнение строк PHP

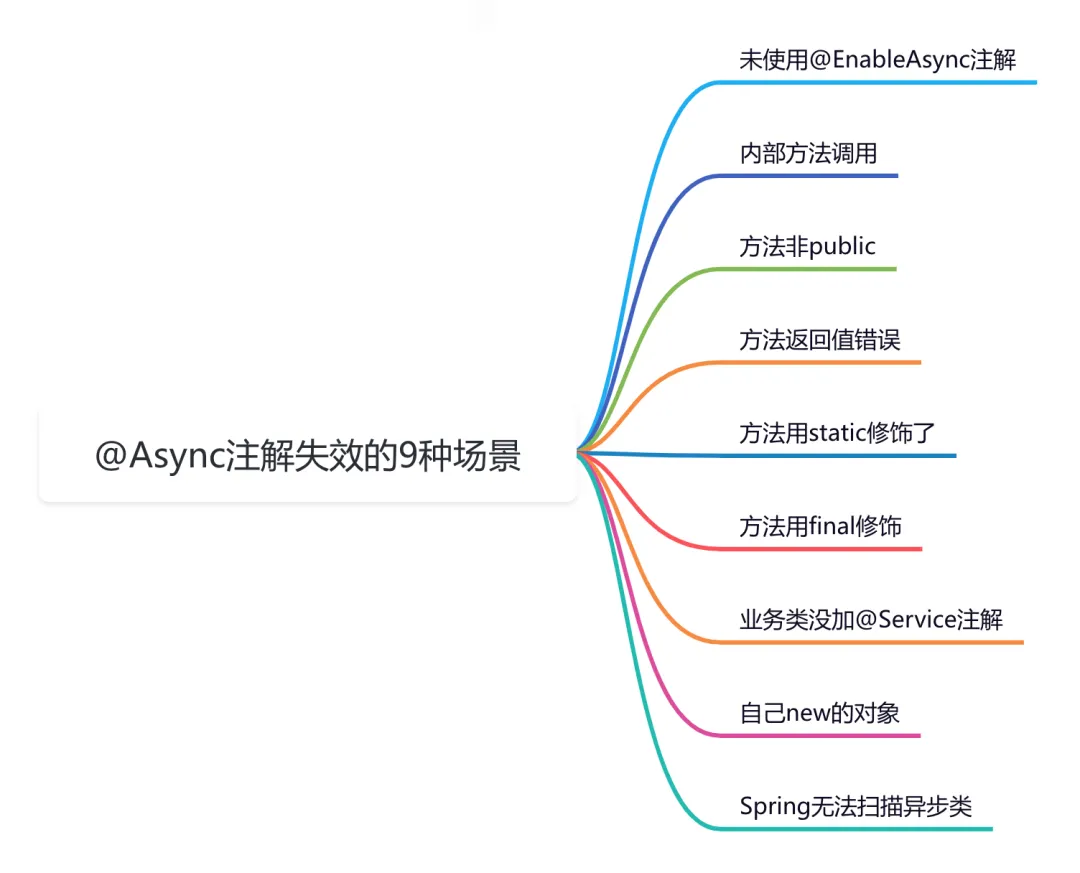

9 сценариев асинхронного сбоя @Async

Эффективная обработка запланированных задач: углубленное изучение секретов библиотеки APScheduler на Python

Рекомендации по облегченному артефакту развязки внутренних компонентов Spring Event (событие Spring)

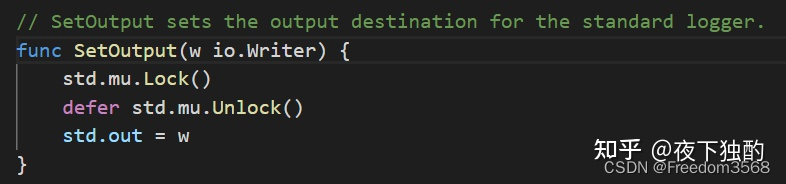

Go: Лесоруб-лесоруб на колесах Введение

Основы серверной разработки: технология кэширования, которую должен освоить каждый программист

Java Advanced Collections TreeSet: что это такое и зачем его использовать?

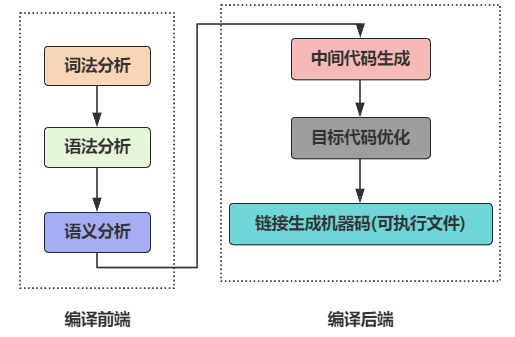

Оказывается, у команды go build столько знаний

Node.js

Анализ исходного кода, связанный с запланированными задачами версии ruoyi-vue (7), то есть анализ модуля ruoyi-quartz.

Вход в систему с помощью скан-кода WeChat (1) — объяснение процесса входа в систему со скан-кодом, получение авторизованного QR-кода для входа.

HikariPool-1 — обнаружено отсутствие потока или скачок тактовой частоты, а также конфигурация источника данных Hikari.

Сравнение высокопроизводительной библиотеки JSON Go

Простое руководство по извлечению аудио с помощью FFmpeg

Подсчитайте количество строк кода в проекте

Spring Boot элегантно реализует многопользовательскую архитектуру: концепции и практика

Как интегрировать функцию оповещения корпоративного WeChat в систему планирования xxl-job

SpringBoot интегрирует отправку сообщений через веб-сокет в режиме реального времени

Краткий анализ основных библиотек журналов в Go: узнайте, как интегрировать функции вращения и резки бревен на уровне проектирования.

Реализация API-шлюза с нуля-Golang

[Разговорный сайт] Как Springboot получает значения свойств из файлов конфигурации yml или свойств

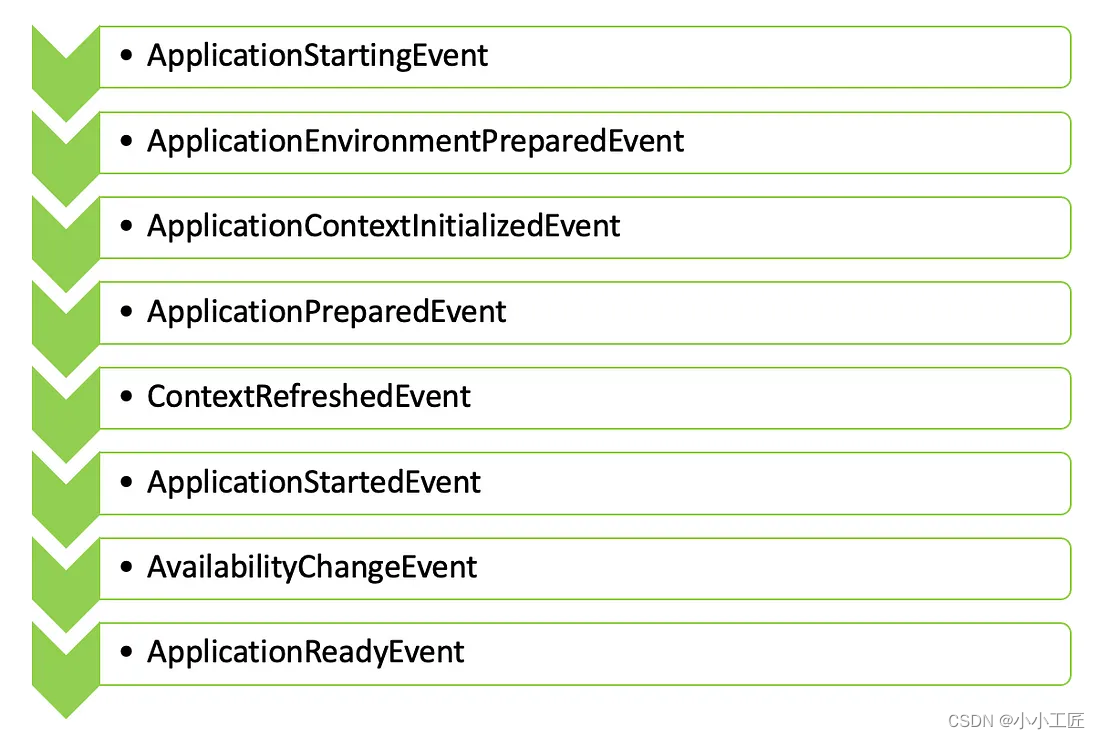

Spring Boot — синхронные события приложения против асинхронных событий публикации и подписки. Практический бой

Spring Boot использует Swagger3 для создания документов интерфейса API.

[1269] Использование Gunicorn для развертывания проектов flask.

Краткое изложение 10 способов регистрации bean-компонентов в SpringBoot

Flask Learning-9. 2 способа включения режима отладки (debug mode).

Руководство по настройке самостоятельного сервера для Eudemons Parlu

40 вопросов для собеседований по SpringBoot, которые необходимо задавать на собеседованиях! При необходимости ответьте на вопросы для собеседования SpringBoot [предлагаемый сборник] [легко понять]

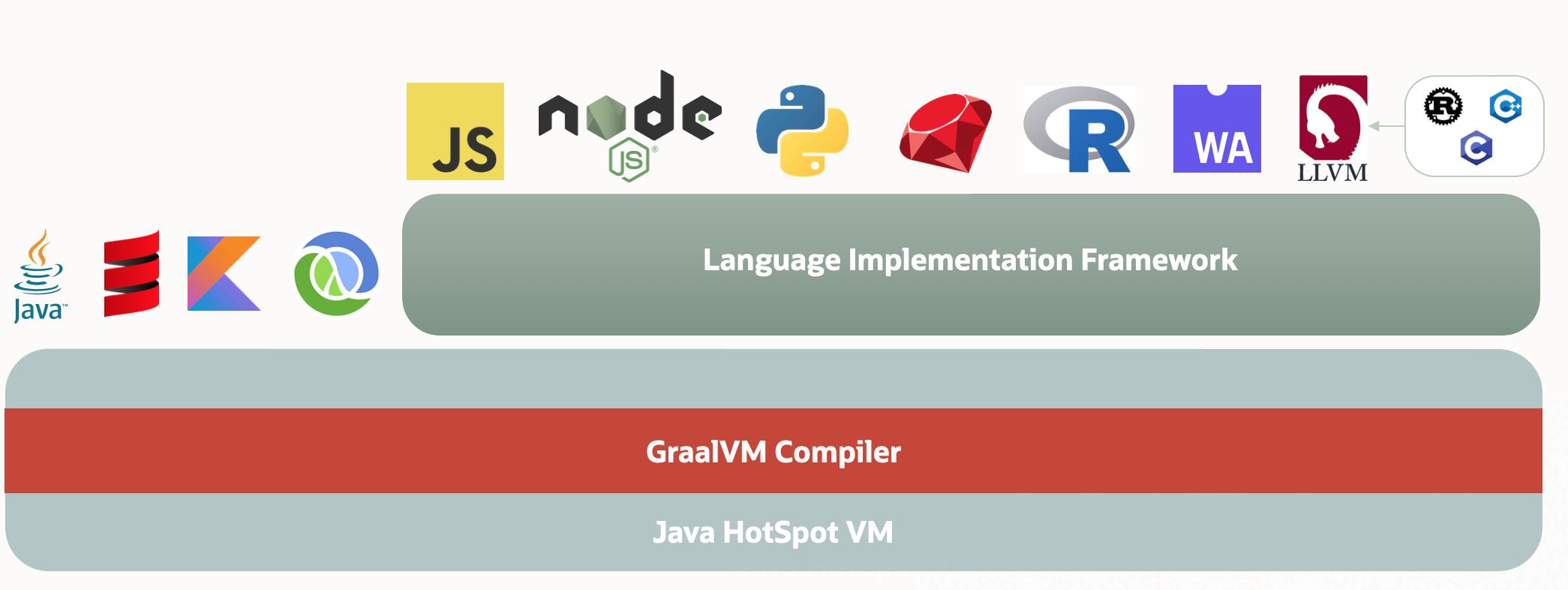

Через два года JVM может быть заменен GraalVM.