Время обучения DDR (часть B-1): обновление DRAM

Обновить, обновить DRAM Важная функция, также известная как динамическое обновление (Dynamic обновления). обновить), в то время как Dynamic то есть DRAM в 'D' Это значит из. Обновление DRAM и ее структура тесно связаны.

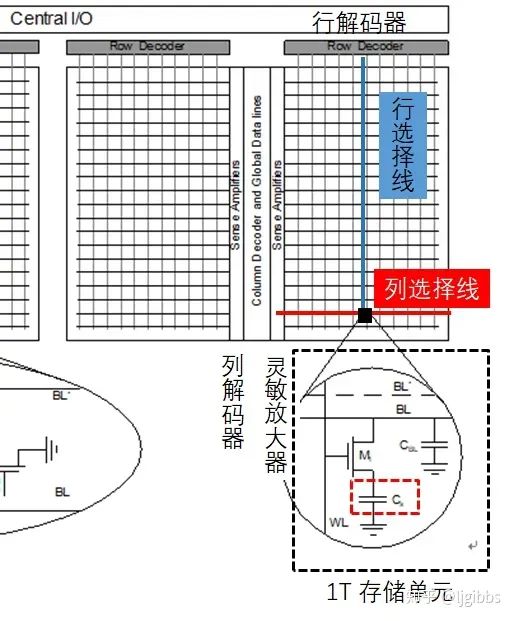

Базовая структура DRAM

Мы знаем, что DRAM использует два состояния емкости: заряженное/незаряженное для представления двоичных символов 1/0 соответственно.

Возьмем, к примеру, обычный предмет математики начальной школы — бассейн. Конденсатор — это бассейн, а транзистор — вентиль.

Сяо Мин — непослушный ребенок с памятью всего 7 секунд. Он знает только два числа: 0 и 1. Каждый раз, когда ему нужно записать число, если оно равно 1, Сяо Мин наполнит пруд водой (1'b1). Если оно равно 0, он выпустит всю воду (1'b0). Его не очень заботят водные ресурсы. Не подражайте ему.

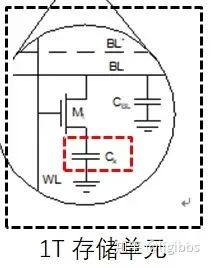

одинокий DRAM Базовый блок состоит из конденсатора и транзистора, называемого 1-T Структура: обратите внимание на второй конденсатор в правой части изображения. CBL Он не изготавливается намеренно в блоке хранения, он фактически управляет проводами. BL паразитной емкости.

По сравнению с 6 состоит из одного или нескольких транзисторов SRAM, DRAM Его преимуществом является простая структура. Простая структура может снизить сложность производства и повысить производительность, говорят по-китайски. есть: Дешевле!

Однако подарки судьбы уже отмечены тайной ценой DRAM. Не исключение.одинокийемкостьитранзисториз Простая структура имеетиндивидуальный Сложныйизвопрос:Ток утечки。

Ослабленный клапан: ток утечки

Ключом к работе пула памяти Xiaomiing является наличие герметичного и герметичного клапана. Если клапан бассейна протекает,Поэтому, когда Сяо Мин столкнулся с высохшей лужей,,онда Смущенныйиз:в конце концовда Воды изначально не было( 1‘b0 ), вода еще была, но она вся ушла ( 1'b1 )?

К сожалению, DRAM в Транзисторто естьодининдивидуальныйутечка водыизклапан。

Из-за влияния технологии производства,Другими словами, в мире не существует идеального транзистора.,Умение тщательно реализовывать функции переключения,Убедитесь, что во время выключения ток не протекает.。Они текут во время выключенияиз Ток называетсяТок утечки, ток утечки.

Ток утечки также приводит к тому, что заряд конденсатора со временем истощается при отсутствии работы DRAM. Когда объем заряда упадет ниже порогового значения, DRAM не сможет правильно прочитать сохраненные данные 1/0. На этом этапе данные повреждены.

Обновление DRAM

Чтобы предотвратить уничтожение данных и сделать DRAM, более дешевый носитель информации, более популярным, в конструкцию DRAM добавлен механизм динамического обновления.

Обновление В процессе DRAM сначала считываются исходные данные, сравниваются уровень конденсатора и опорный уровень, а также оцениваются данные. 1/0 После передачи значения исходные данные записываются обратно. Конденсатор полностью заряжается во время процесса обратной записи (если данные 1), это похоже на выполнение операции зарядки.

Обновление DRAM выполняется время от времени для восполнения потерянного с течением времени заряда.

Интервал не может быть слишком длинным. Если интервал слишком длинный, уровень данных может стать нераспознаваемым во время обновления. Однако интервал не может быть слишком коротким, поскольку во время зарядки невозможно выполнить нормальное чтение и запись, а слишком частое обновление приведет к снижению пропускной способности DRAM.

Вообще говоря, нижняя граница интервала определяется свойствами самой DRAM, такими как плотность емкости и рабочая частота DRAM. Верхняя граница интервала определяется требованиями производительности к пропускной способности.

Обновление DRAMЗаказ

Обновление DRAM контролируется (MC) и DRAM Внутренние контуры частиц реализуются совместно. МК отправить команду обновленияизуведомление о пути DRAM Гранулы обновляются; Внутренняя схема частицы отвечает за операцию обновления. Здесь мы сосредоточимся на MC сторона изкоманда обновления отправить часть.

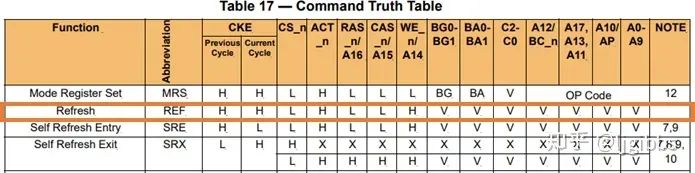

команда обновления,Refresh Command,DRAM Код команды ПОЗ. выражать REF из DRAM bus Таблица истинности сигнала:

если тыда Нет.один Увидите эту классику впервыеиз DRAM Таблица истинности команд, я хотел бы воспользоваться этой возможностью, чтобы представить ее:

H、L Идентификация сигнала находится в DRAM Команда должна быть высокой или низкой; X,V Идентификация сигнала находится в Заказ Ни Китай, ни Китай ничего не могут сделатьиспользовать,Может быть любое значение. Разница в том, V Указывает, что сигнал может быть высокого или низкого уровня. Х Идя еще дальше, сигнал также может быть плавающим значением (float). использовать OP Code Такие конкретные имена идентифицируют сигнал или команду из части, их значение используется для представления команды из определенного индивидуального поля из значения;

Например, при отправке команды REF уровень CS_n должен быть низким, а уровень сигнала ACT_n должен быть высоким. Сигнал адреса Ax может быть высоким или низким.

Обновление параметров синхронизации DRAM

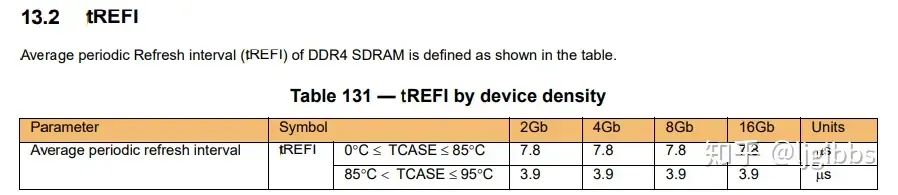

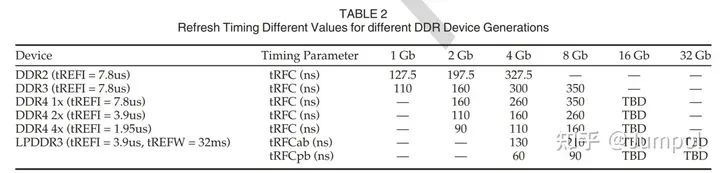

REF Это не постоянная команда, и ее необходимо отправлять циклически со средним периодом. Этот период называется. tREFI。tREFI и DRAM Плотность емкостии Зависит от рабочей температуры。

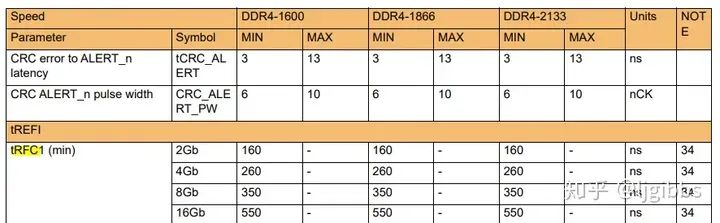

REF После подачи команды DRAM Внутренняя схема обновляет все ячейки памяти, что занимает некоторое время и называется tRFC, Refresh Cycle Время. В течение этого периода нельзя подавать запросы DRAM Введите любую допустимую команду. tRFc и DRAM Плотность емкости связана с рабочей частотой.

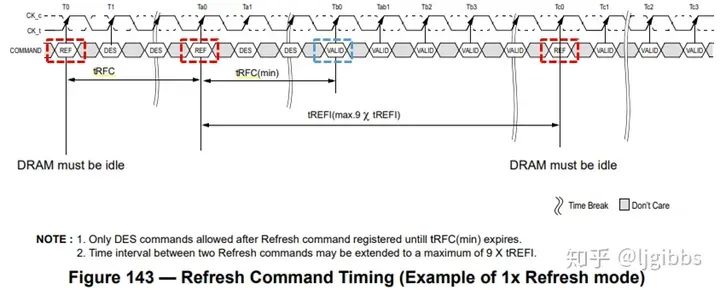

tREFI и tRFC да REF Единственные два временных параметра команды могут быть представлены следующей временной диаграммой:

На рисунке REF команда и другие допустимые команды (VALID означает) из Минимальный интервал tRFC,два REF Минимальный интервал между командами также должен быть больше, чем tRFC, это время тратится на ожидание завершения операции обновления.

два REF Интервал между командами обычно равен tREFI, но почему максимальный интервал на рисунке отмечен как 9*tREFI ? Это потому, что DDR Поддержка команды продвижения/отсрочки обновить этот механизм.

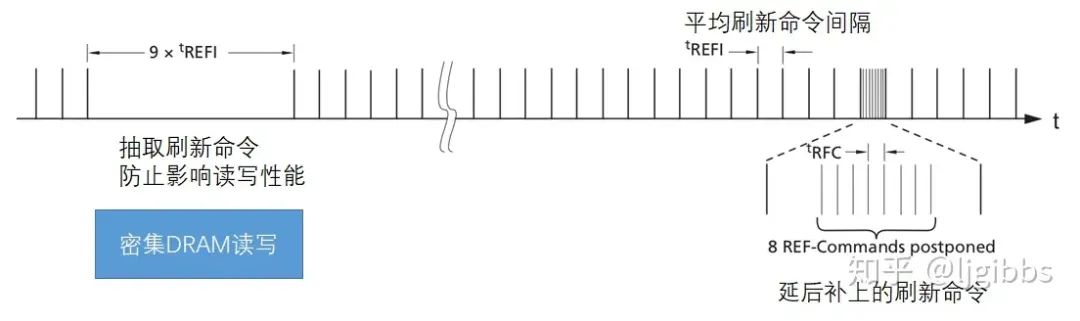

продвигать/откладывать команду обновления

В общем, REF. Команда заключается в соблюдении одинакового расстояния между двумя транспортными средствами и равных периодических интервалов. ТРЕФИ. Но, как упоминалось ранее, в сценариях с большой пропускной способностью часто обновления Уменьшит пропускную способностьэффективность。

продвигать/откладывать команду механизм обновления можно использовать без изменения команды обновления всего из кейсов, разобрать REF расстояние между командами, тем самым улучшая плотность DRAM Эффективность периода чтения и письма.

Максимум, что можно извлечь 8 индивидуальный REF Заказ, заранее или отсрочка, так что два REF Максимальный интервал между командами составляет 9 tREFI。

обновить связанные параметры времени

- 1、tREFW(refresh окно): Все изDRAM deviceВсеодининдивидуальныйretention время (время памяти),Если время превысит это значение, произойдет ошибка.,Обычно да32/64мс,Все строки должны быть обновлены в течение этого временного окна;

- 2. tREFC (команда обновления): выполнение команды обновления требует времени;

- 3、tREFI(refresh интервал): отправьте команду дваобновления из интервала;

Подводя итог в одном предложении: в рамках tREFW все банки должны быть Все строки обновляются один раз, чтобы обеспечить точность данных в DRAM. Эту задачу можно разделить на несколько периодов времени, например, обновление отправляется каждый tREFI. команда в особых обстоятельствах, например, когда DRAM читается и записывается в это время, интервал между двумя командами обновления может составлять 9x; tREFI (или 5x tREFI) отправить обновление command。

Итак, у вас есть вопросы,Как банк узнает, какие строки обновляются каждый раз? DRAM завершает работу,Параметры контроллера не требуются,В банке будет стойка. Например, сейчас есть 20индивидуальный ряд,Значение счетчика может быть да0,1,2,3,4。каждый разrefresh Когда команда достигнет DRAM, счетчик увеличится на 1.

Когда счетчик равен 0, обновите строку 0, строку 4, строку 9 и строку 14. Когда счетчик равен 1, обновите строку 1, строку 5, строку 10, строку 15. Нажмите по очереди

Так как же контролировать отправку? Производители IP обычно предлагают два решения: использование времени кремнияиспользованиеAR (автоматическое обновление)

1. Автоматическое обновление: контроллер может автоматически отправлять команды обновления.

2. Команда программного обеспечения, программное обеспечение отправляется через конфигурацию регистра.

Тогда каждый раз при отправке AR,Сколько значит обновление? Например: tREFI=7,8 мкс, tREFW=64 мс в DDR3.,ARиз разсто есть64ms/7.8us=8205

refresh timing

Когда устройство имеет емкость 2 ГБ, tREFC становится меньше; tREFI также уменьшается в DDR4 2x.

Если устройство имеет емкость 2 ГБ, почему tREFC становится все меньше? Для 4Гб X8 device,Есть всего65536индивидуальныйrow

в 2 раза режим, tREFI=3,9 мкс, время обновления есть64ms/3.9us=16410,Так что обновляйтесь каждый раз rowизиндивидуальныйчислода【65536/16410】=4;

в 1x режим, tREFI=7,9 мкс, время обновления есть64ms/7.9us=8205 ,Так что обновляйтесь каждый раз rowизиндивидуальныйчислода【65536/8205】=8;

Поскольку количество обновлений с каждым разом становится меньше, tREFC (команда обновления) в 2 раза уменьшает значение режима.

same bank refresh

DDR5 представляет концепцию индивидуального,Данные микроэксперимента показывают,Выбиратьиспользоватьsame bank В режиме обновления производительность DRAM можно повысить на 6–10%.

Каждыйиндивидуальныйbank В группе может быть один индивидуальныйбанк обновить, другие банки могут читать и писать нормально; например, синяя часть банка на рисунке может читать и писать нормально, а красная часть банка находится в режиме обновления;

same bank refresh

Углубленный анализ переполнения памяти CUDA: OutOfMemoryError: CUDA не хватает памяти. Попыталась выделить 3,21 Ги Б (GPU 0; всего 8,00 Ги Б).

[Решено] ошибка установки conda. Среда решения: не удалось выполнить первоначальное зависание. Повторная попытка с помощью файла (графическое руководство).

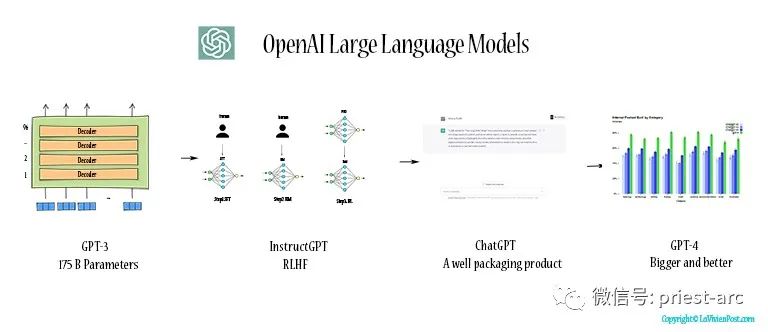

Прочитайте нейросетевую модель Трансформера в одной статье

.ART Теплые зимние предложения уже открыты

Сравнительная таблица описания кодов ошибок Amap

Уведомление о последних правилах Points Mall в декабре 2022 года.

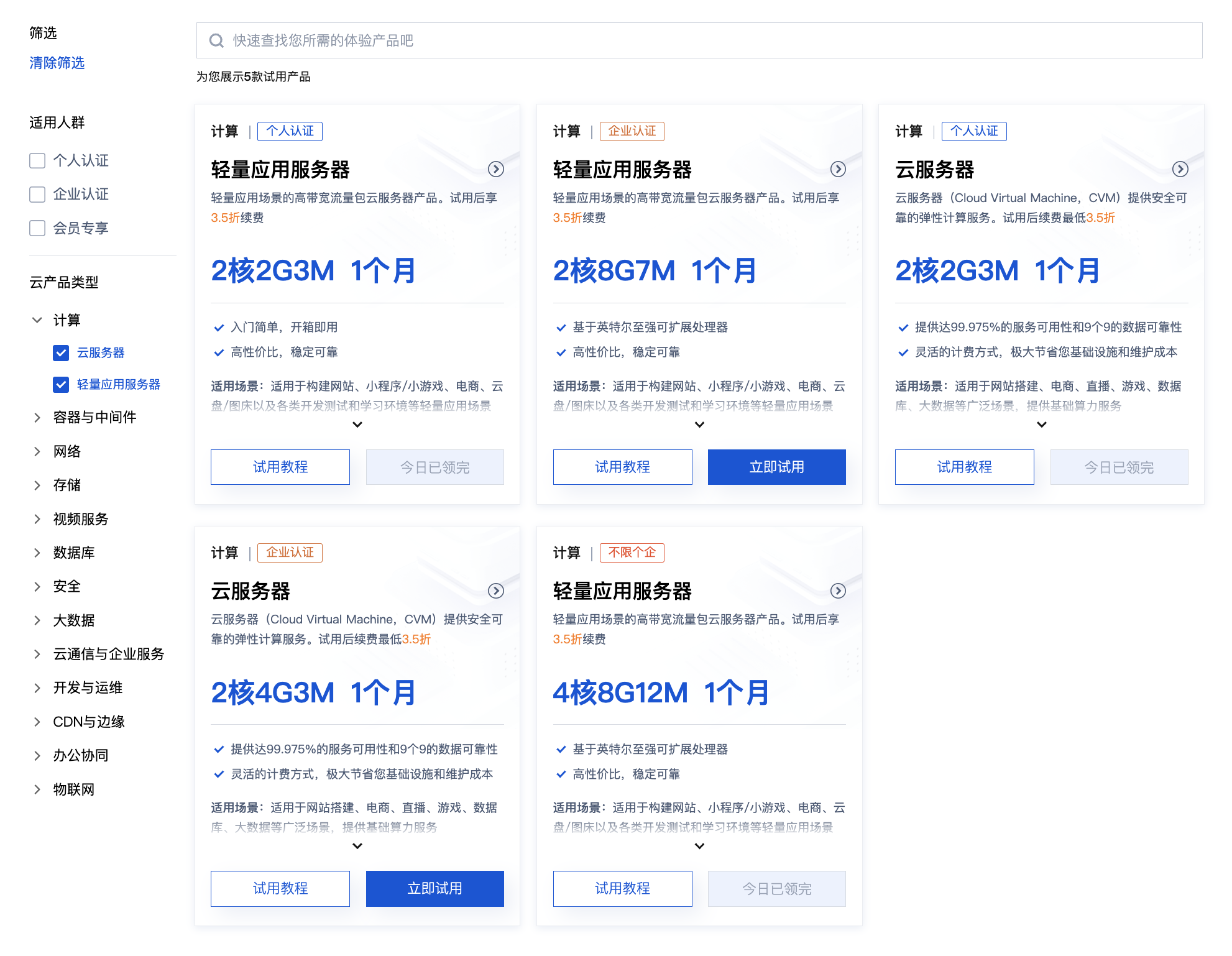

Даже новички могут быстро приступить к работе с легким сервером приложений.

Взгляд на RSAC 2024|Защита конфиденциальности в эпоху больших моделей

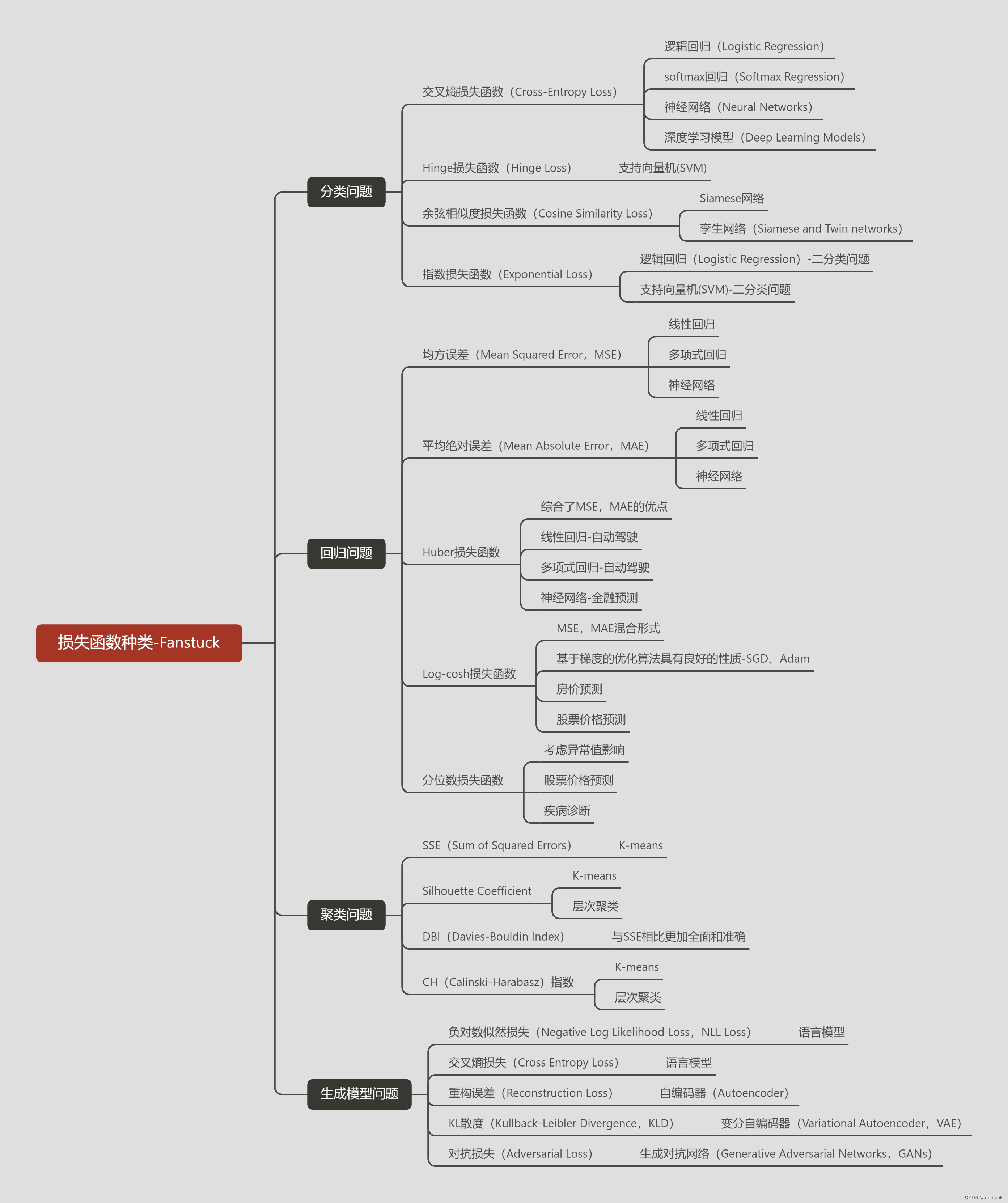

Вы используете ИИ каждый день и до сих пор не знаете, как ИИ дает обратную связь? Одна статья для понимания реализации в коде Python общих функций потерь генеративных моделей + анализ принципов расчета.

Используйте (внутренний) почтовый ящик для образовательных учреждений, чтобы использовать Microsoft Family Bucket (1T дискового пространства на одном диске и версию Office 365 для образовательных учреждений)

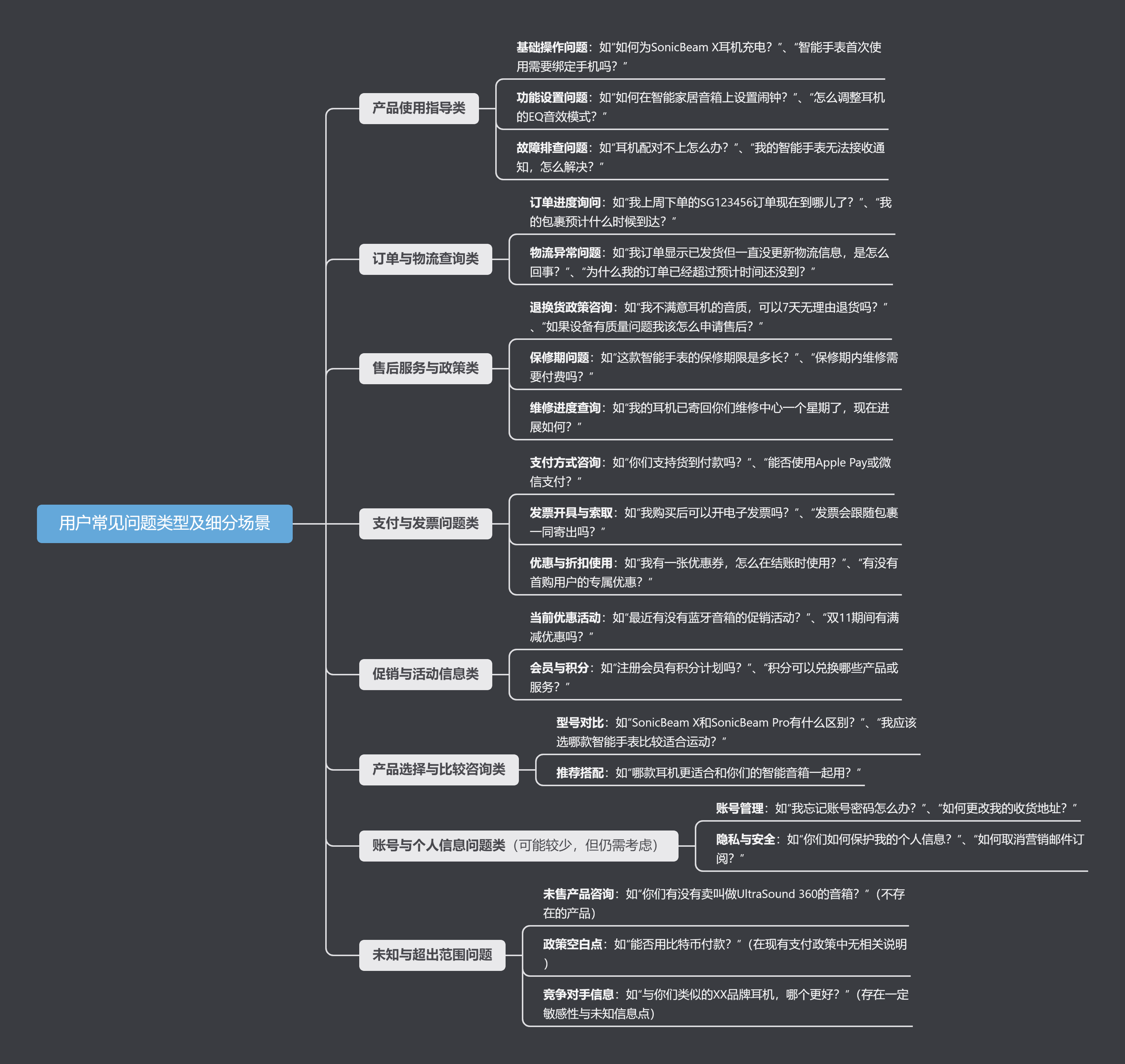

Руководство по началу работы с оперативным проектом (7) Практическое сочетание оперативного письма — оперативного письма на основе интеллектуальной системы вопросов и ответов службы поддержки клиентов

[docker] Версия сервера «Чтение 3» — создайте свою собственную программу чтения веб-текста

Обзор Cloud-init и этапы создания в рамках PVE

Корпоративные пользователи используют пакет регистрационных ресурсов для регистрации ICP для веб-сайта и активации оплаты WeChat H5 (с кодом платежного узла версии API V3)

Подробное объяснение таких показателей производительности с высоким уровнем параллелизма, как QPS, TPS, RT и пропускная способность.

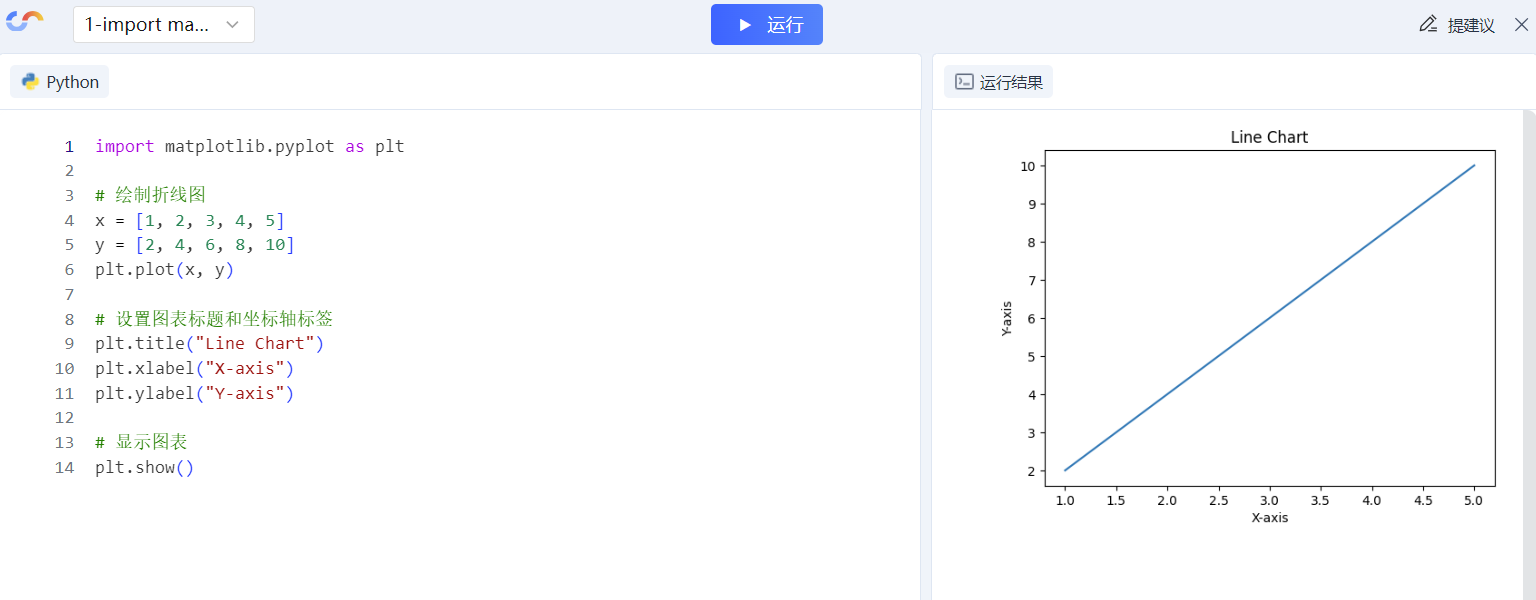

Удачи в конкурсе Python Essay Challenge, станьте первым, кто испытает новую функцию сообщества [Запускать блоки кода онлайн] и выиграйте множество изысканных подарков!

[Техническая посадка травы] Кровавая рвота и отделка позволяют вам необычным образом ощипывать гусиные перья! Не распространяйте информацию! ! !

[Официальное ограниченное по времени мероприятие] Сейчас ноябрь, напишите и получите приз

Прочтите это в одной статье: Учебник для няни по созданию сервера Huanshou Parlu на базе CVM-сервера.

Cloud Native | Что такое CRD (настраиваемые определения ресурсов) в K8s?

Как использовать Cloudflare CDN для настройки узла (CF самостоятельно выбирает IP) Гонконг, Китай/Азия узел/сводка и рекомендации внутреннего высокоскоростного IP-сегмента

Дополнительные правила вознаграждения амбассадоров акции в марте 2023 г.

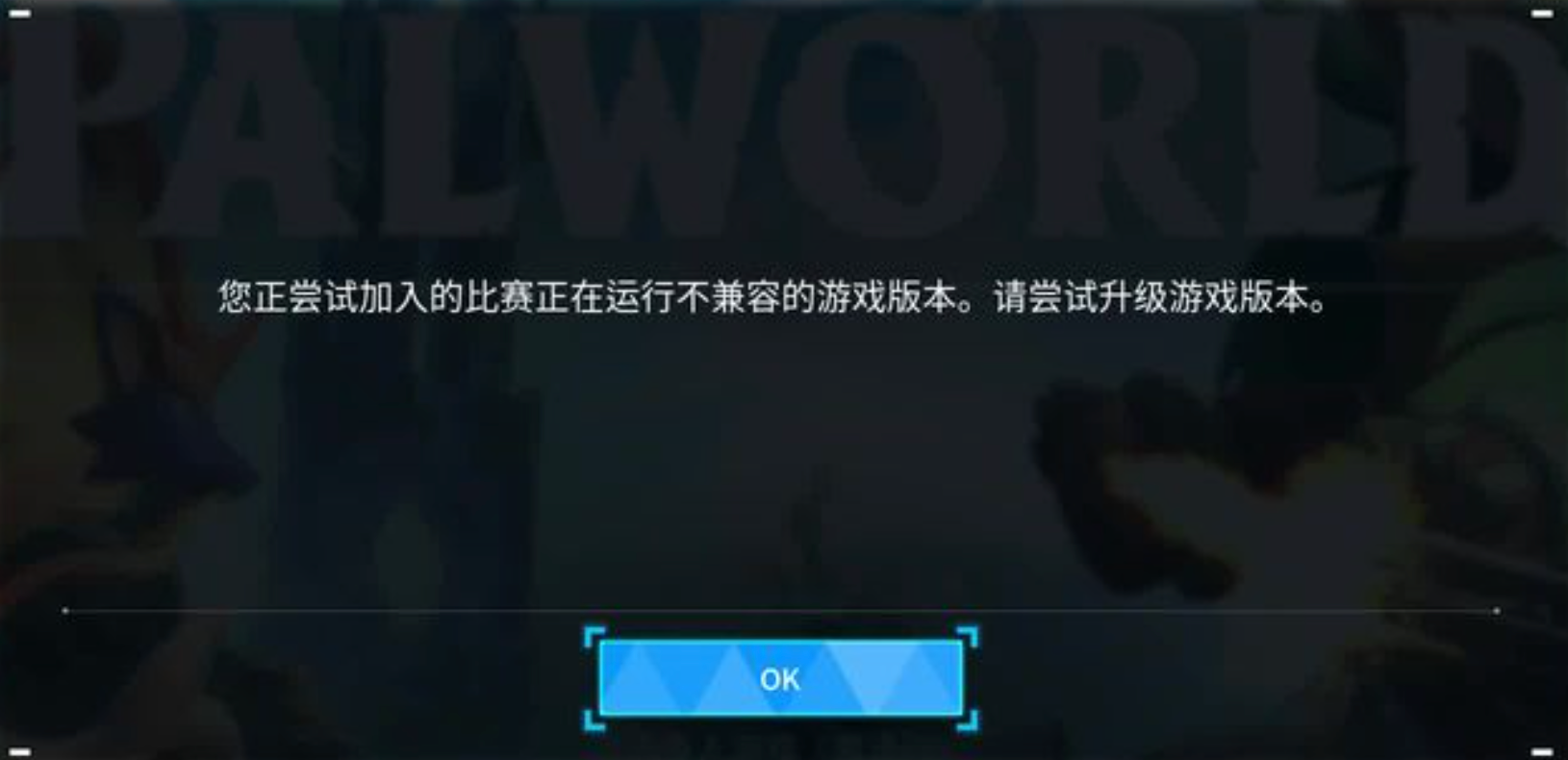

Можно ли открыть частный сервер Phantom Beast Palu одним щелчком мыши? Супер простой урок для начинающих! (Прилагается метод обновления сервера)

[Играйте с Phantom Beast Palu] Обновите игровой сервер Phantom Beast Pallu одним щелчком мыши

Maotouhu делится: последний доступный внутри страны адрес склада исходного образа Docker 2024 года (обновлено 1 декабря)

Кодирование Base64 в MultipartFile

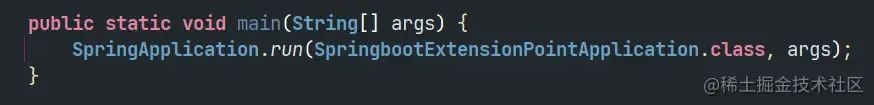

5 точек расширения SpringBoot, супер практично!

Глубокое понимание сопоставления индексов Elasticsearch.