Углубленный анализ: Знание основных понятий и принципов кэширования.

Ключевые слова дренажа: кеш, кеш, кеш, CCI, CMN, CCI-550, CCI-500, DSU, SCU, L1, L2, L3, системный кеш, некэшируемый, кешируемый, неразделяемый, внутренний-разделяемый, внешний- общий, optee, ATF, TF-A, Trustzone, optee3.14, MMU, VMSA, кэш, TLB, Arm, Armv8, Armv9, TEE, безопасность, управление памятью, таблица страниц...

Эта статья перепечатана Чжоу Хехе, бароном, код меняет мир, выбор оружия, Armv8/armv9, зона доверия/tee, SecureBoot, старший эксперт по архитектуре безопасности, 11 лет опыта в области мобильной безопасности/разработки базовой безопасности SOC. Хорошо разбирается в проектировании и разработке продуктов безопасности доверенных зон и тройников.

1. Кэш многоуровневый.

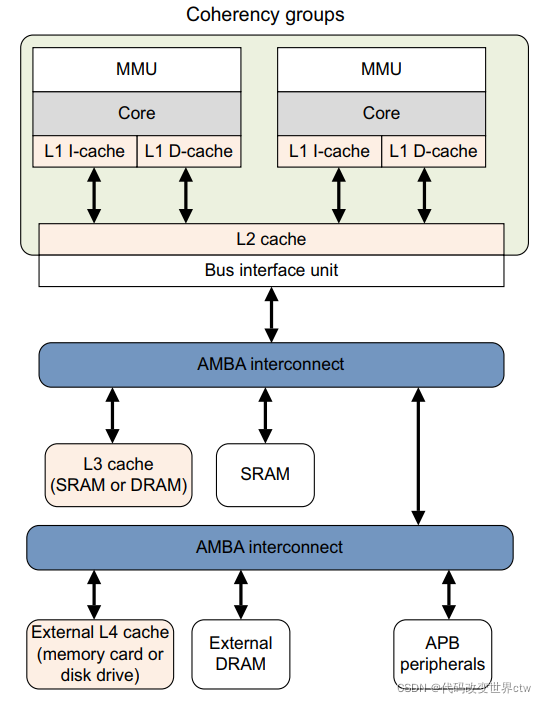

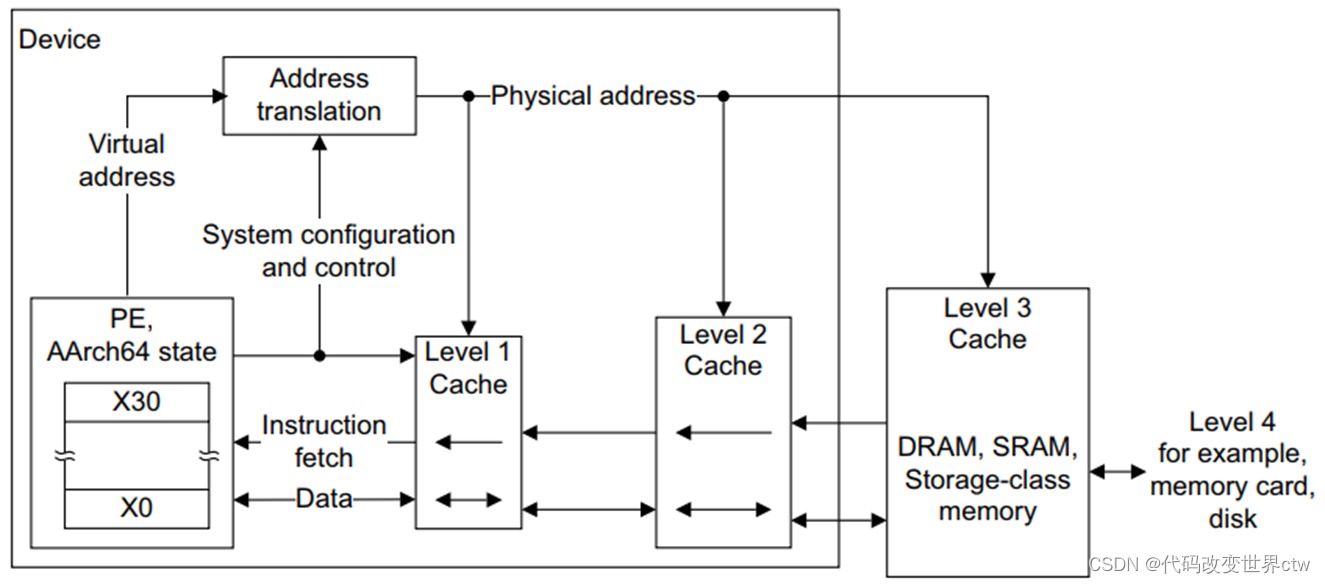

Кэш многоуровневый. В системе могут быть L1, L2 и L3. Конечно, чем ближе к ядру, тем меньше кэш и тем он дороже. Вообще говоря, для архитектуры big.LITTLE L1 находится в ядре, L1 разделен на кеш данных L1 и кеш инструкций L1, кеш L2 находится в кластере, а L3 находится на шине BUS.

2. Кэш обычно используется совместно с MMU.

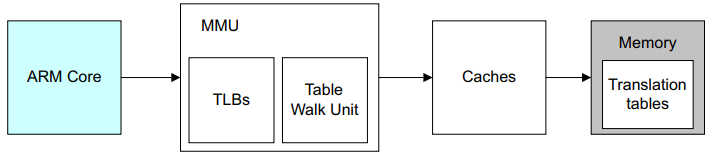

Во многих случаях кеш используется вместе с MMU (то есть он включается или выключается одновременно), поскольку атрибуты записи таблицы страниц MMU управляют разрешениями на память, стратегиями кэширования кэша и т. д.

В архитектуре ARM кэш L1 является VIPT, то есть, когда виртуальный адрес отправляется и MMU начинает выполнять преобразование адресов, виртуальный индекс можно запросить в запросе кеш-памяти L1 и запросе индекса кэша L1. Готово. в то же время. Если L1 пропущен, L2 будет запрошен снова. Если L2 не найден, L3 будет запрошен снова. Обратите внимание, что в архитектуре Arm только кэш L1 является VIPT, а L1L2 и L3 — PIPT.

3. Базовое введение в аппаратную архитектуру

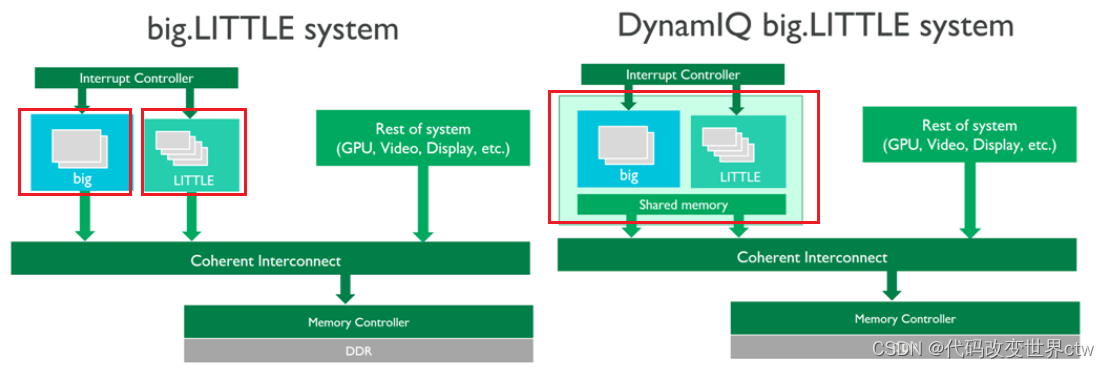

big.LITTLE Архитектура и DynamIQ Архитектура Кэш другой

- существовать

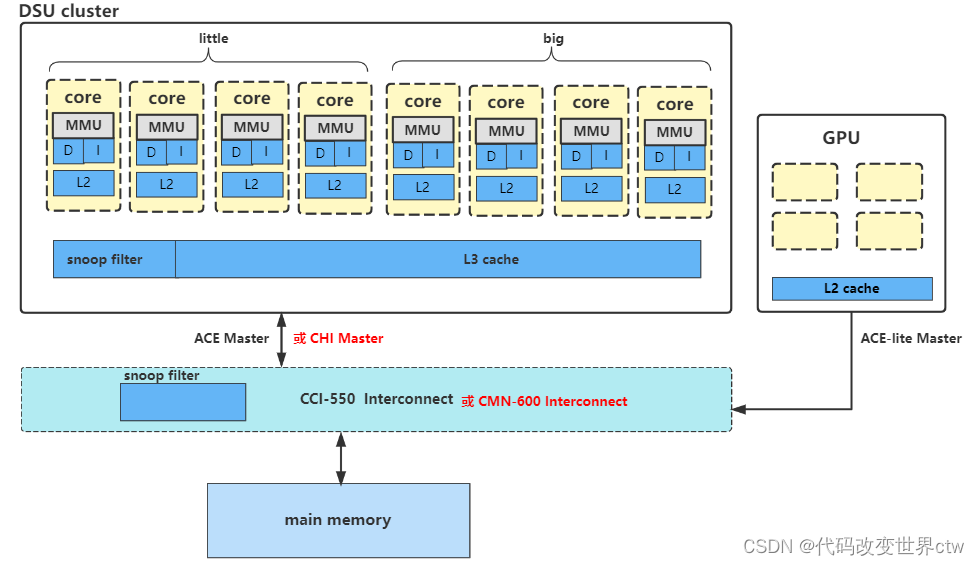

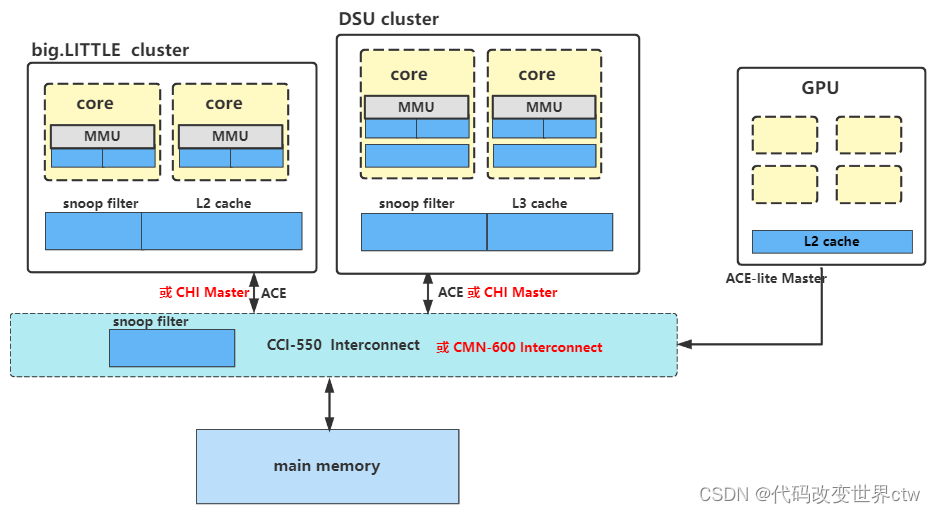

big.LITTLEВ Архитектуре большое ядро и малое ядро существуют в разных кластерах, как два разных ACE или CHI. Master,Подключен к шине согласованности кэша (CCI или CMN). Согласованность большого основного кластера и малого основного кластера,Эту проблему также необходимо решить с помощью шины согласованности. - Прибыл в DynamIQ В Архитектуре и большое ядро, и маленькое ядро представляют собой DSU. В кластере DSU Кластер может поддерживать до 8 ядер. Если в вашей системе 8 ядер, то достаточно одного DSU, и тогда в системе только один ACE или CHI. Мастер, согласованность между большим ядром и малым ядром, как DSU Завершено внутри кластера.

3.1 Кэш архитектуры big.LITTLE

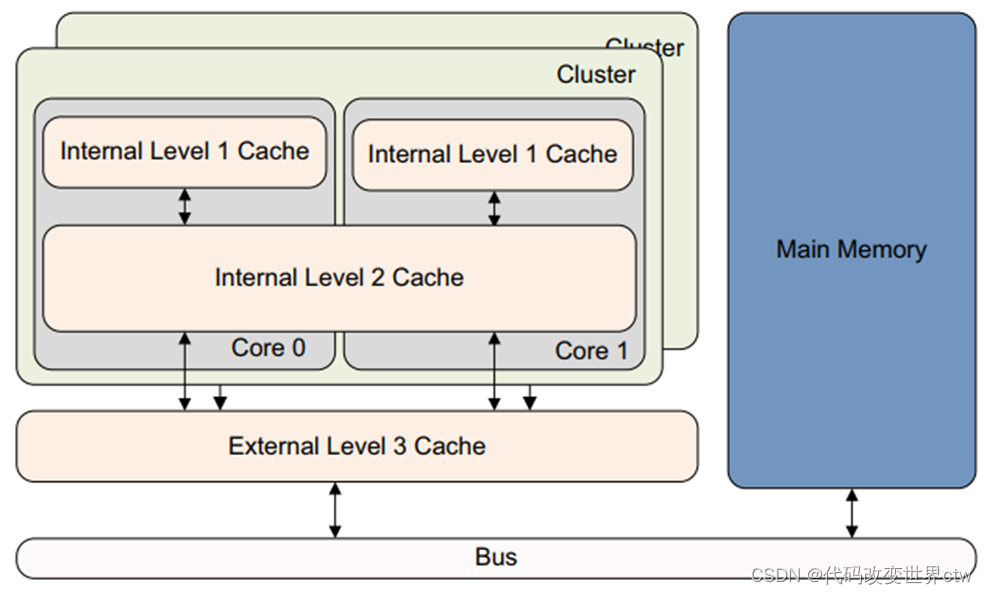

существовать big.LITTLE из Архитектурасередина,L1 находится в существующем ядре,Он является частным для ядра; L2 находится в существующем кластере.,верноclusterвcoreявляется общим;L3новерновсеclusterобщий。big.LITTLE Схема иерархии кэша Архитектуры выглядит следующим образом:

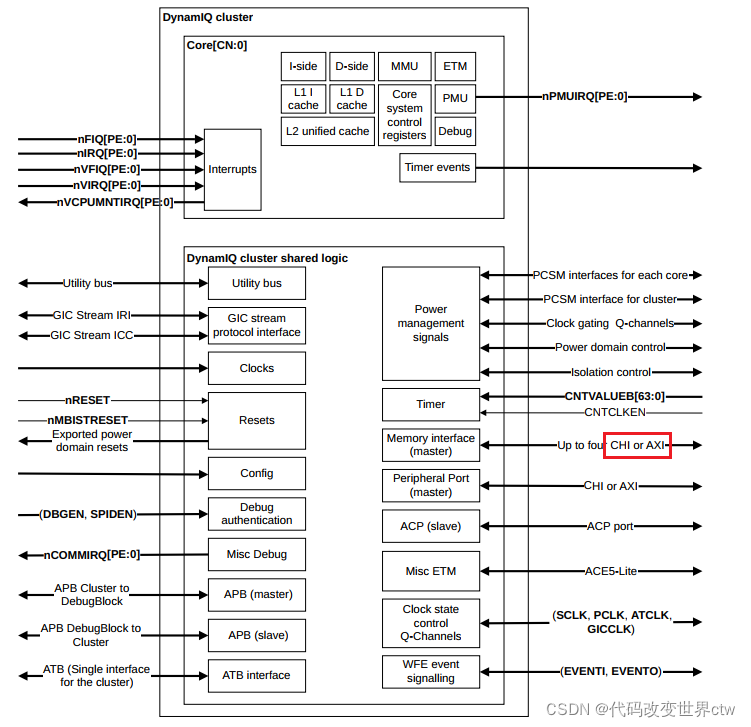

3.2 Кэш архитектуры DynamIQ

существовать dynamIQ В Архитектуре все L1 и L2 находятся в существующем ядре и являются частными для ядра; L3 находится в существующем кластере, а ядро в кластере является общим, если есть L3 или система; кэш является общим для всех кластеров. Диаграмма иерархии кэша Архитектуры dynamIQ показана ниже.

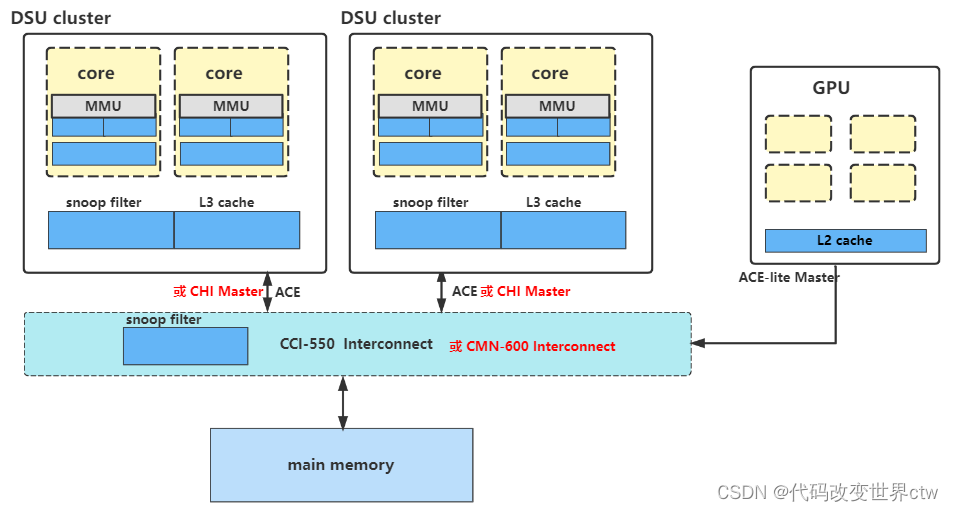

Обратите внимание, что, вообще говоря, DSU Кластер может поддерживать 8 ядер. Ниже приведен лишь крайний пример. При проектировании оборудования мне пришлось разместить два DSU. cluster Является ли это возможным? Два DSU Кластер как два ACE Мастер подключен к шине согласованности CCI.

3.3 Шина когерентности кэша-CCI

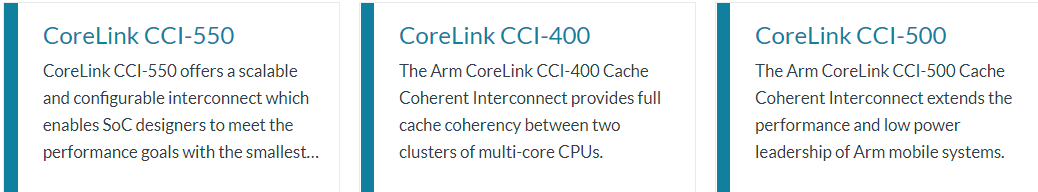

для АСЕ Шина когерентности главного кэша имеет CCI-550、CCI-500、CCI-400。

Его основная функция – соединение несколькихACE Master、ACE-lite Master,Затем через протокол интерфейса ACE,сделать несколькоMasterмеждукэшпоследовательность。CCIНаиболее поддерживаемые2индивидуальныйACE Master,Полная поддержка8индивидуальныйACE Master+ACE-lite Master。

Итак, если это big.LITTLE Архитектура, то она поддерживает до двух соединений. кластеров, каждый кластер 8 ядер, поэтому поддерживает до 8 ядер, если это Архитектура dynamIQ, она поддерживает до двух DSU; Соединение кластеров, каждый кластер 8 ядер, поэтому поддерживается до 16 ядер.

3.4 Шина когерентности кэша-CMN

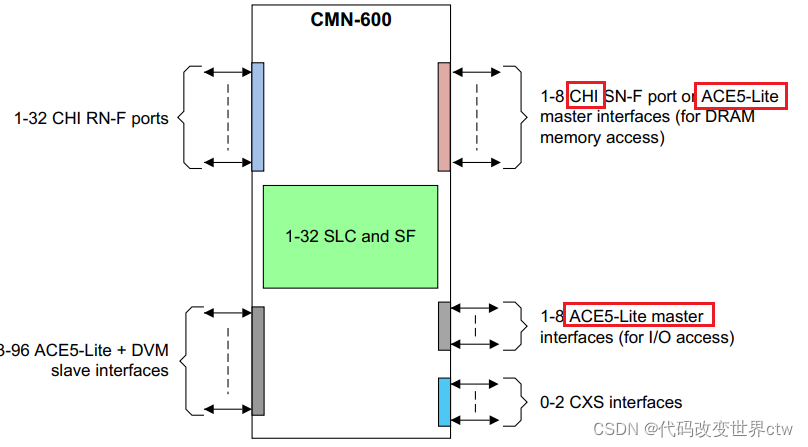

для ОМС Шина когерентности главного кэша имеетCMN-700、CMN-600.

Его основная функция – соединение несколькихCHI Master、ACE-lite Master,Затем через протокол интерфейса CHI,сделать несколькоMasterмеждукэшпоследовательность。CCI-600Наиболее поддерживаемые8индивидуальный CHI Master ,Полная поддержка8индивидуальныйCHI Master + ACE-lite Master。

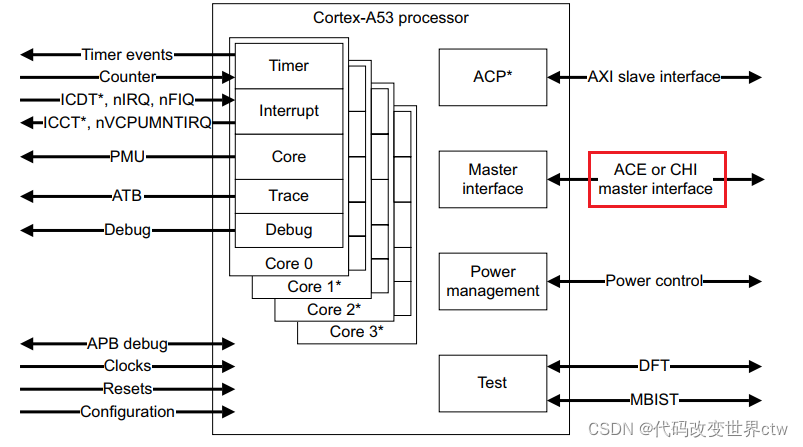

Кластерный интерфейс 3.5 в архитектуре big.LITTLE

существоватьbig.LITTLEАрхитектурасередина,Интерфейс, который кластер подключает к шине согласованности.,Может быть АСЕ,Это также может быть ЧИ,Такой большой.МАЛЕНЬКИЙ кластер можно использовать как ACE Мастер подключается к шине и может также использоваться как CHI. Мастер подключен к шине.

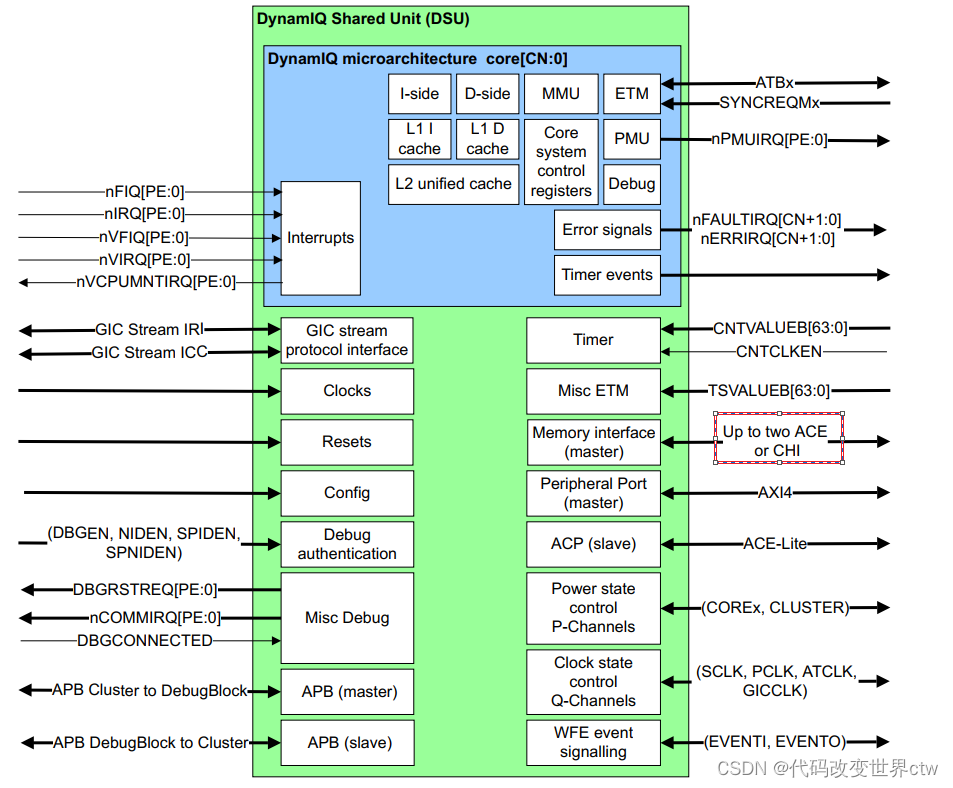

3.6 Интерфейс DSU в архитектуре dynamIQ

2017введено вdynamIQАрхитектура, существоватьDSU(dynamIQ Share Unit), интерфейс, подключенный к шине согласованности, может быть ACE или CHI, поэтому DSU кластер можно использовать как ACE Мастер подключается к шине и может также использоваться как CHI. Мастер подключен к шине.

исуществоватьDSU-110середина, Интерфейс, подключенный к шине согласованности, может быть CHI. , но больше нет ACE. Если вы используете DSU-110, DSU Кластер как ОМС Мастер, то вам необходимо использовать метод соединения шины CMN.

3.7 Пример схемы архитектуры

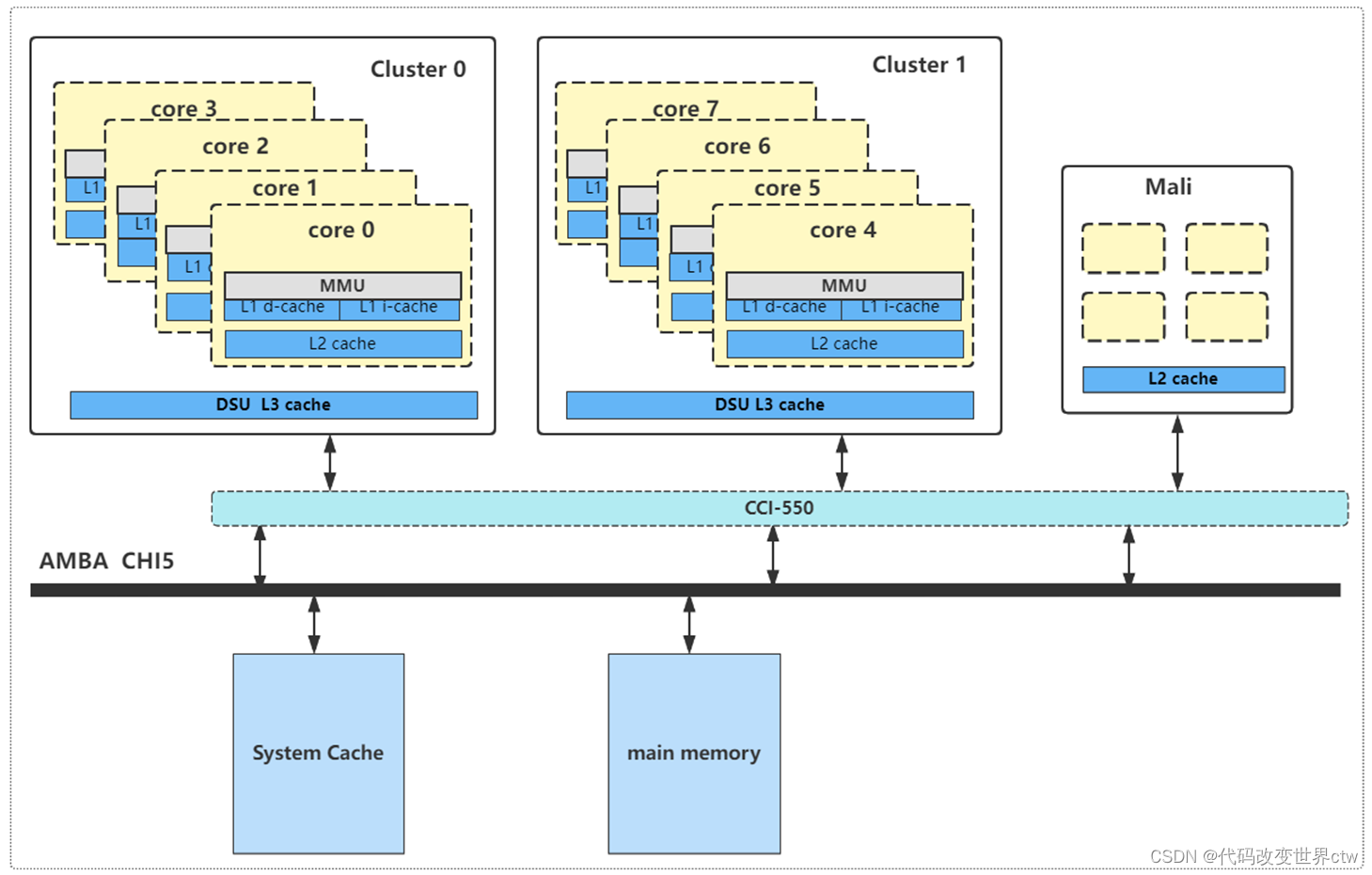

Ну и что,Схема системной архитектуры, которую вы видите (также наиболее часто используемая в последние годы),Это может выглядеть так,всеcoreВсесуществоватьодининдивидуальныйDSU В кластере все ядра используют общий уровень L3. кэша, DSU подключается к шине согласованности межсоединений CCI или CMNкэш и может использоваться с другими ACE-Lite. Мастер (например, GPU) данные общего кэша

Конечно, если привести немного крайний пример, то можно соединить приведенную ниже схему Архитектуры. В системе есть два DSU. кластере DSU подключен к шине согласованности межсетевого взаимодействия кэша CCI или CMN.

фактическиbig.LITTLEАрхитектураизcluster,Его также можно использовать как CHI. Владелец. Следующий ультраэкстремальный пример технически осуществим (разумеется, никто не сможет его использовать).

4. Размер кэша L1/L2/L3.

Вы можете обратиться к документации ARM,

- верно В

big.LITTLEАрхитектураизcore,Размер кэша в основном фиксирован. - верно В

dynamIQАрхитектураизcore,Это L1иL2 Размер кэша в основном фиксирован. Но для L2 cache Выбор Конфигурация не является обязательным.

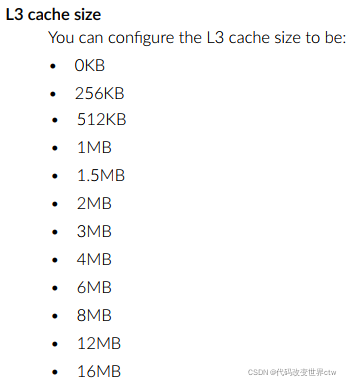

Также проверьте документацию DSU TRM, и вы увидите, что кэш L3 можно настроить с размером 0–16 МБ.

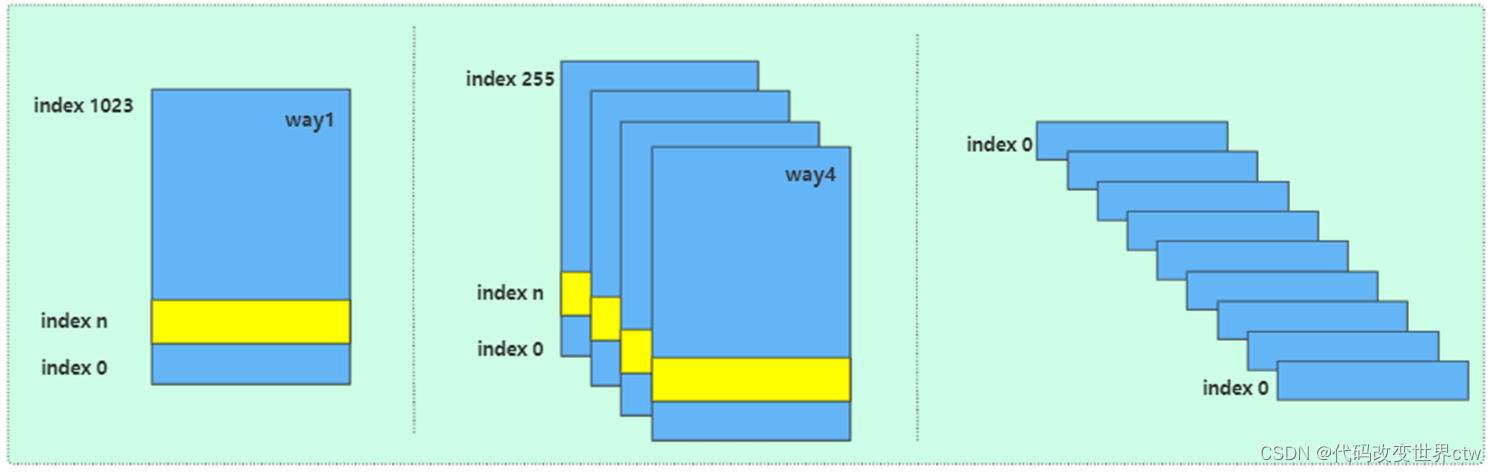

5. Форма организации кэша (индекс, путь, набор)

Организационными формами кэша являются:

- Полностью подключен

- напрямую подключен

- Многостороннее групповое соединение (например, 4-стороннее групповое соединение)

существуют В ядре, в Архитектуре, в SOC, организационная форма всех кэшей неодинакова. Даже если L1 D-cacheиL1 Организационная форма I-кэша может быть неодинаковой. специфическийиз Какова организационная форма?>Образециз,Нужно проверить ваше основное руководство по трм.

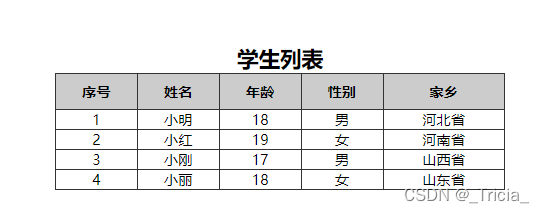

Например, мы запрашиваем информацию о кэше Cortex-A53 следующим образом: I-кэш L1

- Доступно: 8 КБ, 16 КБ, 32 КБ или 64 КБ.

- cacheline:64bytes

- 2-стороннее групповое соединение

- 128-битный интерфейс чтения памяти L2

L1 D-Cache

- Доступно: 8 КБ, 16 КБ, 32 КБ или 64 КБ.

- cacheline:64bytes

- 4-стороннее групповое соединение

- 256-битный интерфейс записи памяти L2

- 128-битный интерфейс чтения памяти L2

- 64-битное чтение L1 в канал данных

- Запишите 128-битный путь данных в L1.

L2 cache Настраиваемый: 128KB, 256KB, 512KB, 1MB and 2MB.

- cacheline:64bytes

- Физически индексированный и тегированный кеш (PIPT) -16-канальная групповая структура

Из-за многопоточного группового кэша существуют некоторые терминологические понятия:

- индекс: понимается на просторечии,По сути, это кусок тайника в существовании.,Построчный номер (на самом деле номера/адреса нет)

- Набор: может быть запрошено несколько строк кэша с использованием индекса. Эти строки кэша с одинаковым значением индекса называются набором.

- Путь: Говоря простым языком, кеш разделен на несколько блоков (многопоточный), и каждый блок представляет собой путь.

- ТЕГ кэша: после запроса строки кеша кэш состоит из ТЕГА + ДАННЫХ.

- Данные кэша: после запроса строки кэша кэш состоит из TAG + DATA.

- cache Line и entry это концепция

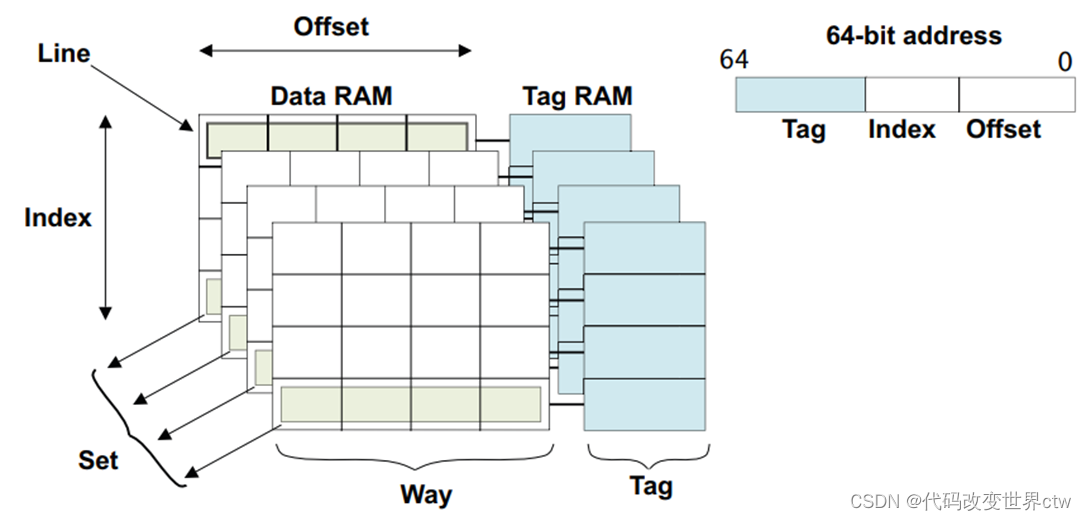

6. Типы кэша (VIVT, PIPT, VIPT)

Кэш обычно имеет следующие типы;

- PIPT

- VIVT

- VIPT существуют В ядре, в архитектуре, в SOC тип используемого вами кэша фиксирован и не может быть изменен программным обеспечением. существоватьARMАрхитектурасередина,Общий Л1 Кэши все VIPT, остальные PIPT. VIPTиPIPTизпринцип,В принципе они одинаковы,Есть лишь небольшая разница в аппаратном запросе.,существование будет введено снова, когда мы поговорим о запросе к кешу позже.

Итак, что еще вы узнаете о VIVT? Почему вам все еще нужно понимать принципы VIVT? Зачем еще нужно анализировать проблему одноимённых и повторяющихся названий тайников? 这Образецизвопрос,существоватьarmv7/armv8/armv9Архитектурасередина Всене существуетсуществоватьиз

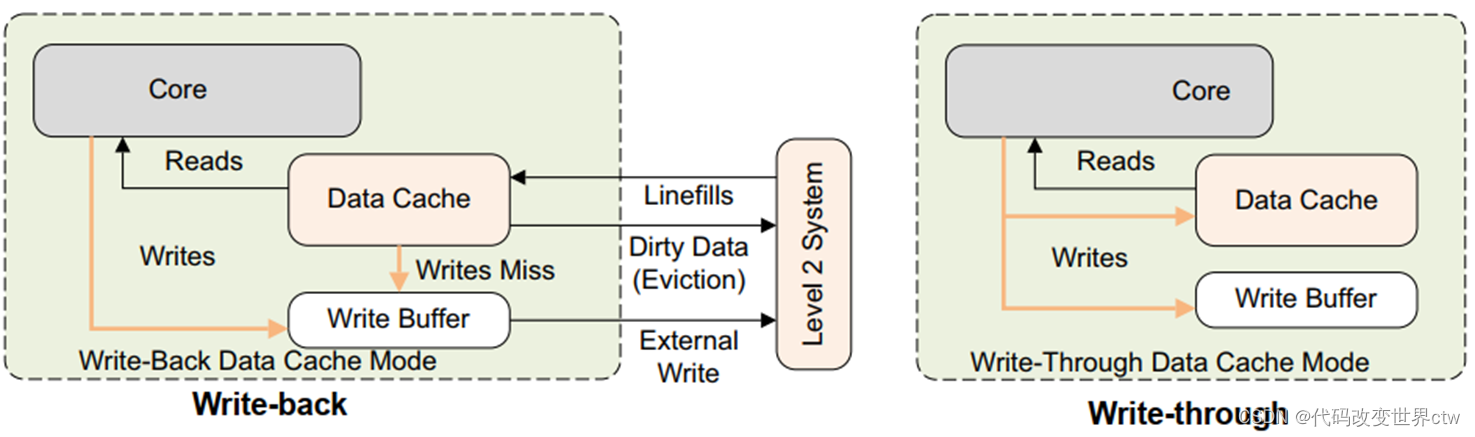

7. Стратегия распределения кэша (распределение, сквозная запись, обратная запись)

- чтение распределения Когда ЦП считывает данные, происходит промах кэша. В этом случае кэш будет выделен. линекэшданные, считываемые из основной памяти. По умолчанию кэши поддерживают распределение чтения.

- запись распределения Когда ЦП записывает данные и происходит промах кэша, будет рассмотрена стратегия распределения записи. Когда мы не поддерживаем распределение записи, инструкция записи будет только обновлять данные основной памяти, и на этом все закончится. Когда поддерживается распределение записи, мы сначала загружаем данные из основной памяти в кеш. (эквивалентно первому выполнению действия по чтению), а затем кеш будет обновлен lineвданные。

- писать через Когда ЦП выполняет инструкцию сохранения и попадает в кеш, мы обновляем данные в кеше и обновляем данные в основной памяти. Кэш и основная память всегда согласованы.

- напиши ответ Когда ЦП выполняет инструкцию сохранения и попадает в кэш, мы только обновляем данные в кэше. И каждый кэш В строке будет бит, указывающий, были ли изменены данные, который называется грязным. бит (посмотрите предыдущую картинку, кэш Рядом с линией стоит буква D, которая означает «грязный». кусочек). мы испачкаем бит установлен. данные в основной памяти будут существовать только в кэше Строка заменяется или обновляется при выполнении операции очистки дисплея. Следовательно, данные в основной памяти могут быть неизмененными данными, в то время как модифицированные данные находятся в существующем кэше. кэш и основная память могут быть противоречивыми

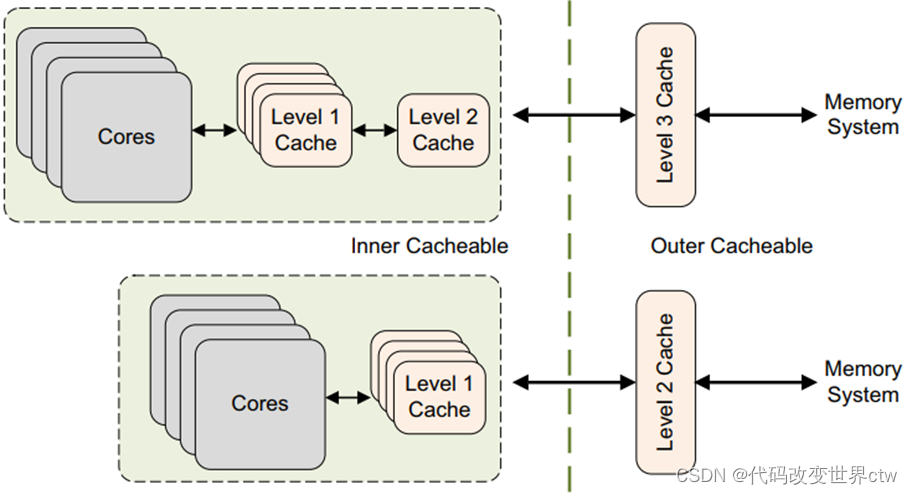

8. Объем кэша, определенный в архитектуре (внутренний, внешний)

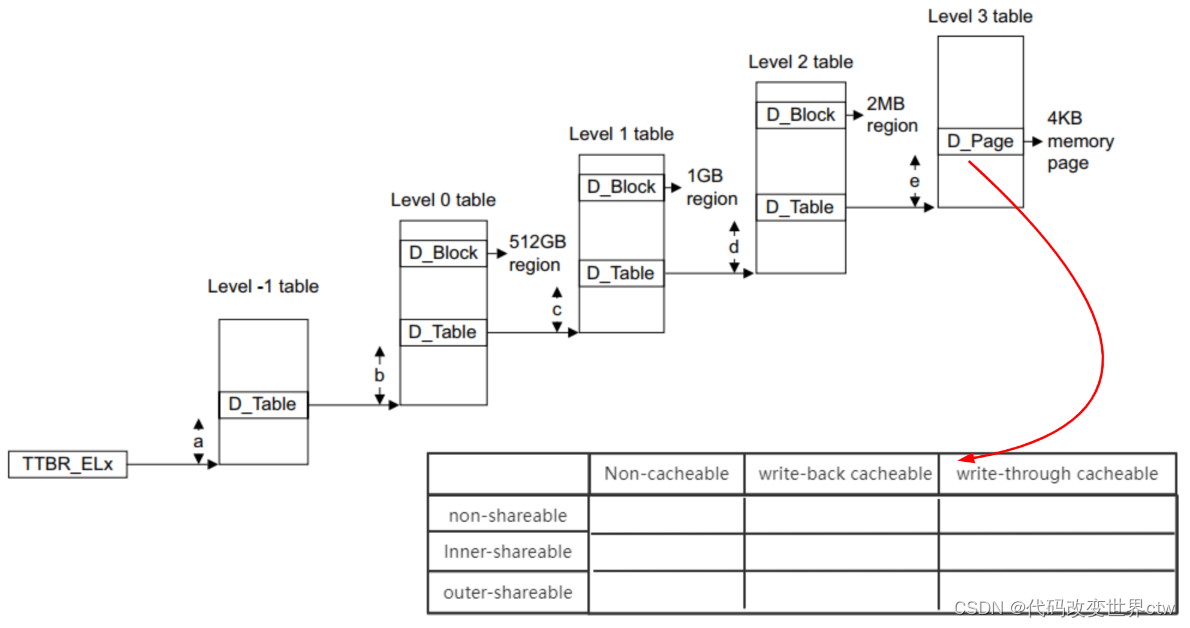

Для атрибута кэшируемого внутренний и внешний описывает определение или классификацию кэша. Например, считайте L1/L2 внутренним кэшем L3.

Обычно внутренний интегрированный кэш относится к внутреннему кэшу, а кэш на внешней шине AMBA принадлежит внешнему кэшу. Например:

- Для big.LITTLEАрхитектура (на примере A53) L1/L2 принадлежит внутренней кэш, если на SOC установлен L3, он принадлежит внешнему cache

- верно ВDynamIQАрхитектура(A76Например)середина,L1/L2/L3принадлежатьinner кэш, если Система зависла на SOC кэш (или другое имя), он принадлежит внешнему cache

Затем мы можем настроить отдельные свойства для каждого типа кэша, например:

- Конфигурация inner Non-cacheable 、Конфигурация inner Write-Through Cacheable 、Конфигурация inner Write-back Cacheable

- Конфигурация outer Non-cacheable 、Конфигурация outer Write-Through Cacheable 、Конфигурация outer Write-back Cacheable

Для общей собственности,внутренний и внешний описывает область кэша. Например, внутренний относится к кешу в диапазоне L1/L2.,внешний относится к кешу в диапазоне L1/L2/L3.

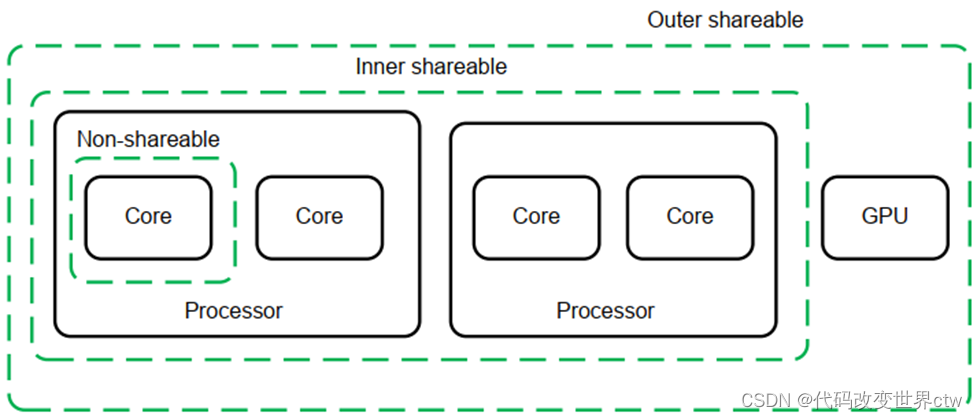

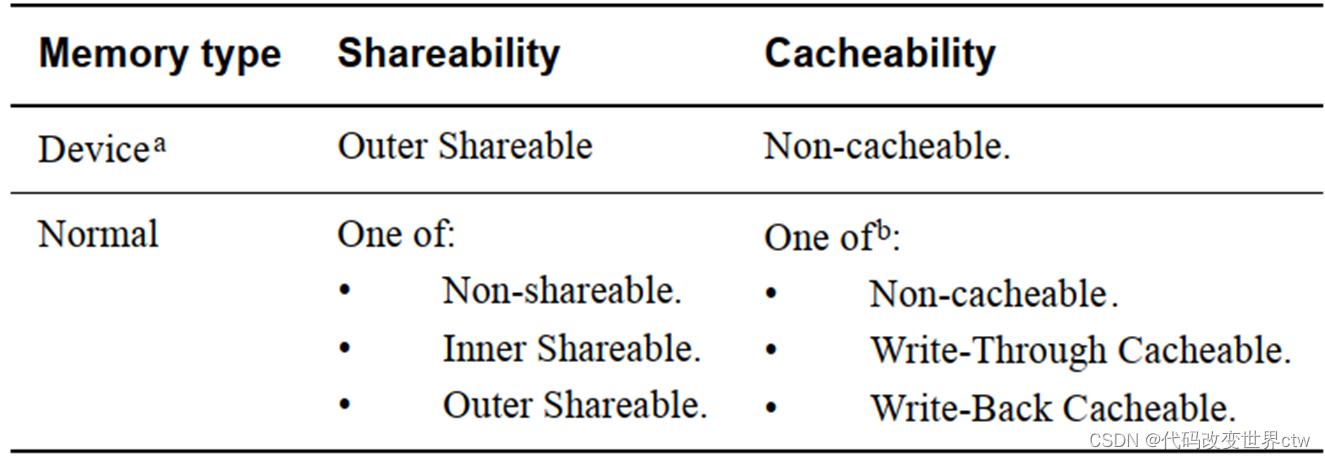

9. Типы памяти в архитектуре

В существующем рукаве Архитектура физическая память делится на два типа: аппаратную и обычную.

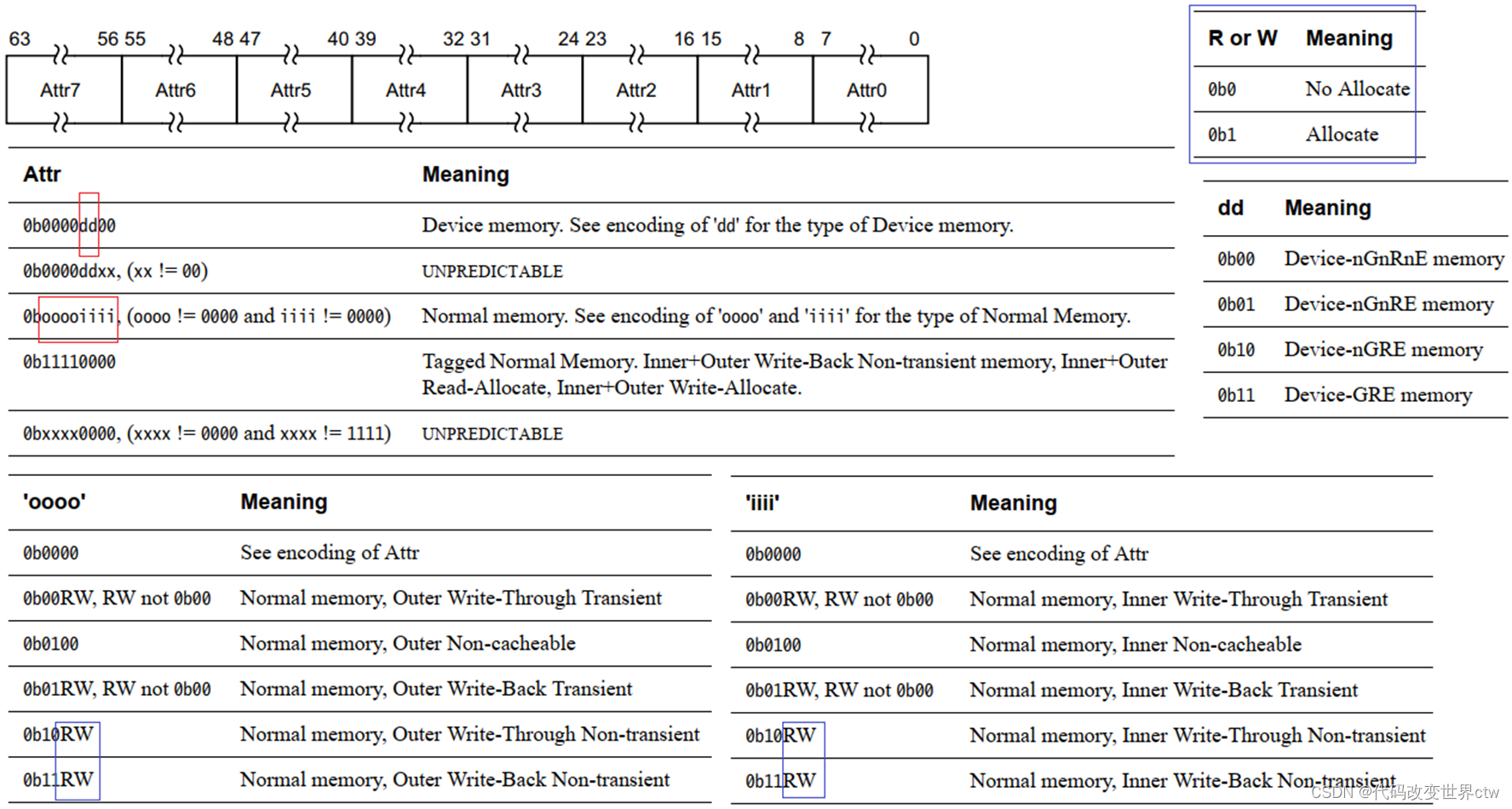

Вместо этого каждый тип памяти (устройство→обычный) имеет несколько атрибутов. ARM предоставляет регистр MAIR, Разделите 64-битный регистр на 8 полей атрибутов attr. Каждое поле атрибута attr имеет 8 бит и может быть настроено на различные атрибуты памяти. Другими словами, существует рука ядро поддерживает до 8 типов физической памяти.

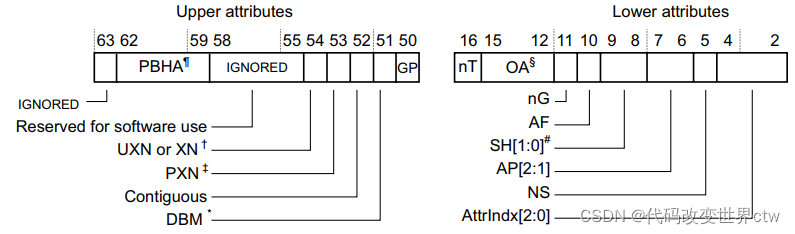

Среди битов атрибутов в записи таблицы страниц, используемых нашим существующимMMU, BIT[4:2] занимает 3 бита, обозначая индекс, который фактически указывает на attr в регистре MAIR. (Attribute fields in stage 1 VMSAv8-64 Block and Page descriptors)

PBHA, bits[62:59] :for FEAT_HPDS2 XN or UXN, bit[54] : Execute-never or Unprivileged execute-never PXN, bit[53] :Privileged execute-never Contiguous, bit[52] : translation table entry Он непрерывен и может хранить один TLB. Вход в DBM, bit[51] :Dirty Bit Modifier GP, bit[50] :for FEAT_BTI nT, bit[16] :for FEAT_BBM nG, bit[11] : кэшсуществовать Использует ли трансляция в TLB идентификацию ASID AF, bit[10] : Access flag, После AF=0 этот флаг будет установлен в 1 при первом доступе к странице. т.е. подразумевает первое посещение SH, bits[9:8] : общий атрибут AP[2:1], bits[7:6] :Data Access Permissions bits, NS, bit[5] :Non-secure bit AttrIndx[2:0], bits[4:2]

Другими словами, каждая запись в таблице страниц указывает на поле атрибута в регистре MAIR. То есть каждая запись в таблице страниц настроена по типу памяти. Как показано ниже, хорошо продемонстрировано, что каждый дескриптор страницы (также называемый записью) таблицы страниц MMU указывает на тип атрибута памяти.

Учебное пособие по Jetpack Compose для начинающих, базовые элементы управления и макет

Код js веб-страницы, фон частицы, код спецэффектов

【новый! Суперподробное】Полное руководство по свойствам компонентов Figma.

🎉Обязательно к прочтению новичкам: полное руководство по написанию мини-программ WeChat с использованием программного обеспечения Cursor.

[Забавный проект Docker] VoceChat — еще одно приложение для мгновенного чата (IM)! Может быть встроен в любую веб-страницу!

Как реализовать переход по странице в HTML (html переходит на указанную страницу)

Как решить проблему зависания и низкой скорости при установке зависимостей с помощью npm. Существуют ли доступные источники npm, которые могут решить эту проблему?

Серия From Zero to Fun: Uni-App WeChat Payment Practice WeChat авторизует вход в систему и украшает страницу заказа, создает интерфейс заказа и инициирует запрос заказа

Серия uni-app: uni.navigateЧтобы передать скачок значения

Апплет WeChat настраивает верхнюю панель навигации и адаптируется к различным моделям.

JS-время конвертации

Обеспечьте бесперебойную работу ChromeDriver 125: советы по решению проблемы chromedriver.exe не найдены

Поле комментария, щелчок мышью, специальные эффекты, js-код

Объект массива перемещения объекта JS

Как открыть разрешение на позиционирование апплета WeChat_Как использовать WeChat для определения местонахождения друзей

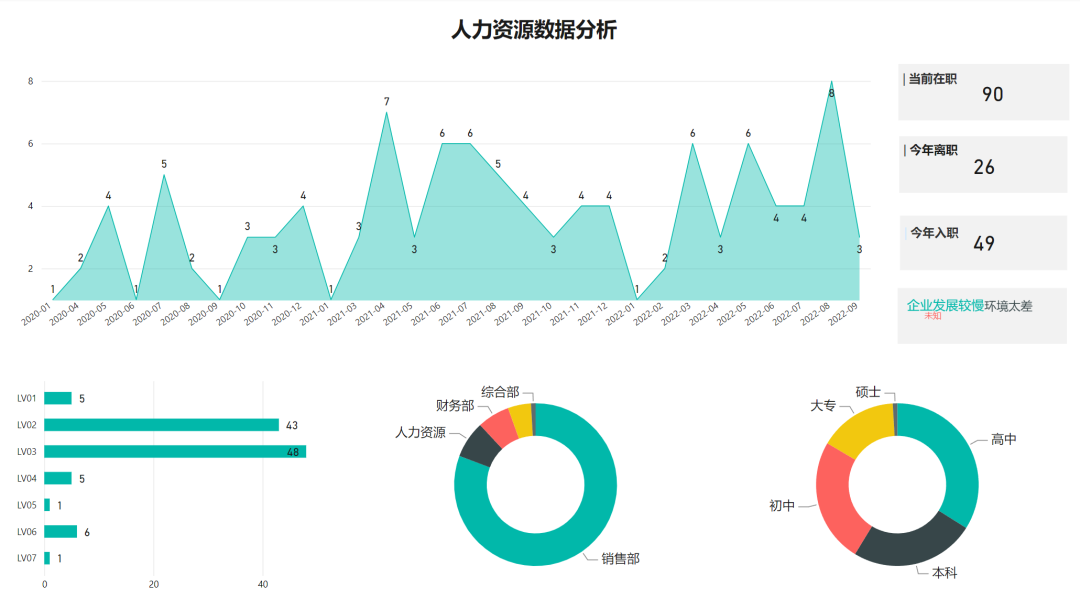

Я даю вам два набора из 18 простых в использовании фонов холста Power BI, так что вам больше не придется возиться с цветами!

Получить текущее время в js_Как динамически отображать дату и время в js

Вам необходимо изучить сочетания клавиш vsCode для форматирования и организации кода, чтобы вам больше не приходилось настраивать формат вручную.

У ChatGPT большое обновление. Всего за 45 минут пресс-конференция показывает, что OpenAI сделал еще один шаг вперед.

Copilot облачной разработки — упрощение разработки

Микросборка xChatGPT с низким кодом, создание апплета чат-бота с искусственным интеллектом за пять шагов

CUDA Out of Memory: идеальное решение проблемы нехватки памяти CUDA

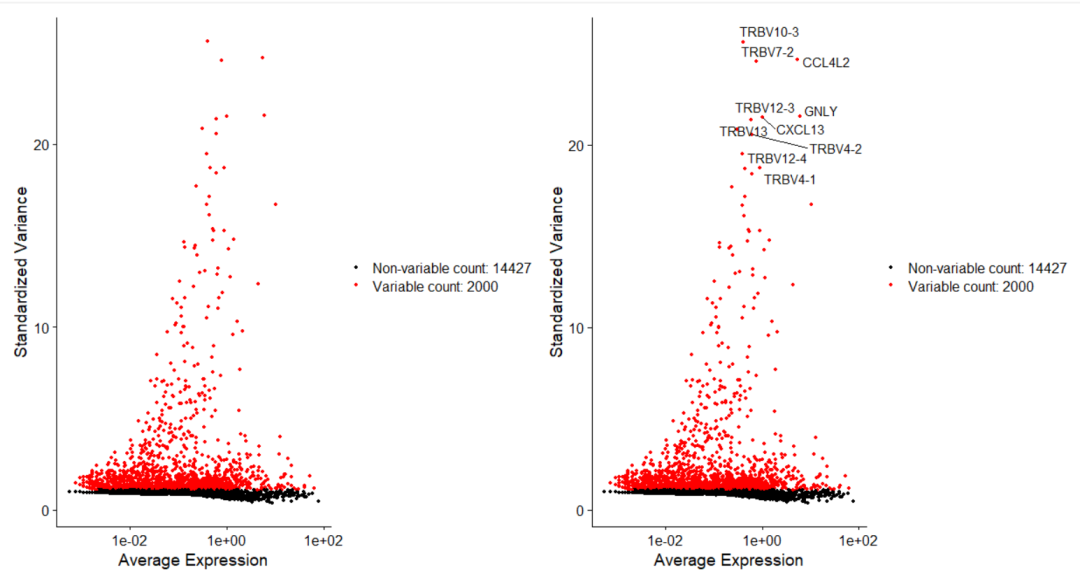

Анализ кластеризации отдельных ячеек, который должен освоить каждый&MarkerгенетическийВизуализация

vLLM: мощный инструмент для ускорения вывода ИИ

CodeGeeX: мощный инструмент генерации кода искусственного интеллекта, который можно использовать бесплатно в дополнение к второму пилоту.

Машинное обучение Реальный бой LightGBM + настройка параметров случайного поиска: точность 96,67%

Бесшовная интеграция, мгновенный интеллект [1]: платформа больших моделей Dify-LLM, интеграция без кодирования и встраивание в сторонние системы, более 42 тысяч звезд, чтобы стать свидетелями эксклюзивных интеллектуальных решений.

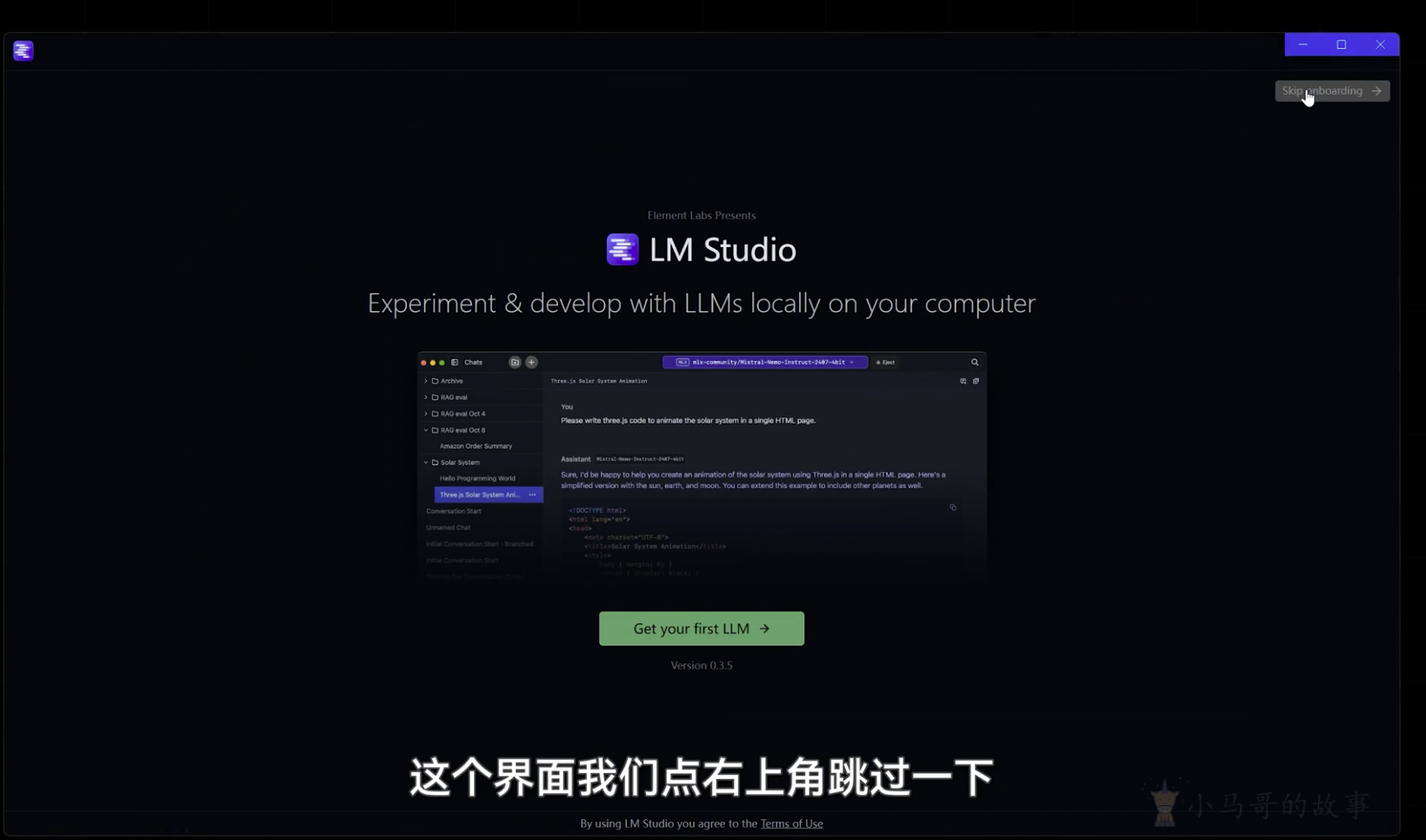

LM Studio для создания локальных больших моделей

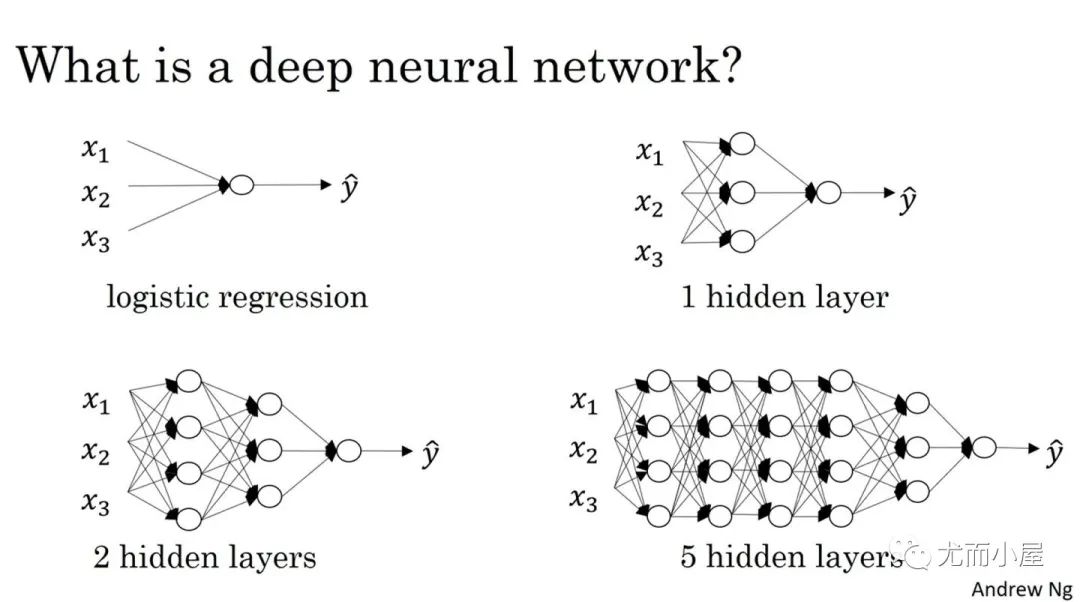

Как определить количество слоев и нейронов скрытых слоев нейронной сети?