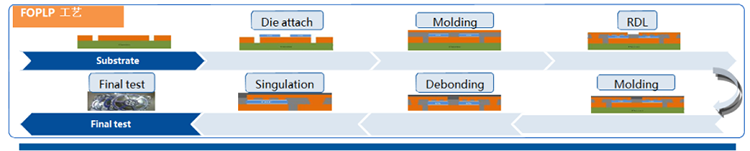

Углубленный анализ инженеров по тестированию чипов: корпус на уровне платы FOPLP: технические характеристики и области применения

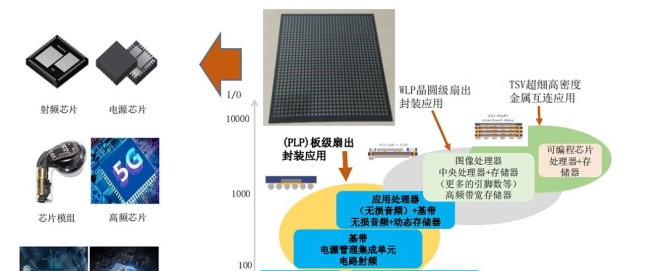

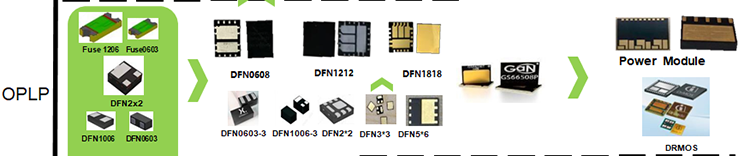

С быстрым развитием полупроводниковых технологий растут и требования к процессам упаковки микросхем. Разработка технологии упаковки особенно важна для обработки высокочастотных, радиочастотных чипов, источников питания и датчиков. Среди многих упаковочных технологий упаковка на уровне панели с разветвлением (FOPLP) постепенно выделилась своими уникальными преимуществами и стала центром внимания отрасли.

Особенности технологии упаковки на уровне платы FOPLP

1. Расширенная область упаковки

Технология FOPLP монтирует один чип и окружающие его схемы на большую материальную панель, образуя разветвленную форму. Этот метод позволяет значительно сократить длину соединений между чипами, тем самым уменьшая потери при передаче и помехи сигнала, а также улучшая электрические характеристики.

2. Улучшение интеграции

По сравнению с традиционной технологией упаковки, FOPLP может вместить больше микросхем и функций, интегрированных вместе, и подходит для упаковки сложных многочиповых модулей. FOPLP увеличивает плотность упаковки за счет увеличения площади панели, позволяя интегрировать больше функциональных блоков в ограниченном пространстве, тем самым улучшая производительность системы.

3. Оптимизация терморегулирования

Технология FOPLP использует лучшие теплопроводящие материалы в процессе упаковки, улучшает способность рассеивания тепла за счет разумной конструкции, снижает рабочую температуру чипа и повышает надежность и срок службы.

Применение FOPLP в различных типах чипов

РФ чип

в РФ В области чипов технология FOPLP имеет значительные преимущества. РФ Чип предъявляет высокие требования к стабильности сигнала и возможностям шумоподавления. Технология FOPLP может более эффективно изолировать шумовые помехи, обеспечить лучший путь передачи сигнала и в то же время улучшить качество сигнала и скорость передачи за счет оптимизации структуры упаковки.

Чип питания

Чип Питание требует эффективного отвода тепла, а также хороших электрических свойств и механической прочности. Технология FOPLP обеспечивает безопасность благодаря высокой плотности интеграции и оптимизированным путям рассеивания тепла. питания Стабильная работа в условиях высокой мощности. Кроме того, технология FOPLP обеспечивает превосходную механическую прочность, гарантируя стабильность и надежность упаковки.

Чип-модуль

Чип-модуль — это системный блок, в котором совместно работают различные чипы. Технология FOPLP позволяет интегрировать несколько чипов на одной панели.,Упрощение конструкции модуля,Улучшите системную интеграцию. также,Технология FOPLP оптимизирует структуру соединения между чипами,Улучшите общую производительность и надежность модуля.

Высокочастотный чип

Высокочастотный Чип играет жизненно важную роль в оборудовании связи, требующем высокой пропускной способности, низкой задержки и высокого качества передачи сигнала. Технология FOPLP позволяет эффективно снизить потери сигнала в процессе упаковки и оптимизировать путь передачи сигнала, тем самым повышая эффективность Высокочастотного Производительность и надежность чипа.

цифровой чип

цифровой Чип охватывает основные компоненты, такие как процессоры и контроллеры. Технология FOPLP улучшает рассеивание тепла и электрические характеристики чипа за счет улучшения дизайна упаковки, что делает цифровой Чип может работать более стабильно и эффективно во время рабочего процесса.

сенсорный чип

сенсорный Чип используется для обнаружения и обратной связи об изменениях окружающей среды и предъявляет высокие требования к объему и энергопотреблению. Технология FOPLP улучшает сенсорность за счет оптимизации площади корпуса и конструкции схемы. Чувствительность и точность чипа, одновременно снижая энергопотребление и улучшая возможности защиты от помех.

Преимущества упаковки FOPLP для тестирования чипов

1. Более высокая эффективность тестирования

Благодаря высокому уровню интеграции и большой площади упаковки упаковка FOPLP позволяет тестировать больше чипов за один испытательный процесс. По сравнению с традиционной технологией упаковки упаковка FOPLP значительно повышает эффективность и скорость испытаний, а также снижает затраты на испытания.

2. Предоставьте более полные данные испытаний

Поскольку технология упаковки FOPLP оптимизирует соединения и пути передачи сигналов между чипами, в ходе процесса тестирования можно получить более полные и точные тестовые данные, что обеспечивает лучшую основу для оценки производительности чипа.

3. Улучшите эффективность охлаждения

В процессе тестирования особенно важно контролировать температуру чипа. Технология упаковки FOPLP обеспечивает контроль температуры чипа в условиях работы с высокой мощностью за счет оптимизации пути рассеивания тепла, тем самым повышая точность и стабильность результатов испытаний.

4. Гибкие решения для тестирования

Технология упаковки FOPLP обеспечивает высокую гибкость,Таким образом, персонализированные тестовые решения могут быть разработаны в соответствии с различными характеристиками и потребностями. Будь то Высокочастотный чип, RF-чип или Чип питания., технология упаковки FOPLP может предоставить подходящие решения для испытаний, гарантирующие последовательность и надежность результатов испытаний.

Необходимость индивидуальных тестовых розеток

Хотя упаковка FOPLP демонстрирует большие преимущества во многих аспектах, в процессе тестирования чипов конструкцию и изготовление тестовых разъемов часто необходимо адаптировать для конкретных приложений. Это связано с тем, что разные типы чипов и сценарии их применения предъявляют разные требования к тестовым разъемам, в том числе:

1. Особые электрические и механические требования

Различные типы чипов должны иметь особенности во время тестирования. электрические и механические требования。Например,Высокочастотный Чип должен иметь отличные возможности изоляции сигнала. питание требует хороших показателей теплоотвода и т. д. Поэтому конструкция тестового разъема должна быть специально разработана в соответствии с конкретными характеристиками чипа.

2. Очень гибкая структура подключения

Высокий уровень интеграции и характеристики сосуществования нескольких микросхем в корпусе FOPLP требуют, чтобы тестовый сокет имел Очень гибкая структура подключение для адаптации к различным потребностям тестирования. Стандартизированные тестовые розетки часто не могут удовлетворить этот спрос, поэтому возникает необходимость в индивидуальной конструкции.

3. Точные возможности сбора и анализа данных

К высокопроизводительным чипам предъявляются высокие требования к точности и возможностям анализа тестовых данных. Для точного сбора и анализа тестовых данных тестовое гнездо должно иметь профессиональную и высокоточную конструкцию. Стандартные продукты не могут полностью удовлетворить эту потребность и должны быть адаптированы к конкретному чипу.

С развитием технологии чипов и технологии упаковки,Упаковка FOPLP на уровне платы отличается превосходной масштабируемостью, высокой степенью интеграции и оптимизированными возможностями управления температурным режимом.,Он продемонстрировал значительные технические преимущества в области радиочастотных чипов, чипов питания, сенсорных чипов и других областях. в то же время,Упаковка FOPLP обладает более высокой эффективностью и более полными возможностями сбора данных в процессе тестирования. Однако из-за различных характеристик разных чипов с точки зрения электрических свойств, механических требований и структур соединения,,Тестовые сокеты необходимо настраивать для конкретных приложений.,Обеспечить точность и надежность процесса тестирования.

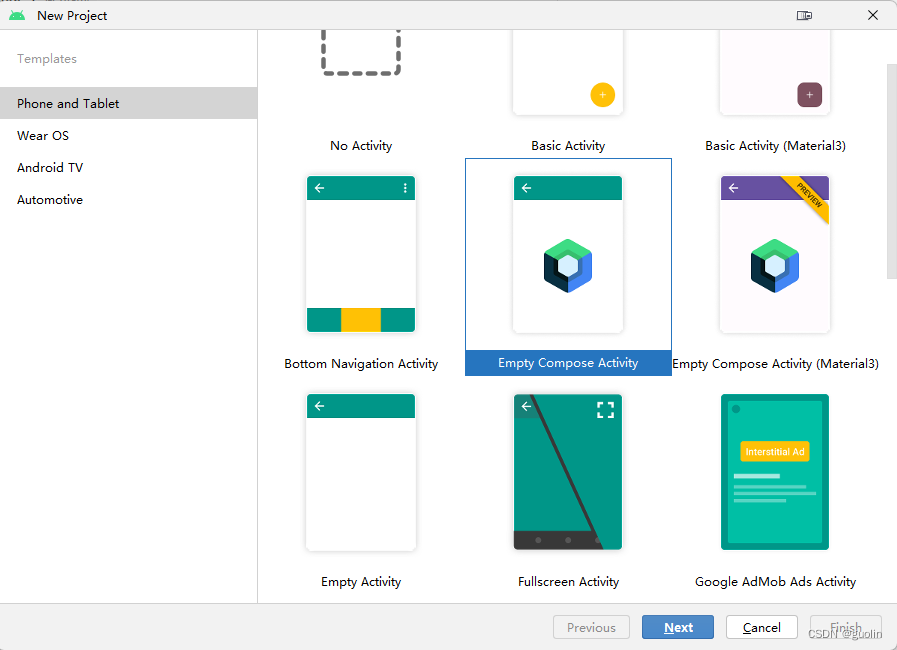

Учебное пособие по Jetpack Compose для начинающих, базовые элементы управления и макет

Код js веб-страницы, фон частицы, код спецэффектов

【новый! Суперподробное】Полное руководство по свойствам компонентов Figma.

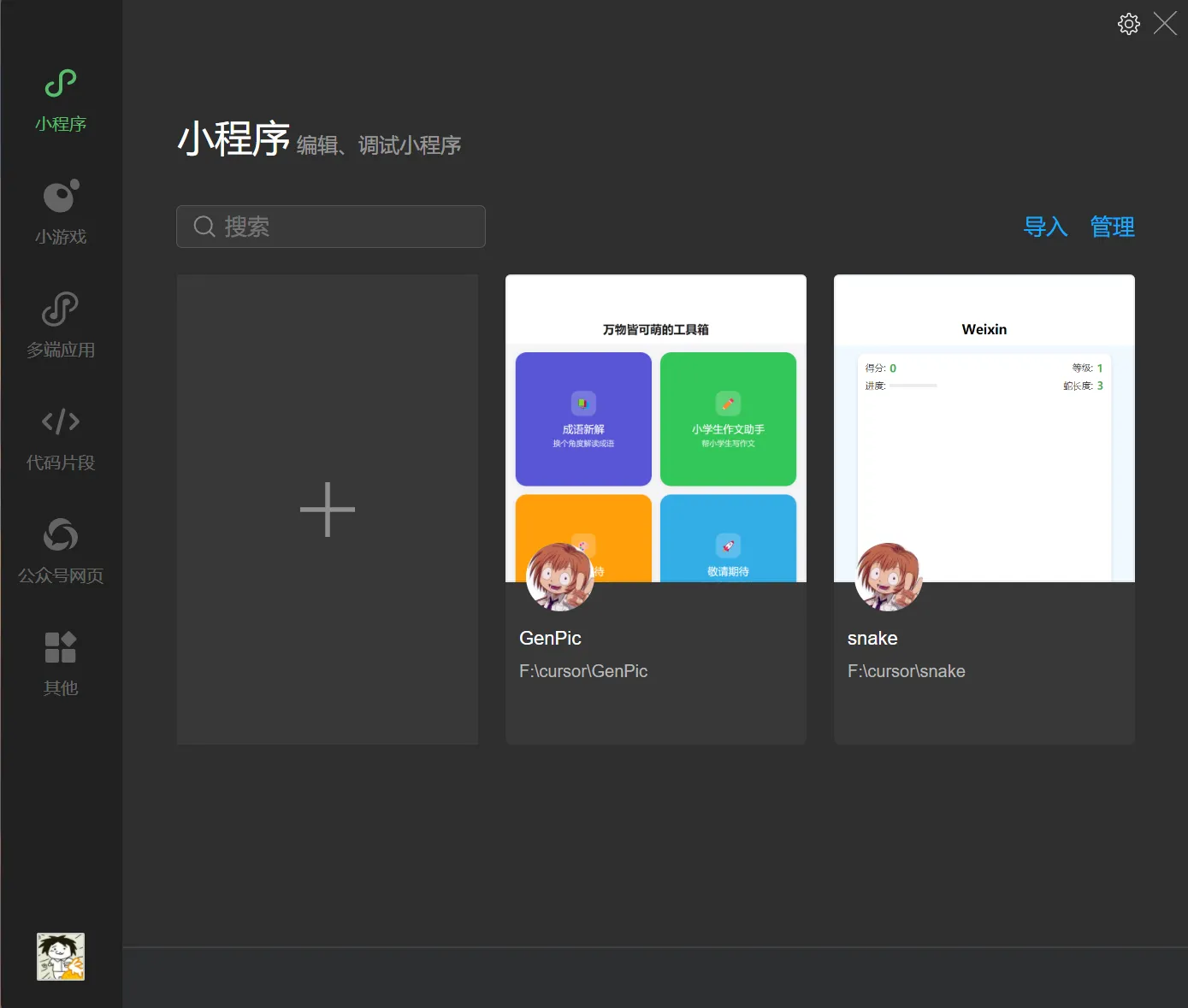

🎉Обязательно к прочтению новичкам: полное руководство по написанию мини-программ WeChat с использованием программного обеспечения Cursor.

[Забавный проект Docker] VoceChat — еще одно приложение для мгновенного чата (IM)! Может быть встроен в любую веб-страницу!

Как реализовать переход по странице в HTML (html переходит на указанную страницу)

Как решить проблему зависания и низкой скорости при установке зависимостей с помощью npm. Существуют ли доступные источники npm, которые могут решить эту проблему?

Серия From Zero to Fun: Uni-App WeChat Payment Practice WeChat авторизует вход в систему и украшает страницу заказа, создает интерфейс заказа и инициирует запрос заказа

Серия uni-app: uni.navigateЧтобы передать скачок значения

Апплет WeChat настраивает верхнюю панель навигации и адаптируется к различным моделям.

JS-время конвертации

Обеспечьте бесперебойную работу ChromeDriver 125: советы по решению проблемы chromedriver.exe не найдены

Поле комментария, щелчок мышью, специальные эффекты, js-код

Объект массива перемещения объекта JS

Как открыть разрешение на позиционирование апплета WeChat_Как использовать WeChat для определения местонахождения друзей

Я даю вам два набора из 18 простых в использовании фонов холста Power BI, так что вам больше не придется возиться с цветами!

Получить текущее время в js_Как динамически отображать дату и время в js

Вам необходимо изучить сочетания клавиш vsCode для форматирования и организации кода, чтобы вам больше не приходилось настраивать формат вручную.

У ChatGPT большое обновление. Всего за 45 минут пресс-конференция показывает, что OpenAI сделал еще один шаг вперед.

Copilot облачной разработки — упрощение разработки

Микросборка xChatGPT с низким кодом, создание апплета чат-бота с искусственным интеллектом за пять шагов

CUDA Out of Memory: идеальное решение проблемы нехватки памяти CUDA

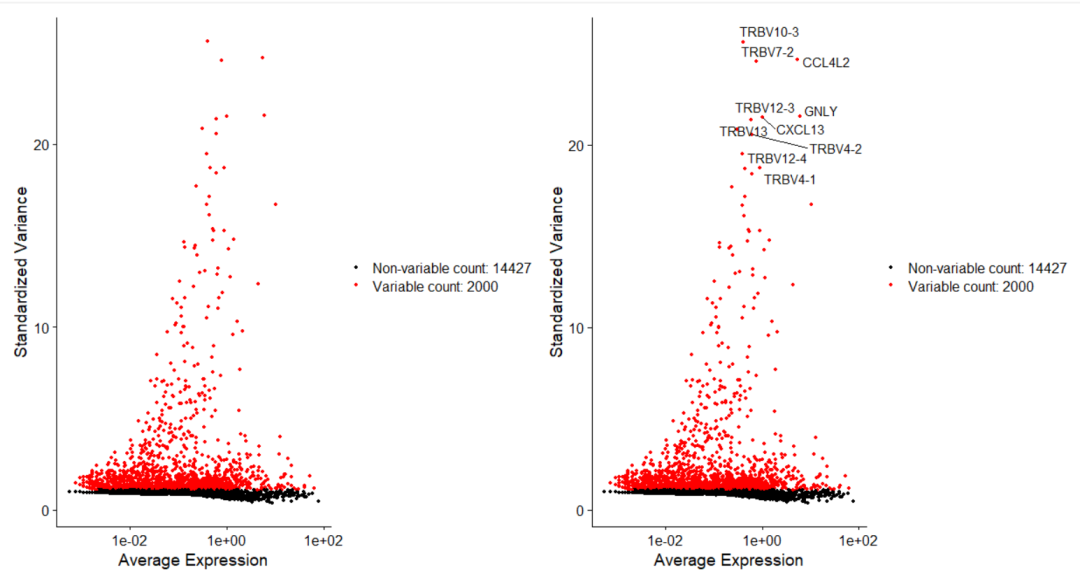

Анализ кластеризации отдельных ячеек, который должен освоить каждый&MarkerгенетическийВизуализация

vLLM: мощный инструмент для ускорения вывода ИИ

CodeGeeX: мощный инструмент генерации кода искусственного интеллекта, который можно использовать бесплатно в дополнение к второму пилоту.

Машинное обучение Реальный бой LightGBM + настройка параметров случайного поиска: точность 96,67%

Бесшовная интеграция, мгновенный интеллект [1]: платформа больших моделей Dify-LLM, интеграция без кодирования и встраивание в сторонние системы, более 42 тысяч звезд, чтобы стать свидетелями эксклюзивных интеллектуальных решений.

LM Studio для создания локальных больших моделей

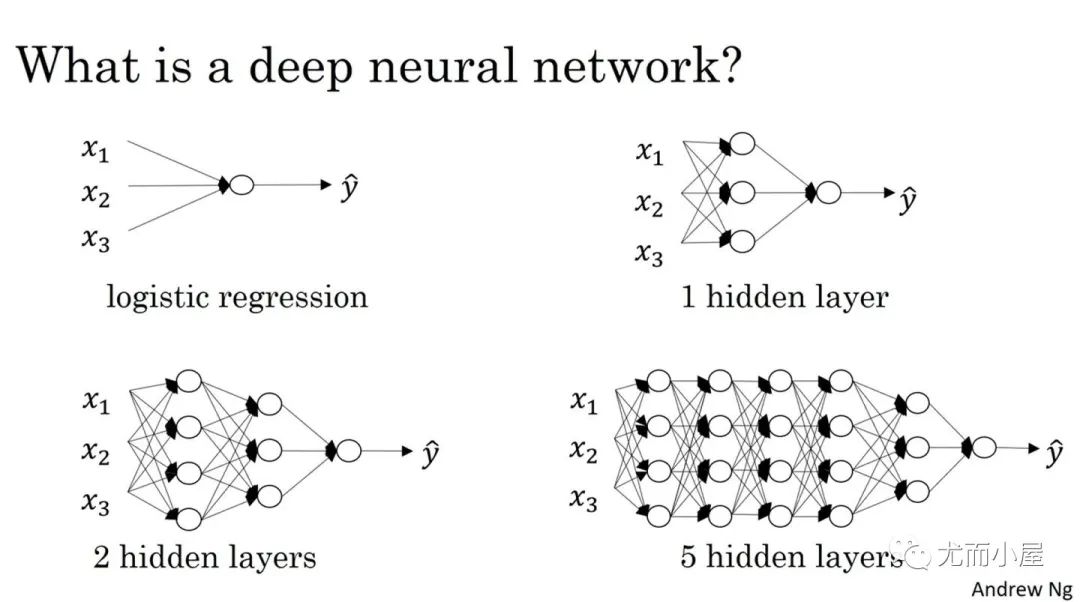

Как определить количество слоев и нейронов скрытых слоев нейронной сети?