Оптимизация конструкции с использованием теоремы расширения Шеннона

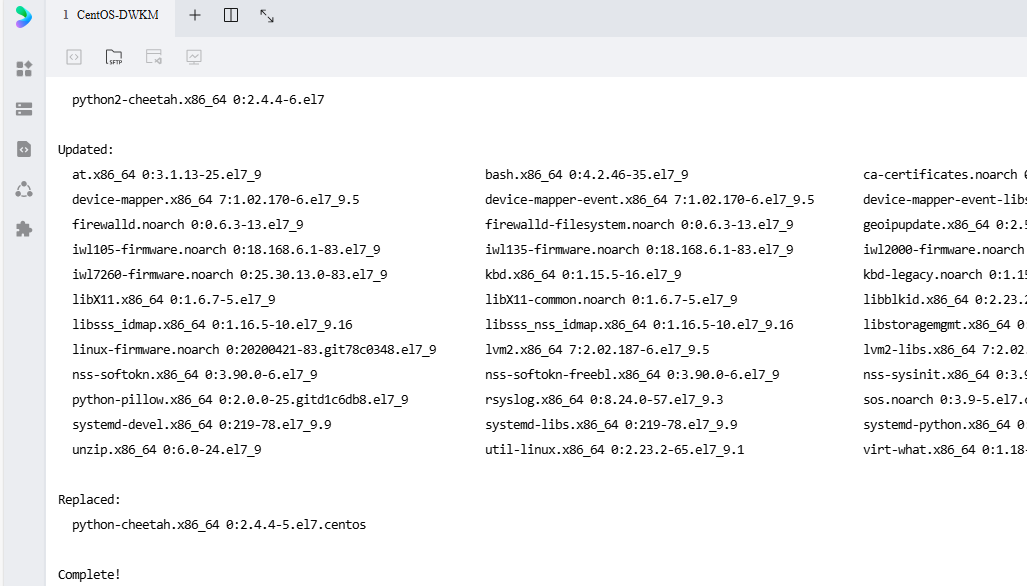

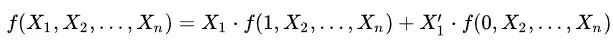

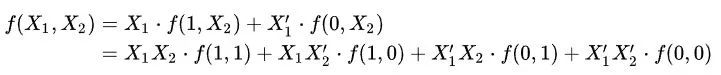

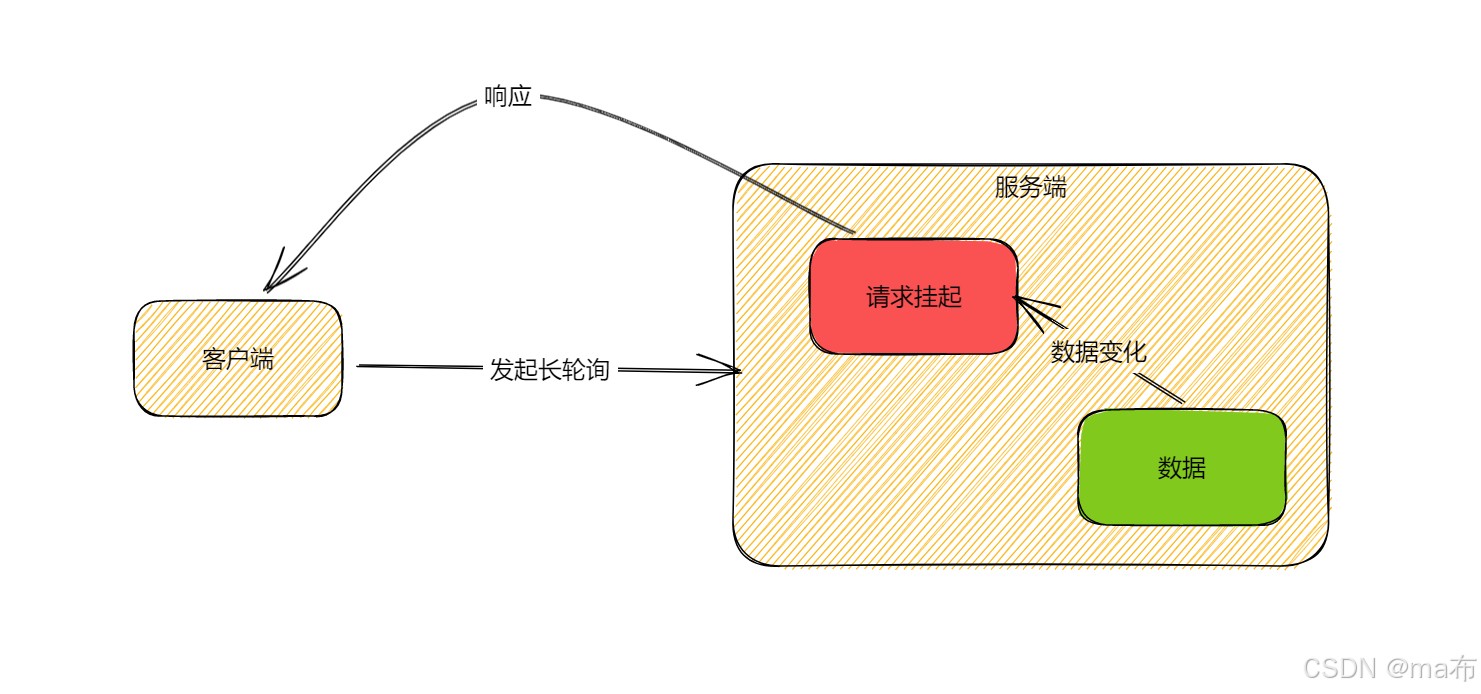

Расширение Шеннона или разложение Шеннона — это метод преобразования булевых функций. Он может выразить любую логическую функцию как любую переменную, умноженную на подфункцию, плюс обратную переменную этой переменной, умноженную на другую подфункцию, как показано в следующих двух формулах.

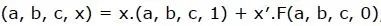

Используя теорему Шеннона о расширении логистической функции, вы можете использовать извлеченную переменную в качестве сигнала выбора, а затем использовать селектор данных для реализации функции. Например:

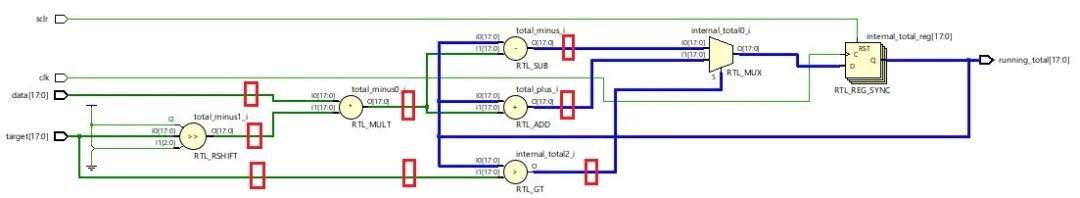

В результате получается следующая схема:

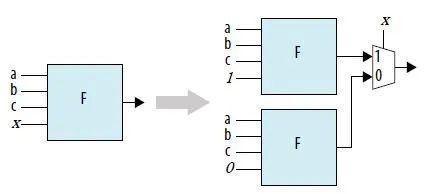

В этой схеме возникает ситуация, когда один из входных портов всегда равен 1 или 0. Инструмент дополнительно оптимизирует это во время логического синтеза, как показано на рисунке ниже.

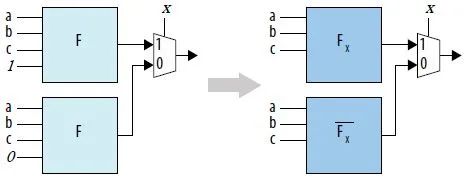

Фактически, теорему о разложении Шеннона можно многократно использовать для приведенной выше схемы, чтобы сформировать схему, показанную на рисунке ниже.

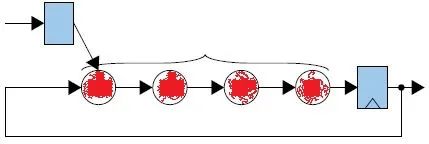

Теорема расширения Шеннона особенно существенно улучшает логические циклы. Как показано на рисунке ниже, из-за существования циклов путь, отмеченный на рисунке красным, не работает правильно после его вставки в регистр конвейера.

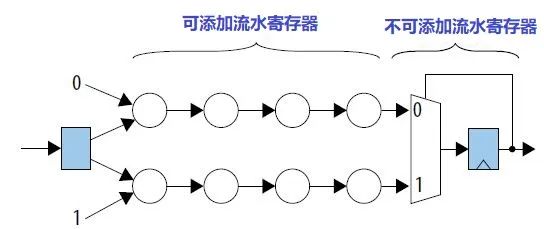

Конвейерные регистры можно добавлять только вне цикла, что требует использования теоремы расширения Шеннона. Извлеките коэффициенты обратной связи и установите их равными 0 и 1 соответственно, тем самым открывая цикл для формирования двух независимых путей и добавляя селектор данных с двумя вариантами в конце пути, конец управления которого обеспечивается выходной обратной связью, и, наконец, образует следующий рисунок: показана схема.

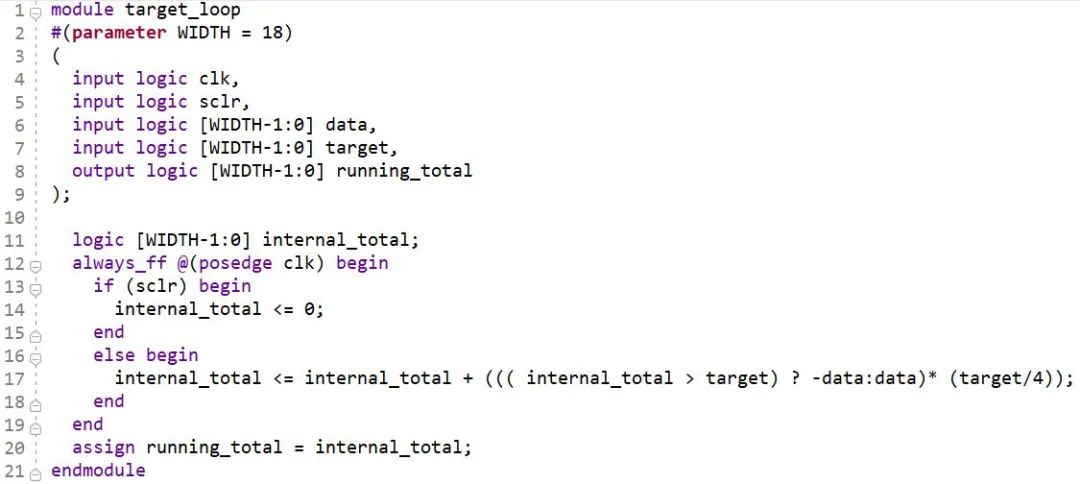

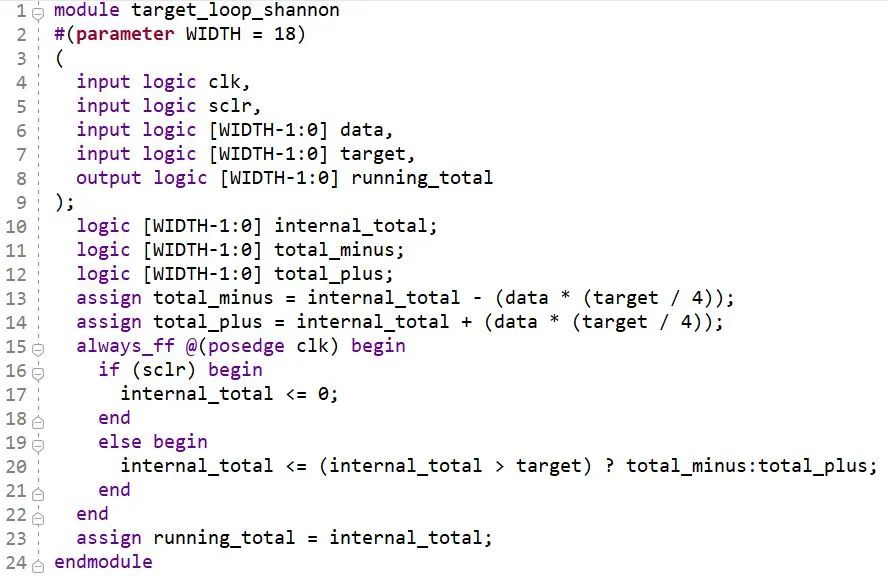

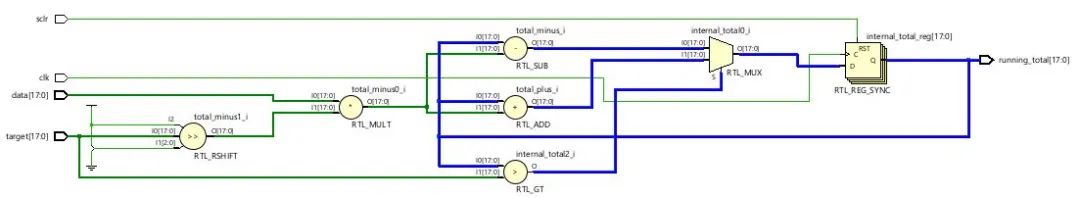

Давайте рассмотрим случай: фрагмент кода, показанный на рисунке ниже. Обратите внимание, что строка 17 образует цикл обратной связи, и именно цикл обратной связи становится узким местом в производительности синхронизации. Этот путь имеет как таблицы поиска, так и DSP (реализующий операции умножения) и не содержит дополнительных регистров конвейера.

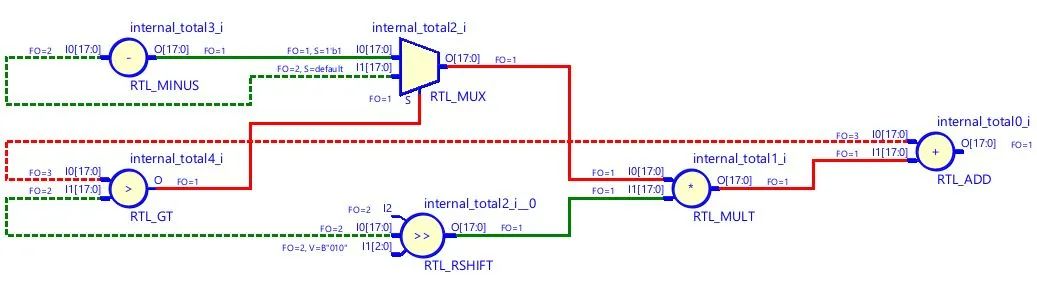

Основываясь на теореме расширения Шеннона, мы оптимизировали код до следующей формы. Обратите внимание, что в строках 13 и 14 кода добавлены две новые переменные, соответствующие ситуации, когда Internal_total больше целевого и меньше целевого значения соответственно, тем самым открывая. петля.

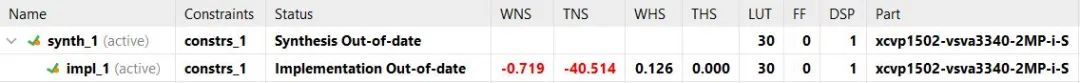

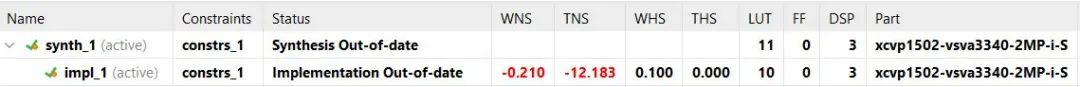

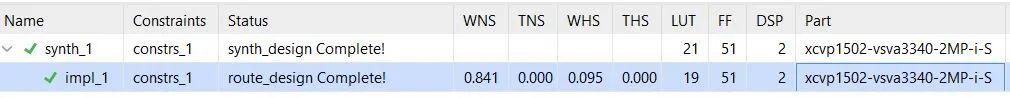

При сравнении двух вышеуказанных схем целевой чип — xcvp1502, тактовая частота — 400 МГц, используется Vivado2023.2. Окончательная производительность показана на рисунке ниже. Видно, что после использования теоремы о разложении Шеннона WNS увеличивается с исходного -0,719 до -0,210. Но все еще не достиг цели в 400 МГц. На этом этапе мы можем продолжить оптимизацию.

Поскольку в этот момент цикл уже открыт, мы можем вставить соответствующие регистры конвейера, как показано на рисунке ниже. Красный прямоугольник на рисунке представляет регистр конвейера. Это может еще больше улучшить WNS, и итоговое значение WNS равно 0,841, что означает, что эта часть пути может работать как минимум до 500 МГц.

Авторские права @ Технологическая станция FPGA

По вопросам перепечатки пишите в личное сообщение | Перепечатка разрешена только после получения разрешения.

Неразрушающее увеличение изображений одним щелчком мыши, чтобы сделать их более четкими артефактами искусственного интеллекта, включая руководства по установке и использованию.

Копикодер: этот инструмент отлично работает с Cursor, Bolt и V0! Предоставьте более качественные подсказки для разработки интерфейса (создание навигационного веб-сайта с использованием искусственного интеллекта).

Новый бесплатный RooCline превосходит Cline v3.1? ! Быстрее, умнее и лучше вилка Cline! (Независимое программирование AI, порог 0)

Разработав более 10 проектов с помощью Cursor, я собрал 10 примеров и 60 подсказок.

Я потратил 72 часа на изучение курсорных агентов, и вот неоспоримые факты, которыми я должен поделиться!

Идеальная интеграция Cursor и DeepSeek API

DeepSeek V3 снижает затраты на обучение больших моделей

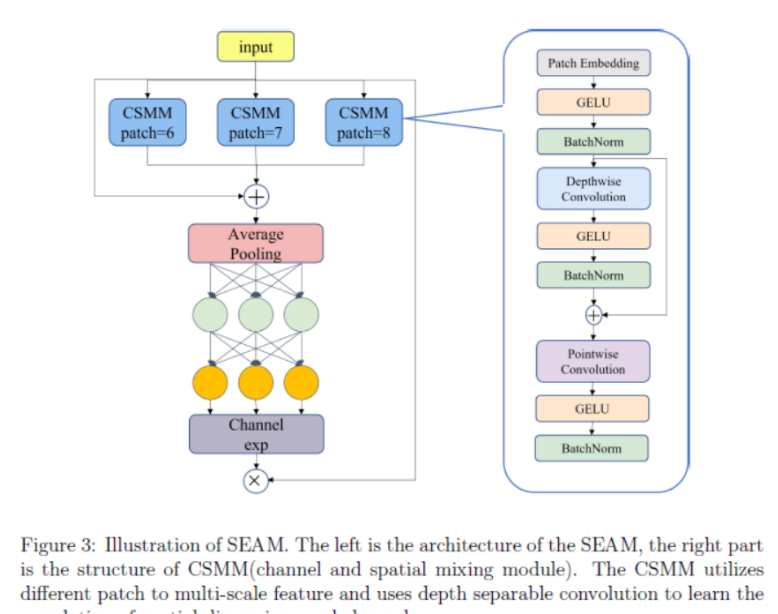

Артефакт, увеличивающий количество очков: на основе улучшения характеристик препятствия малым целям Yolov8 (SEAM, MultiSEAM).

DeepSeek V3 раскручивался уже три дня. Сегодня я попробовал самопровозглашенную модель «ChatGPT».

Open Devin — инженер-программист искусственного интеллекта с открытым исходным кодом, который меньше программирует и больше создает.

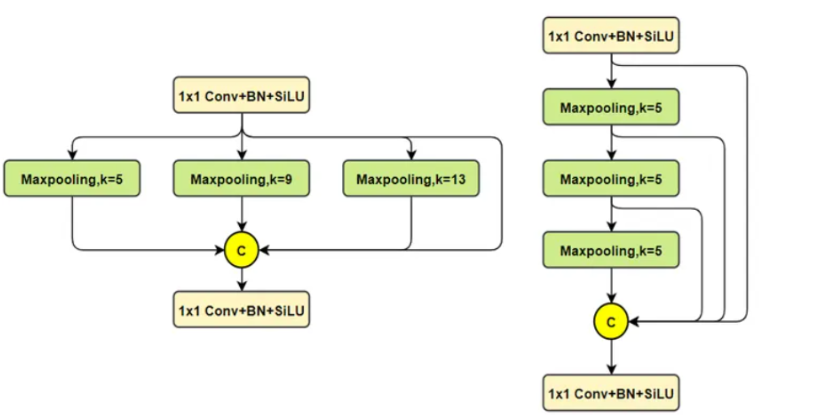

Эксклюзивное оригинальное улучшение YOLOv8: собственная разработка SPPF | SPPF сочетается с воспринимаемой большой сверткой ядра UniRepLK, а свертка с большим ядром + без расширения улучшает восприимчивое поле

Популярное и подробное объяснение DeepSeek-V3: от его появления до преимуществ и сравнения с GPT-4o.

9 основных словесных инструкций по доработке академических работ с помощью ChatGPT, эффективных и практичных, которые стоит собрать

Вызовите deepseek в vscode для реализации программирования с помощью искусственного интеллекта.

Познакомьтесь с принципами сверточных нейронных сетей (CNN) в одной статье (суперподробно)

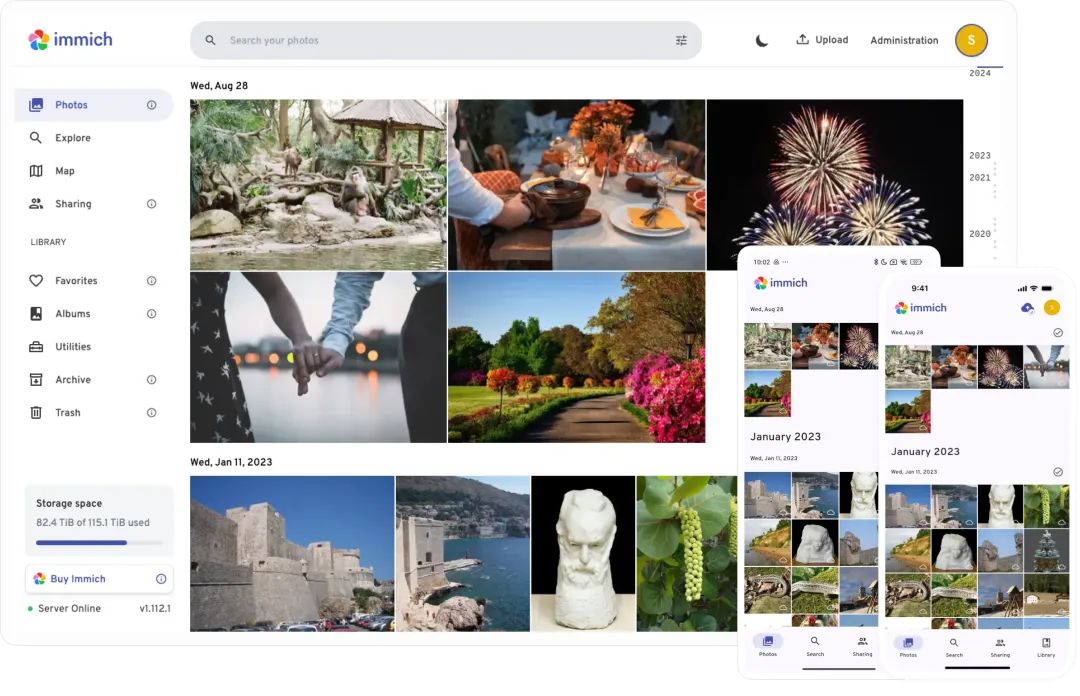

50,3 тыс. звезд! Immich: автономное решение для резервного копирования фотографий и видео, которое экономит деньги и избавляет от беспокойства.

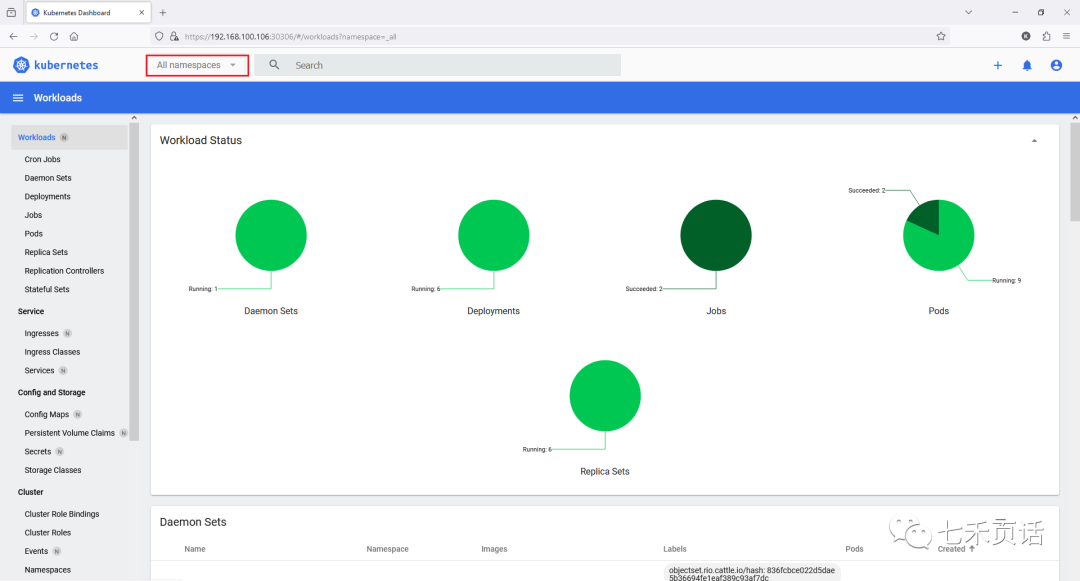

Cloud Native|Практика: установка Dashbaord для K8s, графика неплохая

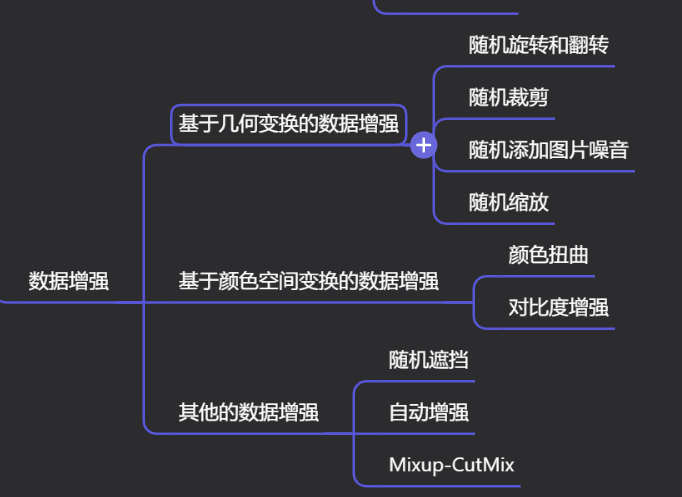

Краткий обзор статьи — использование синтетических данных при обучении больших моделей и оптимизации производительности

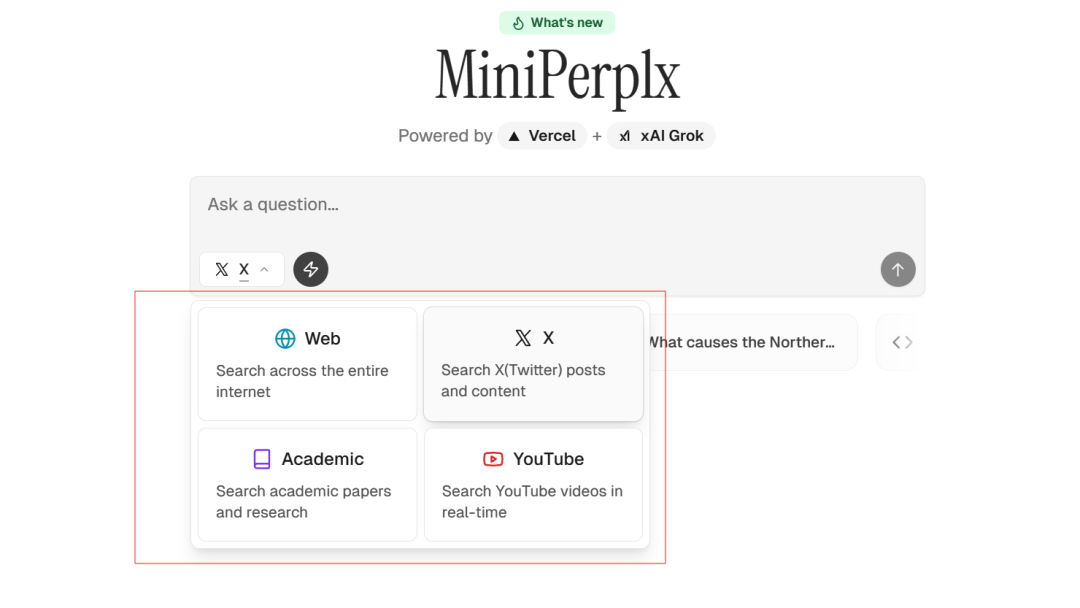

MiniPerplx: новая поисковая система искусственного интеллекта с открытым исходным кодом, спонсируемая xAI и Vercel.

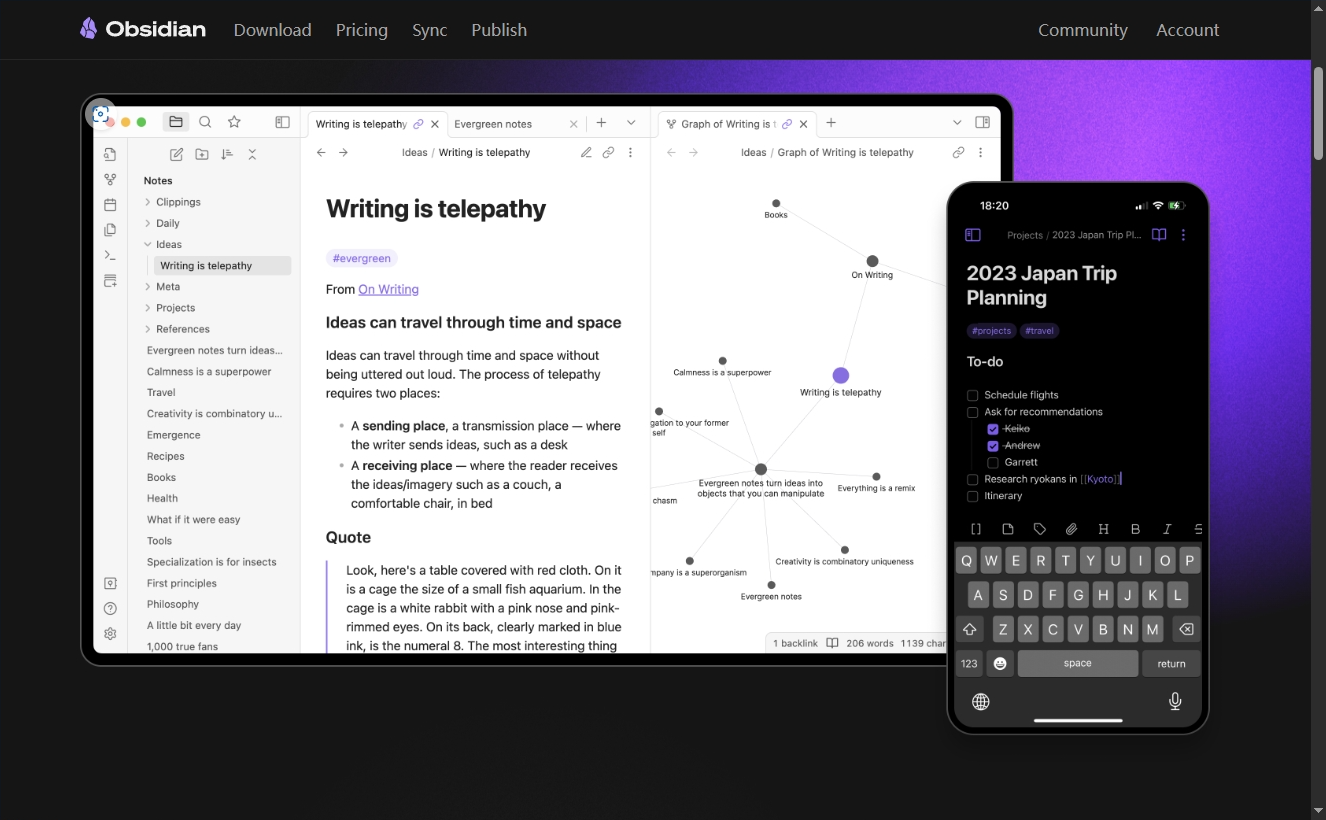

Конструкция сервиса Synology Drive сочетает проникновение в интрасеть и синхронизацию папок заметок Obsidian в облаке.

Центр конфигурации————Накос

Начинаем с нуля при разработке в облаке Copilot: начать разработку с минимальным использованием кода стало проще

[Серия Docker] Docker создает мультиплатформенные образы: практика архитектуры Arm64

Обновление новых возможностей coze | Я использовал coze для создания апплета помощника по исправлению домашних заданий по математике

Советы по развертыванию Nginx: практическое создание статических веб-сайтов на облачных серверах

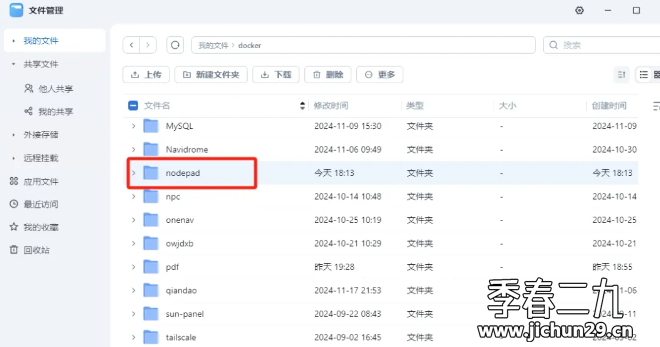

Feiniu fnos использует Docker для развертывания личного блокнота Notepad

Сверточная нейронная сеть VGG реализует классификацию изображений Cifar10 — практический опыт Pytorch

Начало работы с EdgeonePages — новым недорогим решением для хостинга веб-сайтов

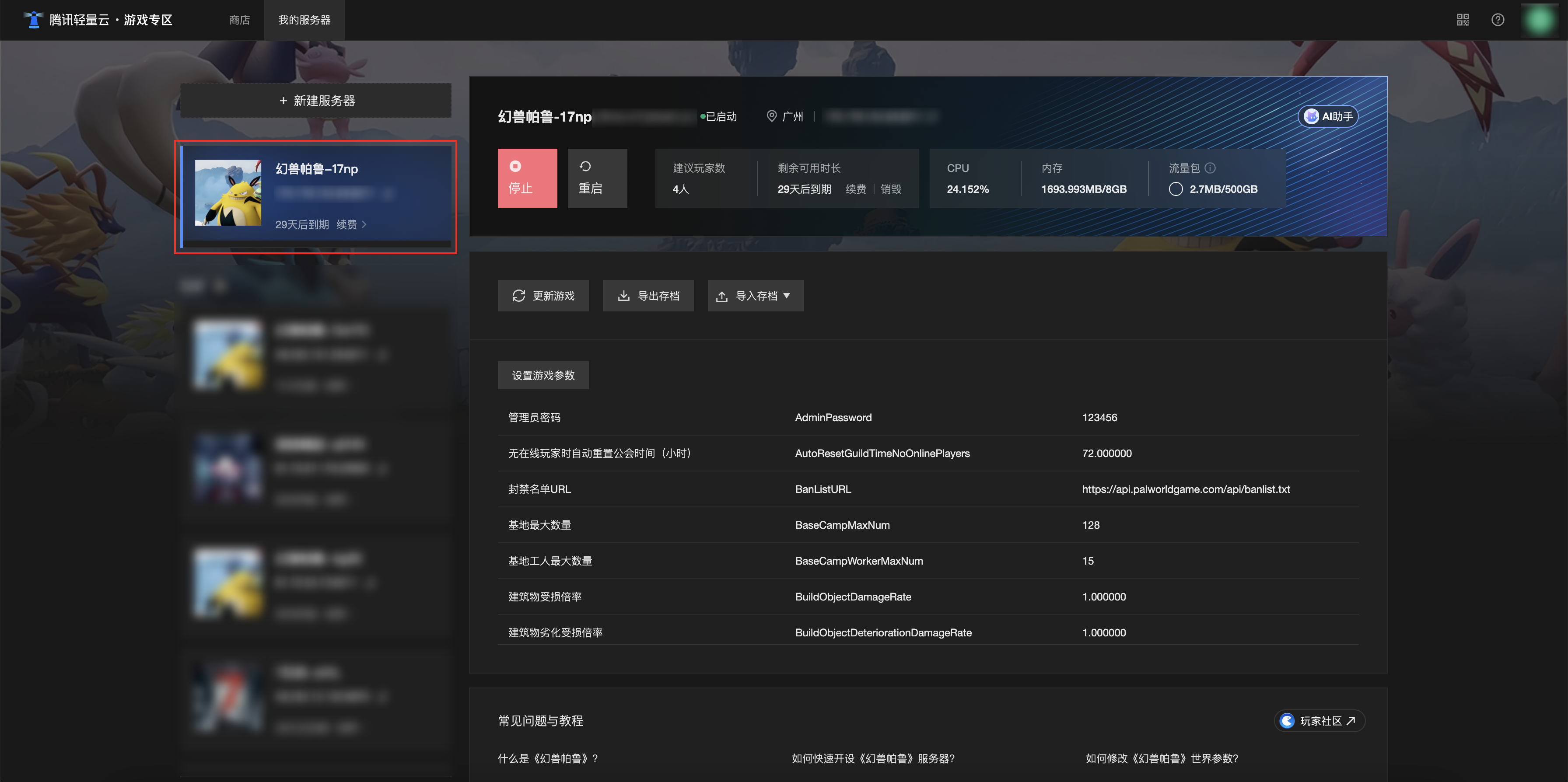

[Зона легкого облачного игрового сервера] Управление игровыми архивами