[Нарисуйте свой собственный процессор] Дизайн контроллера (2)

🌷1. Цель прохождения уровней.

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

(1) освоить логику реализации однобитного полного сумматора и логику реализации многобитной управляемой схемы сложения и вычитания;

(2) Быть знакомым с основными функциями платформы Logisim и уметь реализовывать в Logisim многоразрядные управляемые схемы сложения и вычитания.

🌼Уровень 2: Оригинальный код однобитного множителя

(1) Овладеть основными принципами операции однобитового умножения исходного кода;

(2) Быть опытным в использовании регистровых схем Logisim и уметь спроектировать и реализовать 8*8-битный беззнаковый умножитель на платформе Logisim.

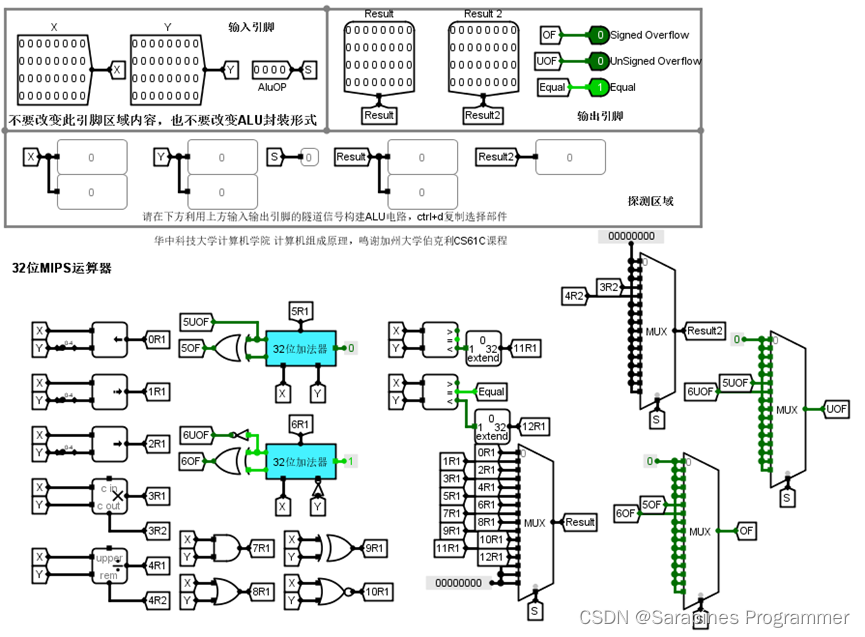

🌼Уровень 3: Проектирование оператора MIPS

(1) Понять базовую структуру блока арифметико-логических операций (АЛУ) и освоить использование различных вычислительных компонентов в Logisim;

(2) Быть знакомым с использованием мультиплексоров и уметь использовать 32-битный сумматор, выполненный в вышеупомянутом эксперименте, и арифметические компоненты в Logisim для построения блока ALU с заданными характеристиками.

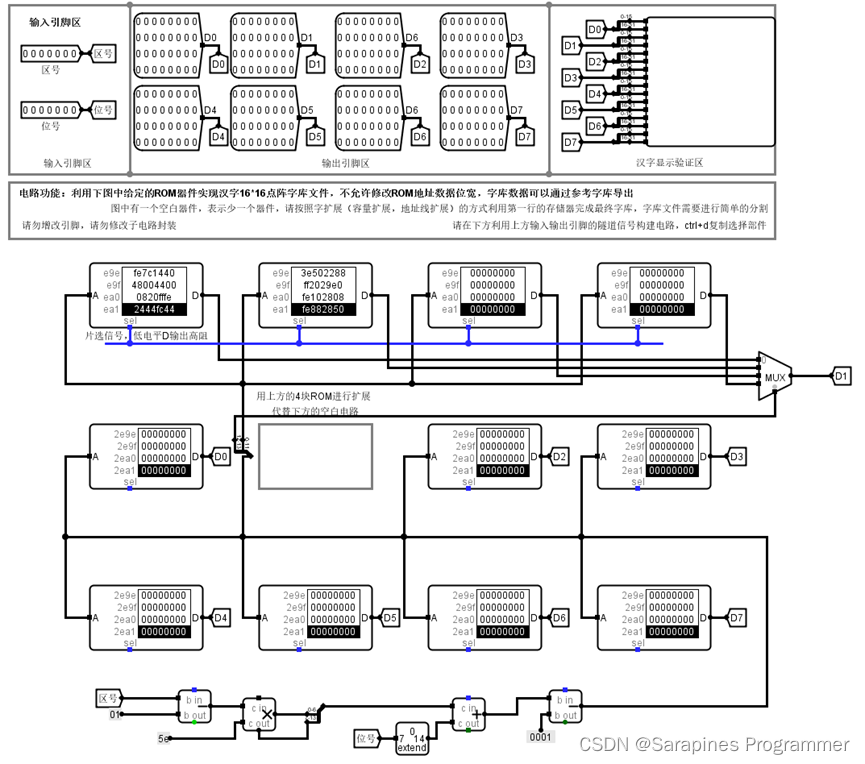

🌼Уровень 4: Эксперимент по расширению чипа памяти библиотеки китайских иероглифов

(1) Понимать основные принципы расширения битов и слов в системах хранения данных;

(2) Использовать соответствующие принципы для решения проблемы расширения хранилища библиотеки китайских символов в эксперименте и иметь возможность заполнить ее правильными данными шрифтов.

🌼Уровень 5: Регистрация дизайна файла

(1) Понять основные концепции файлов регистров MIPS;

(2) Быть знакомым с использованием компонентов Logisim, таких как мультиплексоры, декодеры и демультиплексоры, и использовать соответствующие компоненты для создания файлов регистров MIPS.

🌼Уровень 6: Проектирование оперативной памяти MIPS

(1) Понять основные концепции адресов основной памяти и основные идеи расширения памяти;

(2) Используйте соответствующие принципы для создания подсистемы хранения, которая может одновременно поддерживать доступ к байтам, полусловам и словам.

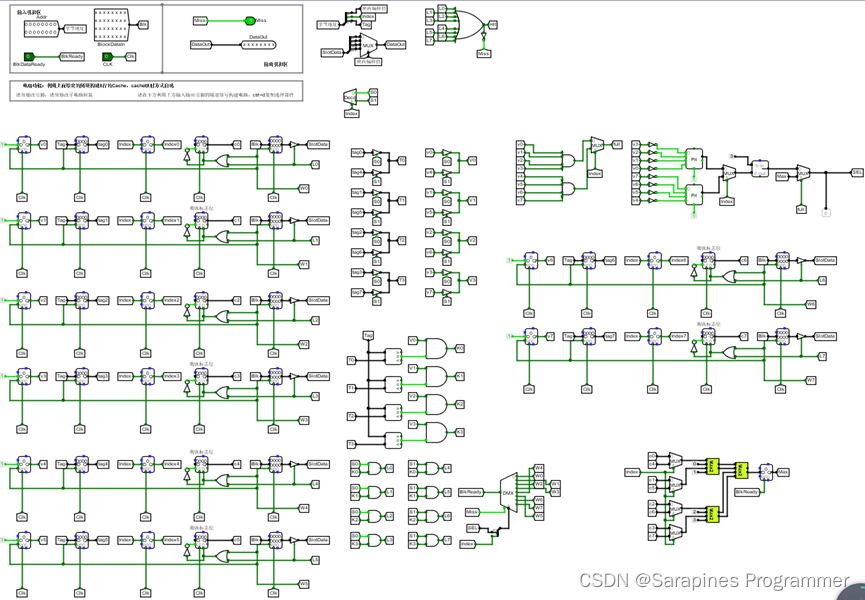

🌼Уровень 7: конструкция кэша с 4-сторонним групповым подключением

(1) Освоить три ключевые технологии реализации кэша: поиск данных, сопоставление адресов и алгоритм замены;

(2) Быть знакомым с использованием декодеров, мультиплексоров и регистров, а также уметь использовать цифровые логические схемы для реализации механизмов кэширования на платформе Logisim в соответствии с различными стратегиями отображения.

🌼Уровень 8: Проектирование однотактного процессора MIPS

(1) Освоить основные принципы проектирования контроллеров, использовать принципы проектирования проводных контроллеров, а также спроектировать и внедрить однотактный процессор MIPS на платформе Logisim.

🌼Уровень 9: Разработка логики передачи адреса микропрограммы.

(1) Понять основные принципы ветвления микропрограмм в микропрограммных контроллерах, что требует умения проектировать логику передачи микроадресов.

🌼Уровень 10: Проектирование процессора микропрограммы MIPS

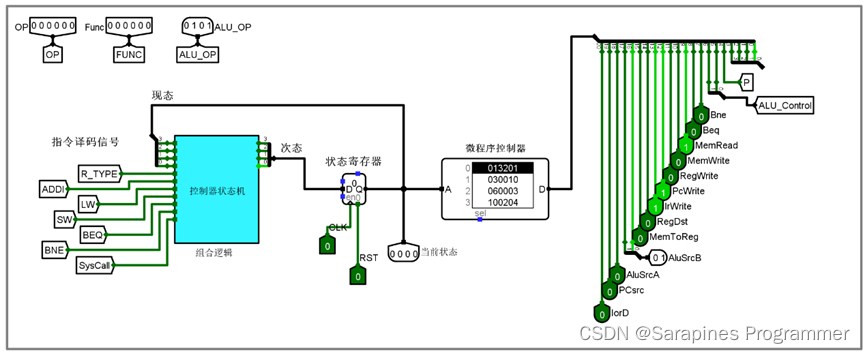

(1) Овладеть основными принципами проектирования микропрограммных контроллеров и уметь использовать принципы проектирования микропрограммных контроллеров для проектирования и реализации многотактных процессоров MIPS.

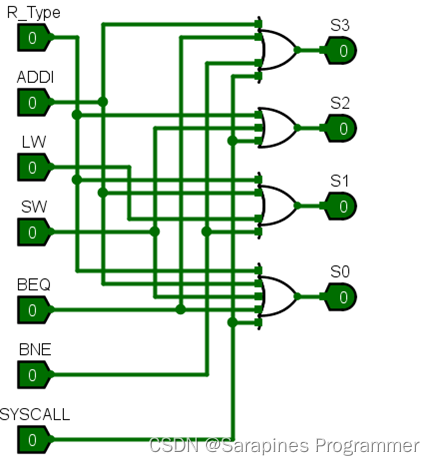

🌼Уровень 11: Проектирование конечного автомата аппаратного контроллера

(1) Понимать основные принципы конечного автомата FSM в проводных контроллерах и уметь проектировать логику конечного автомата контроллера.

🌼Уровень 12: Проектирование процессора многоциклового аппаратного контроллера MIPS (программа секвенирования)

(1) Понимать основные принципы многотактных процессоров MIPS и уметь использовать принципы проектирования проводных контроллеров для проектирования и реализации многотактных процессоров MIPS.

Рисунок 4.2-4

🌷2. Решающий уровень контент.

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

Откройте файл alu.circ в симуляторе Logisim и используйте упакованный полный сумматор в соответствующей подсхеме для разработки 8-битной последовательной управляемой схемы сложения и вычитания. Пользователь может напрямую использовать соответствующую метку туннеля в схеме, где X и. Y — два входных числа, Sub — сигнал управления сложением и вычитанием, S — выход результата операции, Cout — выход переноса, а OF — бит переполнения операции со знаком.

🌼Уровень 2: Оригинальный код однобитного множителя

В исходную подсхему однобитового умножителя в файле alu.circ добавляются схема управления и путь данных, чтобы схема могла автоматически выполнять однобитовую операцию умножения 8-битных беззнаковых чисел. Затем установите начальное значение вывода, а затем запустите часы для автоматической имитации, и схема сможет автоматически завершить операцию. Операция завершена, и результат передается на выходной вывод. В конце операции экспериментальная структура показана на Рисунке 4.2-1:

Рисунок 4.2-1

🌼Уровень 3: Проектирование оператора MIPS

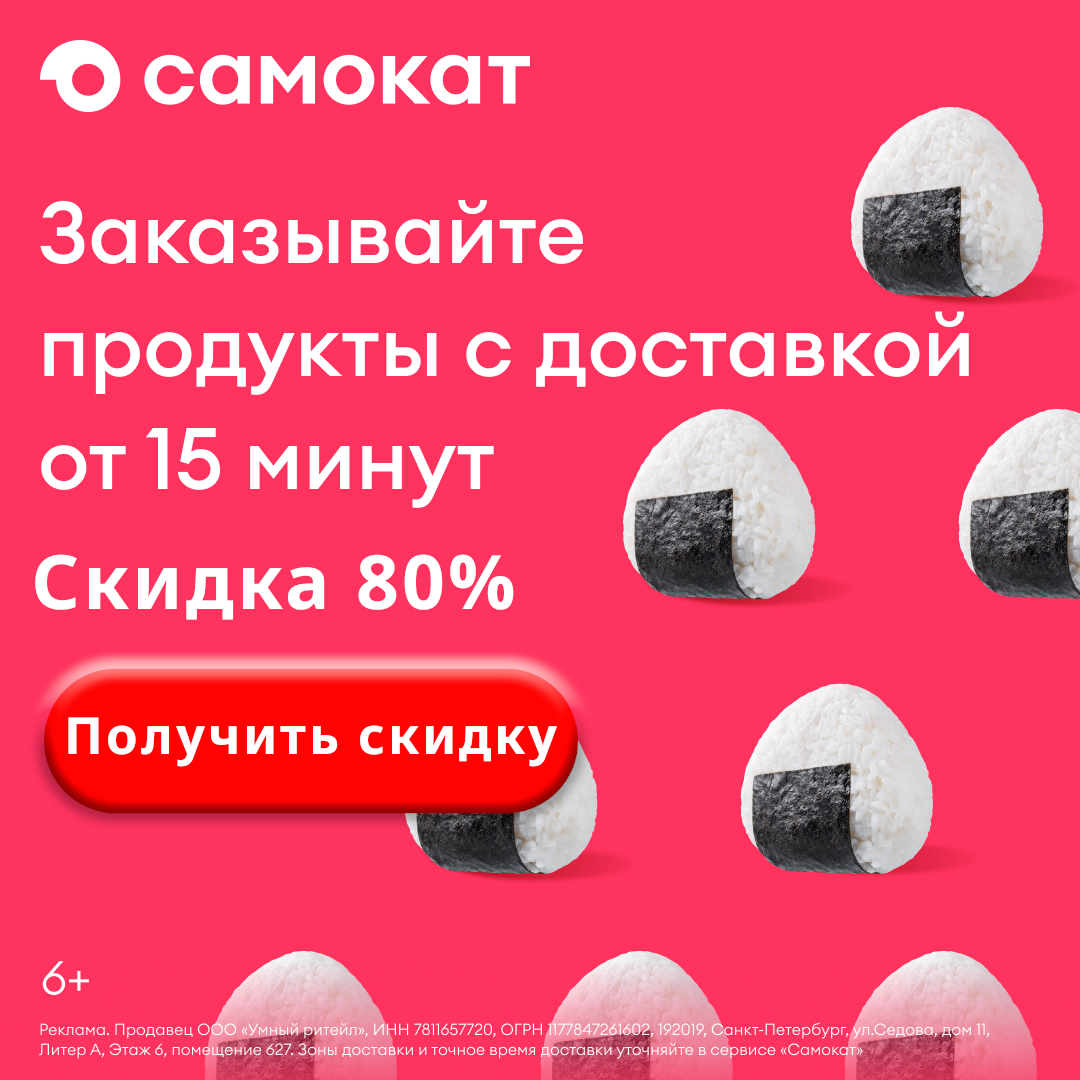

Используйте 32-битный сумматор, инкапсулированный в предыдущем эксперименте, и существующие вычислительные компоненты платформы Logisim, чтобы создать 32-битный блок арифметических логических операций (отключите сумматор и вычитатель, поставляемые с системой Logisim), который может поддерживать арифметическое сложение. вычитание, умножение, деление, логическое И, ИЛИ, НЕ, операция исключающее ИЛИ, логический сдвиг влево, логический сдвиг вправо, арифметическая операция сдвига вправо, поддерживает общие флаги состояния программы (переполнение со знаком OF, переполнение без знака UOF, результат равен), ALU Функции, а также входные и выходные контакты показаны в таблице ниже. Подробно протестируйте самокомплектный АЛУ в основной схеме и проанализируйте преимущества и недостатки оператора. Схема эксперимента показана на рисунке 4.2-2:

Рисунок 4.2-2

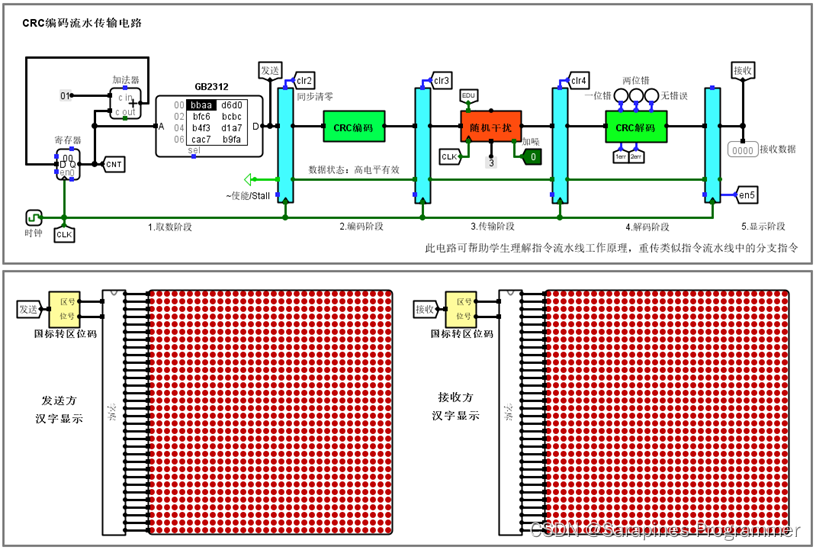

🌼Уровень 4: Эксперимент по расширению чипа памяти библиотеки китайских иероглифов

Доступны следующие компоненты ПЗУ: 4 4K*32-битных ПЗУ и 7 16K*32-битных ПЗУ. Создайте матричную библиотеку китайских символов размером 16K*16 с кодировкой китайских символов GB2312 на платформе Logisim. Вход схемы — это код области китайских символов и номер бита, а выход схемы — 8 × 32 бита (16 КБ * 16 = 256 бит информации о решетке. Подробную информацию см. в файле Storage.circ в файле проекта). файлы, соответствующие коду региона и номеру бита кода региона китайского символа. Средняя область представляет собой восемь 32-битных выходных контактов, которые могут одновременно обеспечивать 256-битное матричное отображение информации китайского символа. — это фактическая область отображения китайских иероглифов. Дисплей нормальный. Упаковка подсхемы шрифта завершена, не изменяйте ее, чтобы не повлиять на последующую функцию автоматического тестирования.

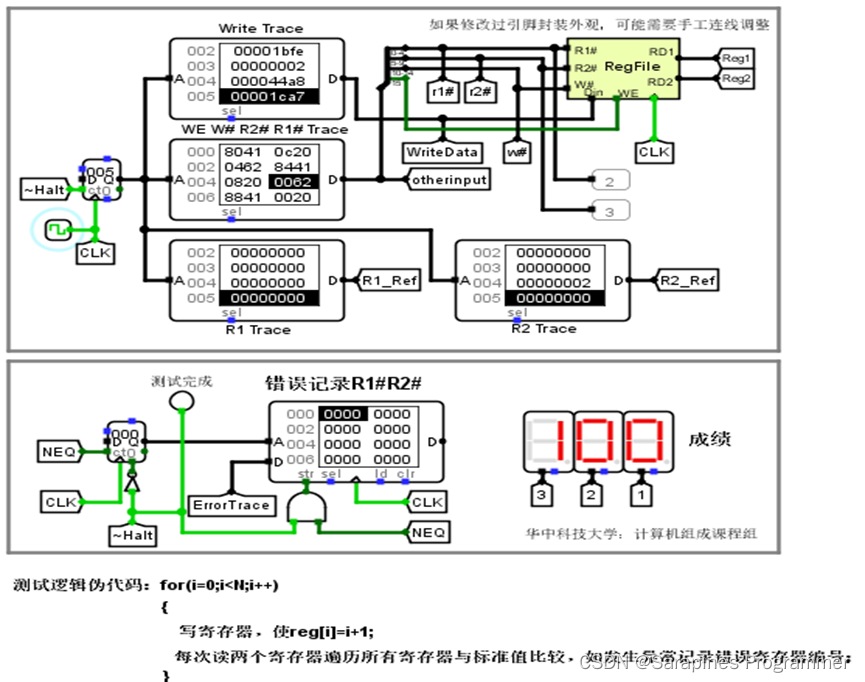

🌼Уровень 5: Регистрация дизайна файла

Используйте платформу Logisim для создания упрощенного файла регистров MIPS, который содержит четыре 32-битных регистра.

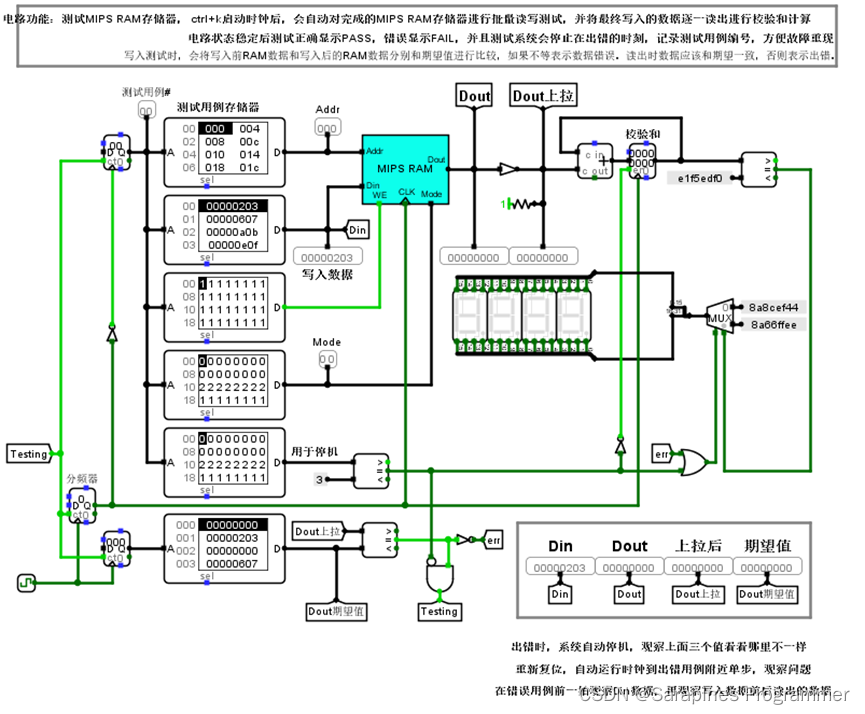

🌼Уровень 6: Проектирование оперативной памяти MIPS

Компонент RAM в Logisim может обеспечивать только фиксированную разрядность адреса, а вывод данных может обеспечивать только фиксированную разрядность данных. Он не может поддерживать три режима доступа: байт/полуслово/слово одновременно во время доступа. использование четырех 8-битных компонентов RAM. Расширена и разработана 32-битная память, которую можно читать и записывать в 8-битном, 16-битном или 32-битном формате.

🌼Уровень 7: конструкция кэша с 4-сторонним групповым подключением

Схема автоматического тестирования системы кэширования, разработанная в Logisim. Чтобы упростить экспериментальную схему, все модули кэша здесь являются кэшами только для чтения (аналогично кэшам инструкций) и не имеют механизма записи. Часть счетчика и памяти на левой стороне схемы будет генерировать последовательности доступа к адресу одну за другой к модулю кэша, управляемому тактовым сигналом. Конец включения модуля счетчика управляется сигналом попадания. Если он отсутствует, конец включения недействителен, и счетчик не рассчитывает, пока система запланирует блок, содержащий запрошенные данные, из вторичной памяти. кэш, прежде чем он сможет продолжить подсчет. Обмен блоками данных осуществляется между кэшем и вторичной памятью посредством логики обмена блоками. Поскольку вторичная память работает намного медленнее, чем кэш, для завершения обмена блоками требуется несколько тактов. Модуль кэша определяет логику используемого блока данных. Ready — это сигнал blkready. Действительный, когда сигнал действителен и тактовый сигнал поступает, кэш загружает данные блока из порта BlkDin в соответствующий буфер строки кэша. В это время данные кэша попадают в данные кэша. напрямую выводит данные запроса, разблокирует конец включения счетчика и продолжает доступ к следующему адресу.

Схема автоматического тестирования будет извлекать адреса основной памяти из памяти трассировки один за другим для доступа к системе хранения, а также извлекать данные один за другим из модуля кэша и отправлять их в схему расчета контрольной суммы для расчета контрольной суммы. значение счетчика равно 256, работа схемы будет остановлена. В это время все данные о скорости доступа к хранилищу будут отображаться на светодиодной цифровой трубке в правом верхнем углу. Основная задача этого эксперимента — разработать подсхему кэша, основной модуль схемы.

В сочетании с описанием функции вывода реализован полностью ассоциативный модуль кэша. Модуль кэша включает в себя в общей сложности 8 строк кэша, и каждый блок данных содержит 4 байта 32-битных данных.

🌼Уровень 8: Проектирование однотактного процессора MIPS

Используя арифметический блок эксперимента, арифметический блок, регистровый файл, систему хранения и другие компоненты, встроенные в эксперимент с системой хранения, а также другие функциональные компоненты в Logisim, был построен 32-битный однотактный процессор MIPS CPU.

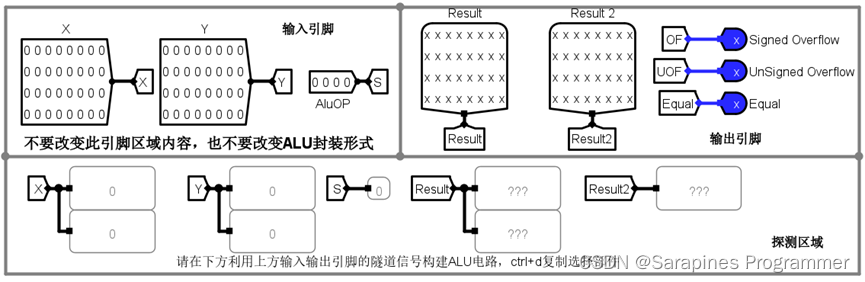

🌼Уровень 9: Разработка логики передачи адреса микропрограммы.

Рисунок 4.2-3

Спроектируйте приведенную выше схему для генерации адреса входа микропрограммы на основе сигнала декодирования инструкций.

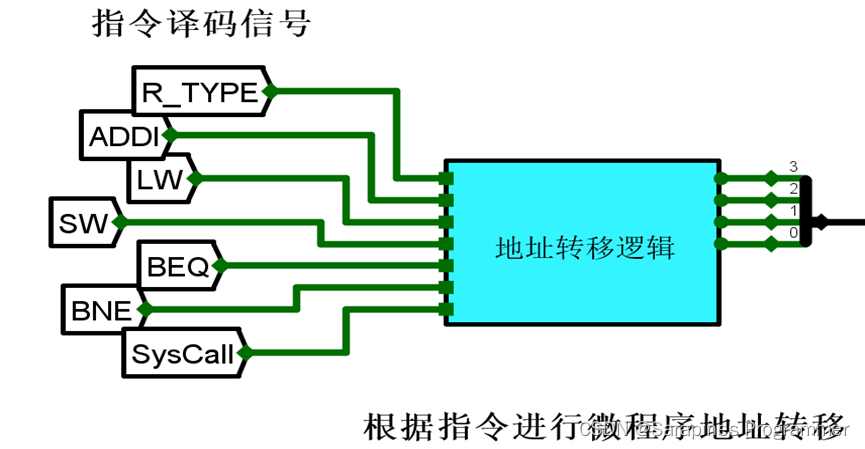

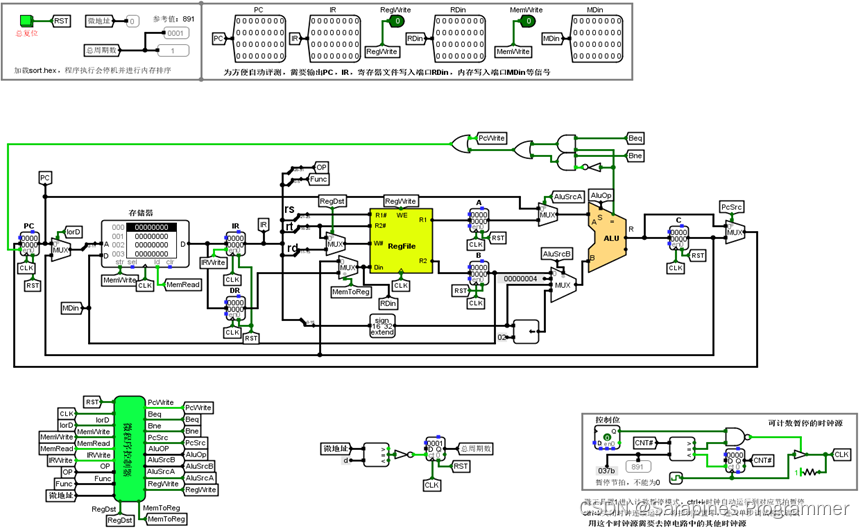

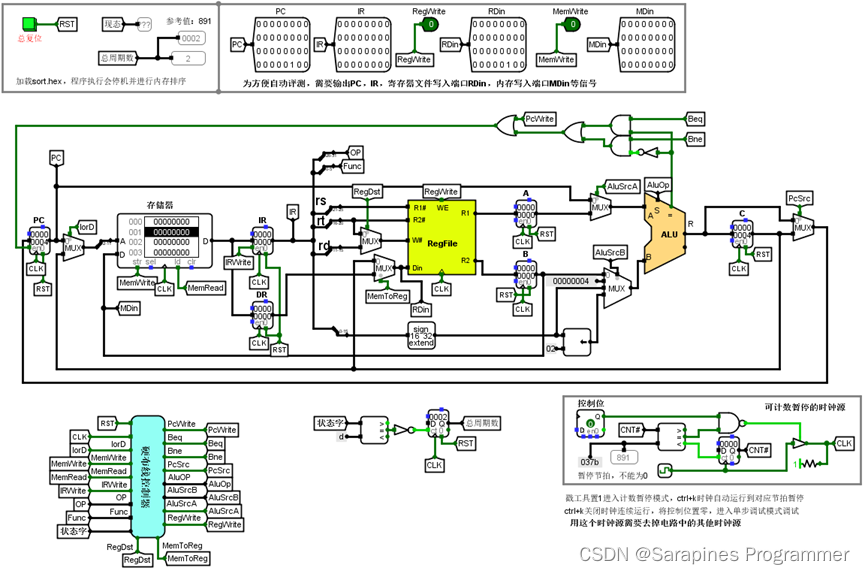

🌼Уровень 10: Проектирование процессора микропрограммы MIPS

По сравнению с трактом данных многотактного процессора MIPS для реализации контроллера используется метод проектирования микропрограммного контроллера, и создается многотактный процессор MIPS, который необходим для поддержки 8 основных инструкций MIPS, указанных в таблице. наконец разработанный и реализованный процессор MIPS может провести эксперимент. Тестовая программа пузырьковой сортировки sort.asm в пакете автоматически записывает 16 данных в виде слов от 0 до 15 в память данных, а затем использует пузырьковую сортировку для сортировки данных в возрастающем порядке. Экспериментальная схема должна иметь возможность автоматически подсчитывать количество инструкций и количество тактовых циклов.

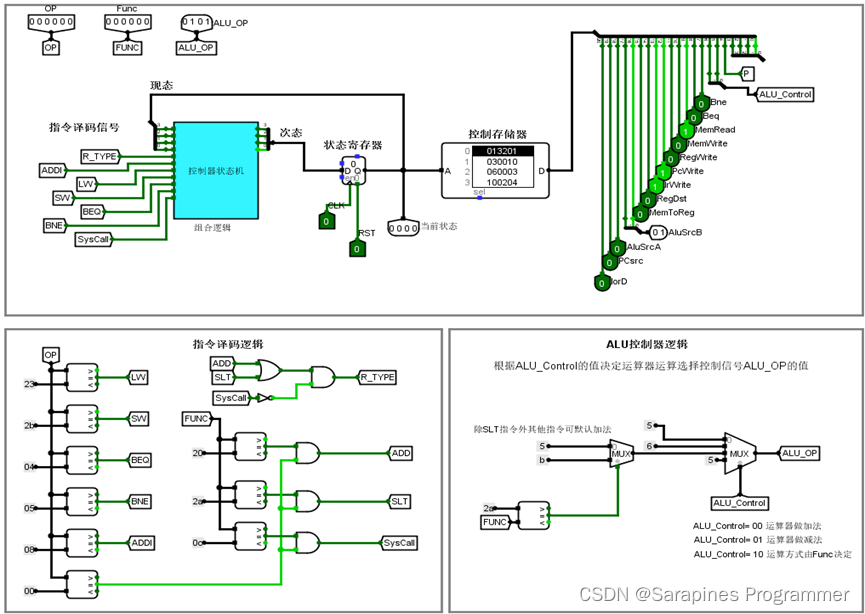

🌼Уровень 11: Проектирование конечного автомата аппаратного контроллера

Откройте файл data.circ в экспериментальном пакете в logisim и завершите схему обнаружения ошибок четности в соответствующей схеме. Вход: 17-битный контрольный код, контрольная цифра хранится в старшем бите. Выход: 16-битные исходные данные, 1 бит обнаружения ошибок. Определение входа и выхода экспериментальной схемы. Обратите внимание, что каждый бит 17-битного контрольного кода; проходит через отвод. Устройство вводится с помощью туннельных меток, что удобно для использования при проведении экспериментов.

🌼Уровень 12: Проектирование процессора многоциклового аппаратного контроллера MIPS (программа секвенирования)

(1) Создайте основные функциональные компоненты и пути к данным.

Основные функциональные компоненты, необходимые для разработки многотактного процессора MIPS, разработаны на платформе Logisim. Файл регистров использует стандартную библиотеку cs3410. Арифметический оператор может использовать либо собственный арифметический оператор в арифметическом эксперименте, либо стандартную библиотеку. Модуль ALU создает многоцикловый путь данных процессора MIPS и в конечном итоге соединяет различные функциональные компоненты для формирования пути данных.

Рисунок 4.2-4

(2) Создайте проводной контроллер.

Создайте аппаратный контроллер на основе заданного конечного автомата.

Рисунок 4.2-5

Требуется поддержка 8 основных инструкций.

Рисунок 4.2-6

Рисунок 4.2-7

🌷3. Шаги для прохождения уровня.

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

Рисунок 4.2-8

🌼Уровень 2: Оригинальный код однобитного множителя

Рисунок 4.2-9

🌼Уровень 3: Проектирование оператора MIPS

Рисунок 4.2-10

🌼Уровень 4: Эксперимент по расширению чипа памяти библиотеки китайских иероглифов

Рисунок 4.2-11

🌼Уровень 5: Регистрация дизайна файла

Рисунок 4.2-12

Рисунок 4.2-13

🌼Уровень 6: Проектирование оперативной памяти MIPS

Рисунок 4.2-14

Рисунок 4.2-15 тест

🌼Уровень 7: конструкция кэша с 4-сторонним групповым подключением

Рисунок 4.2-16

🌼Уровень 8: Проектирование однотактного процессора MIPS

Рисунок 4.2-17

🌼Уровень 9: Разработка логики передачи адреса микропрограммы.

Рисунок 4.2-18

🌼Уровень 10: Проектирование процессора микропрограммы MIPS

Рисунок 4.2-19

🌼Уровень 11: Проектирование конечного автомата аппаратного контроллера

Рисунок 4.2-20

🌼Уровень 12: Проектирование процессора многоциклового аппаратного контроллера MIPS (программа секвенирования)

Рисунок 4.2-21

🌷4. Краткое описание прорыва уровня.

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

1. Параллельный сумматор: Выход переноса связан только с наименьшим входом переноса C0 (Cn=Gn+PnGn-1+PnPn-1Gn-2+PnPn-1Pn-2Gn-3…+PnPn-1…P1C0), а не опираясь на перенос младшего порядка (Cn= Gn + Pn Cn-1).

2. Аппаратная реализация: управляемый противофазный вентиль XOR. С помощью вентиля XOR Sub может реализовать Y и не-Y, установив значение от 0 до 1, а также может использоваться в качестве входного сигнала 0 и 1 для Cin. OF — это флаг переполнения, а выход переполнения равен 1 (здесь 1 — это). высокий уровень). Аппаратная реализация для определения переполнения операций сложения и вычитания знаковых чисел: перенос старшего бита ⊕ перенос знакового бита, 1 указывает на переполнение.

🌼Уровень 2: Оригинальный код однобитного множителя

1. Контроль количества перемещений: Используйте аппаратную реализацию счетчика + компаратора Просто управляйте правым сдвигом 9 раз (в вопросе есть подсказка). При LOAD = 0 подается сигнал 1; правый регистр и другой. Когда =0, регистр справа обновляется в соответствии со смещением.

2. Реализация смещения: используются четыре группы верхних и нижних разделителей шириной 8 бит. Старший бит слева — младший бит справа. Произведение сдвигается вправо. Самый старший бит получается при переносе. вход восьмибитного сумматора. Всплывающие данные правого сдвига используются для развертывания селектора данных. Время равно +0 или +a.

🌼Уровень 3: Проектирование оператора MIPS

1. Проект таможенного оформления: используйте 32-битный сумматор, включенный в предыдущий эксперимент, и существующие вычислительные компоненты платформы logisim, чтобы создать 32-битный сумматор. Блок битовых арифметических логических операций посредством мультиплексной обработки выполняет сложение, вычитание, умножение, деление, логические операции И, ИЛИ, НЕ, исключающее ИЛИ, логический сдвиг влево, логический сдвиг вправо и арифметический сдвиг вправо соответственно и получает результаты. результат, соответствующий выбранному методу операции, передается в Result через мультиплексор. Во время операций умножения и деления результат старшего порядка или остаток передается в Result2. В других случаях результат Result2 равен 0.

2. Используйте сдвигатели для реализации логических операций сдвига влево, сдвига вправо и арифметических операций сдвига вправо.

🌼Уровень 4: Эксперимент по расширению чипа памяти библиотеки китайских иероглифов

1. Конструкция таможенного оформления: память кода глифа для поиска с использованием кода города и номера бита, логическая схема преобразования кода города: (код города-1) * 94 + номер бита-1, а для китайского кода глифа требуется 3232 = 1024 бита, память ПЗУ в logisim До 32 бит надо поразрядно расширить, тогда 1024/32 = 32 штуки по 16К32 бит нужно ПЗУ, в соответствии с экспериментальными требованиями, просто реализует стандартную библиотеку китайских символов с точечной матрицей 16 * 16, 256/32 = 8 частей ПЗУ размером 16 КБ × 32 бит, отправляет логический адрес на восемь адресных терминалов ПЗУ для одновременного выполнения, в соответствии с Для экспериментальных задач используйте четыре части. Малая емкость (4 КБ × 32 бита). ПЗУ представляет собой расширенное слово для замены исходной памяти (16 КБ × 32 бита).

2. Количество адресных строк в ПЗУ размером 4Кх32 бита составляет 12 бит, а количество адресных строк в ПЗУ размером 16Кх32 бита — 14 бит. Соедините адреса четырех ПЗУ малой емкости параллельно и поместите. сегмент параллельного адреса на клемме 0 разветвителя -11, затем подключите 1 через разветвитель. Два старших бита 4-битной адресной линии (концы 12–13) подключены к входному концу декодера 2–4, а выходной конец декодера подключен к выходному концу четырех ПЗУ. 4 сегмента данных ПЗУ малой емкости подключены параллельно к D1 для завершения расширения слова.

🌼Уровень 5: Регистрация дизайна файла

1. Схема таможенного оформления: значение регистра № 0 всегда равно нулю, а 32-битная длина данных константы 0 используется для доступа к входным данным регистра № 0. Туннелируйте Din к оставшимся трем регистровым входам. Демультиплексор используется для завершения ввода разрешения WE в четыре регистра, а W# является его интерфейсом селектора. Чтобы упростить экспериментальный процесс, R1#R2#W# имеет ширину всего 2 бита, что также удобно для демультиплексирования. разрядность подключенного устройства. Подключите CLK к интерфейсу часов из 4 регистров. Используйте мультиплексор для завершения вывода регистров RD1 и RD2, RD1 и RD2 — это значения R1# и R2#. Конец выбора подключен к R1# и R2#. R1# и R2# обозначают номера первого и второго регистров чтения соответственно.

🌼Уровень 6: Проектирование оперативной памяти MIPS

1. 00 представляет доступ к слову, 01 представляет доступ к 1 байту (т. е. доступ к одному байту), а 10 представляет доступ к 2 байтам (т. е. доступ к полуслову).

2. В эксперименте слово имеет длину 32 бита, один байт — 8 бит, а половина слова — 16-битный адрес. Два младших бита игнорируются при доступе к слову; младший бит игнорируется при доступе к полуслову. предпоследний бит — это выбор чипа; во время доступа к байтам требуется второй бит. Сделайте выбор фильма. Чтобы предотвратить перезапись данных в блоке хранения, необходимо определить, какая из четырех ячеек памяти хранится, на основе режима и двух младших битов.

🌼Уровень 7: конструкция кэша с 4-сторонним групповым подключением

Схема таможенного оформления: разделите кэш на 4 пути, чтобы размер каждого пути составлял 8 КБ. Размер строки кэша составляет 32 байта, поэтому всего имеется 256 групп (8 КБ/32 байта). Поскольку размер строки кэша составляет 32 байта, для смещения требуется 5 бит. Всего групп 256, поэтому для индекса требуется 8 бит, а остальное — часть тега, которая занимает 35 бит.

🌼Уровень 8: Проектирование однотактного процессора MIPS

1. Поймите, что однотактный процессор MIPS означает, что выполнение одной инструкции завершается за один такт, а затем начинается выполнение следующей инструкции, то есть одна инструкция завершается за один такт.

2. "может появиться" not find jar library cs3410.jar", из-за cs3410.jar и тестплатформасередина cs3410.jar Путь другой, вы можете изменить локальный cs3410.jar первый шаг в cpu.circ Находясь в том же каталоге, откройте cpu.circ,logisim Будет сообщено, что его невозможно найти. cs3410.jar, перенаправление в тот же каталог cs3410.jar, сохраните и выйдите, а затем повторно загрузите текстовое содержимое схемы, чтобы решить проблему.

🌼Уровень 9: Разработка логики передачи адреса микропрограммы.

1. Логическая схема передачи адреса используется для генерации адреса следующей микрокоманды и в основном состоит из двухуровневых вентилей И и вентилей ИЛИ. Сигналы данных, необходимые для логики передачи адреса, включают в себя: последующие микроадреса μA3-μA0, бит дискриминации P1 и коды операций команд IR7-IR5.

2. Регистр микроадреса 74LS175 содержит адрес микрокоманды для управляющей памяти. Когда CLR = 0, регистр микроадреса очищается и микропрограмма выполняется с адреса управляющей памяти 00H. Логика передачи адреса генерирует адрес следующей микрокоманды. Если сигналы синхронизации поступают непрерывно, микро- инструкции также будут выводиться в определенном порядке.

🌼Уровень 10: Проектирование процессора микропрограммы MIPS

1. Идея проекта: в подсхеме многоциклового ЦП (микропрограммы) MIPS постройте путь данных ЦП ПК, MEM, IR, DR, RegFile, ALU и контроллер.

2. Реализация логики передачи адреса микропрограммы может быть известна из диаграммы перехода состояний команды.

🌼Уровень 11: Проектирование конечного автомата аппаратного контроллера

Идея дизайна: во-первых, проанализировать последовательность микроопераций цикла выполнения, цикла косвенного адреса, цикла выполнения и цикла прерывания всех инструкций. Последовательность микроопераций цикла выполнения, цикла косвенного адреса и цикла прерывания является общей для всех команд. все инструкции и выполнение различных инструкций. Циклы различаются, затем выбирают режим управления ЦП. Каждая инструкция состоит из соответствующей последовательности микроопераций. Затем первый шаг последовательности микроопераций делится на такты каждой. Нарисованы машинный цикл и все диаграммы микроопераций машинного цикла, тактов и инструкций, используйте это для записи комбинационного логического выражения каждой микрооперации и используйте это для проектирования схемы.

🌼Уровень 12: Проектирование процессора многоциклового аппаратного контроллера MIPS (программа секвенирования)

По сравнению с однотактным ЦП конструкция проводного контроллера многотактного ЦП MIPS только заменяет контроллер микроинструкций на проводной контроллер, но другие части не изменились, поэтому часть пути данных такая же, как и у Многотактный процессор MIPS контроллера микроинструкций.

Учебное пособие по Jetpack Compose для начинающих, базовые элементы управления и макет

Код js веб-страницы, фон частицы, код спецэффектов

【новый! Суперподробное】Полное руководство по свойствам компонентов Figma.

🎉Обязательно к прочтению новичкам: полное руководство по написанию мини-программ WeChat с использованием программного обеспечения Cursor.

[Забавный проект Docker] VoceChat — еще одно приложение для мгновенного чата (IM)! Может быть встроен в любую веб-страницу!

Как реализовать переход по странице в HTML (html переходит на указанную страницу)

Как решить проблему зависания и низкой скорости при установке зависимостей с помощью npm. Существуют ли доступные источники npm, которые могут решить эту проблему?

Серия From Zero to Fun: Uni-App WeChat Payment Practice WeChat авторизует вход в систему и украшает страницу заказа, создает интерфейс заказа и инициирует запрос заказа

Серия uni-app: uni.navigateЧтобы передать скачок значения

Апплет WeChat настраивает верхнюю панель навигации и адаптируется к различным моделям.

JS-время конвертации

Обеспечьте бесперебойную работу ChromeDriver 125: советы по решению проблемы chromedriver.exe не найдены

Поле комментария, щелчок мышью, специальные эффекты, js-код

Объект массива перемещения объекта JS

Как открыть разрешение на позиционирование апплета WeChat_Как использовать WeChat для определения местонахождения друзей

Я даю вам два набора из 18 простых в использовании фонов холста Power BI, так что вам больше не придется возиться с цветами!

Получить текущее время в js_Как динамически отображать дату и время в js

Вам необходимо изучить сочетания клавиш vsCode для форматирования и организации кода, чтобы вам больше не приходилось настраивать формат вручную.

У ChatGPT большое обновление. Всего за 45 минут пресс-конференция показывает, что OpenAI сделал еще один шаг вперед.

Copilot облачной разработки — упрощение разработки

Микросборка xChatGPT с низким кодом, создание апплета чат-бота с искусственным интеллектом за пять шагов

CUDA Out of Memory: идеальное решение проблемы нехватки памяти CUDA

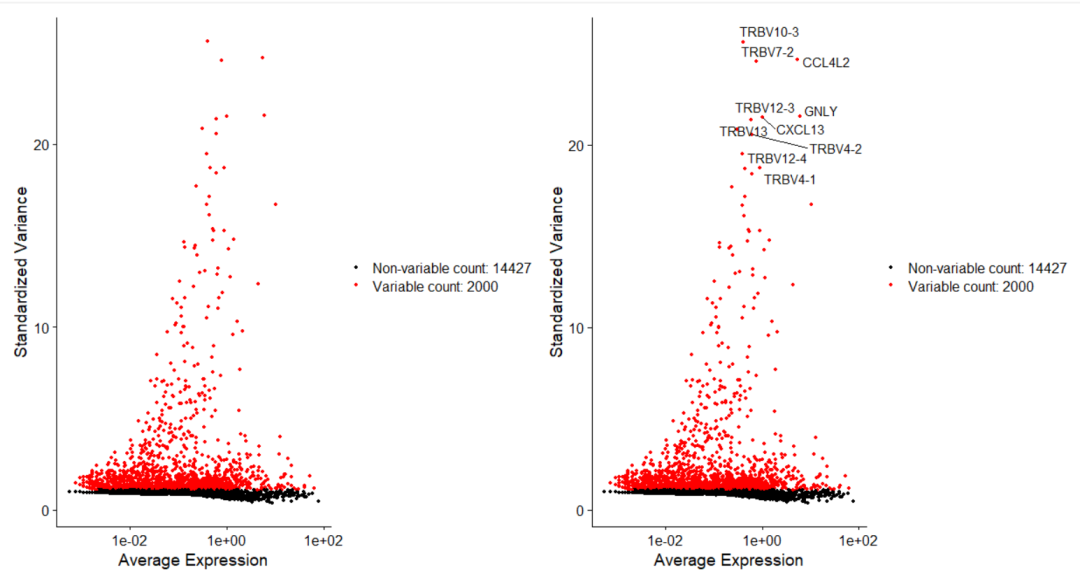

Анализ кластеризации отдельных ячеек, который должен освоить каждый&MarkerгенетическийВизуализация

vLLM: мощный инструмент для ускорения вывода ИИ

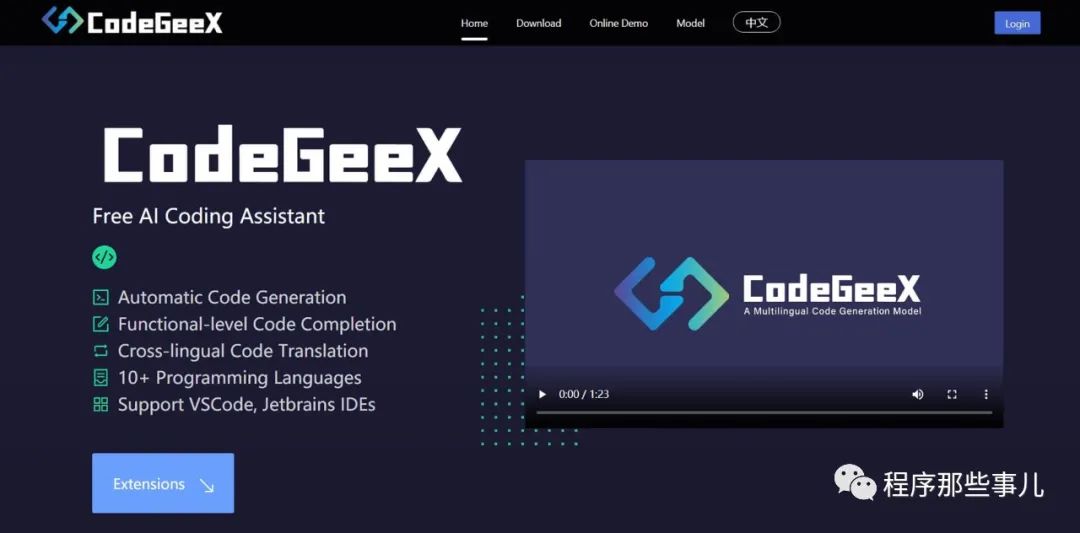

CodeGeeX: мощный инструмент генерации кода искусственного интеллекта, который можно использовать бесплатно в дополнение к второму пилоту.

Машинное обучение Реальный бой LightGBM + настройка параметров случайного поиска: точность 96,67%

Бесшовная интеграция, мгновенный интеллект [1]: платформа больших моделей Dify-LLM, интеграция без кодирования и встраивание в сторонние системы, более 42 тысяч звезд, чтобы стать свидетелями эксклюзивных интеллектуальных решений.

LM Studio для создания локальных больших моделей

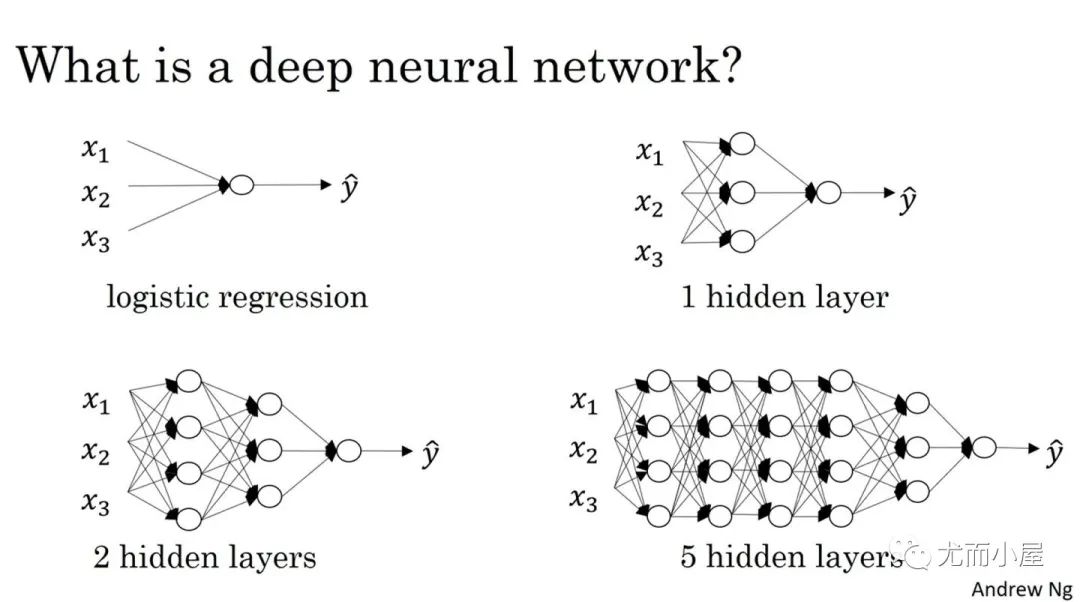

Как определить количество слоев и нейронов скрытых слоев нейронной сети?