[Нарисуйте свой собственный процессор] Дизайн контроллера (1)

🌷1. Цель

🌼Уровень 1: Проектирование однотактного процессора MIPS

(1) Освоить основные принципы проектирования контроллеров, использовать принципы проектирования проводных контроллеров, а также спроектировать и внедрить однотактный процессор MIPS на платформе Logisim.

🌼Уровень 2: Разработка логики передачи адреса микропрограммы.

(1) Понять основные принципы ветвления микропрограмм в микропрограммных контроллерах, что требует умения проектировать логику передачи микроадресов.

🌼Уровень 3: Проектирование процессора микропрограммы MIPS

(1) Овладеть основными принципами проектирования микропрограммных контроллеров и уметь использовать принципы проектирования микропрограммных контроллеров для проектирования и реализации многотактных процессоров MIPS.

🌼Уровень 4: Проектирование конечного автомата аппаратного контроллера

(1) Понимать основные принципы конечного автомата FSM в проводных контроллерах и уметь проектировать логику конечного автомата контроллера.

🌼Уровень 5: Проектирование ЦП многотактного аппаратного контроллера MIPS (программа секвенирования)

(1) Понимать основные принципы многотактных процессоров MIPS и уметь использовать принципы проектирования проводных контроллеров для проектирования и реализации многотактных процессоров MIPS.

🌷2. Решающий уровень контент.

🌼Уровень 1: Проектирование однотактного процессора MIPS

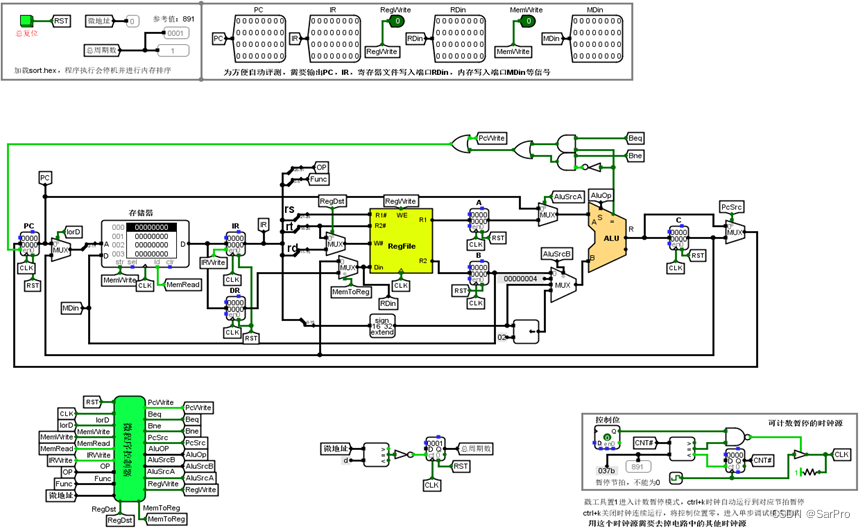

Используя арифметический блок эксперимента, арифметический блок, регистровый файл, систему хранения и другие компоненты, встроенные в эксперимент с системой хранения, а также другие функциональные компоненты в Logisim, был построен 32-битный однотактный процессор MIPS CPU.

🌼Уровень 2: Разработка логики передачи адреса микропрограммы.

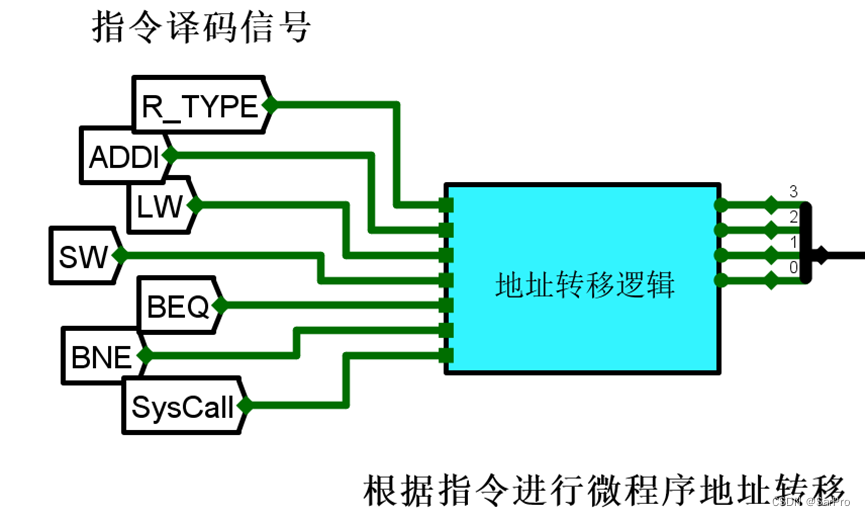

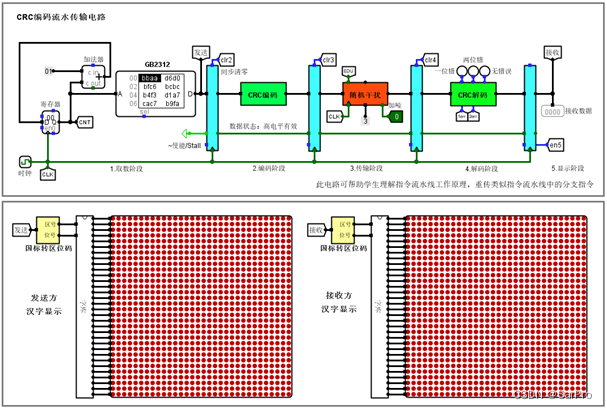

Разработайте следующую схему для генерации адреса записи микропрограммы на основе сигнала декодирования инструкций.

Рисунок 4.1-1

🌼Уровень 3: Проектирование процессора микропрограммы MIPS

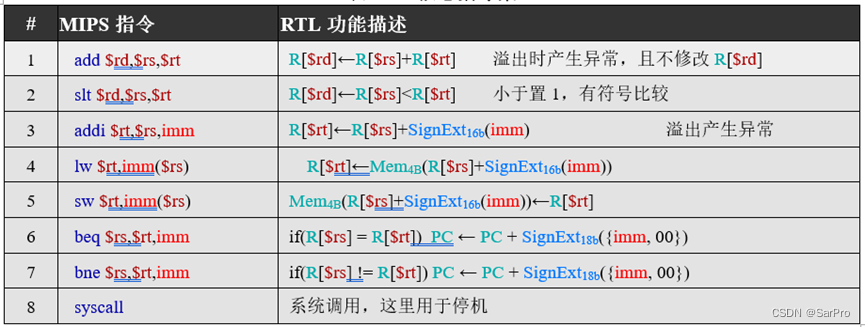

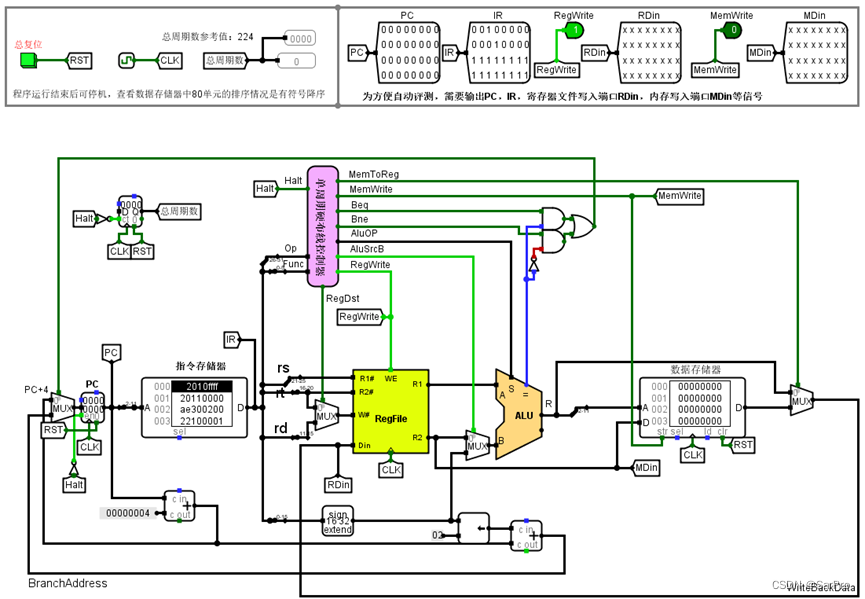

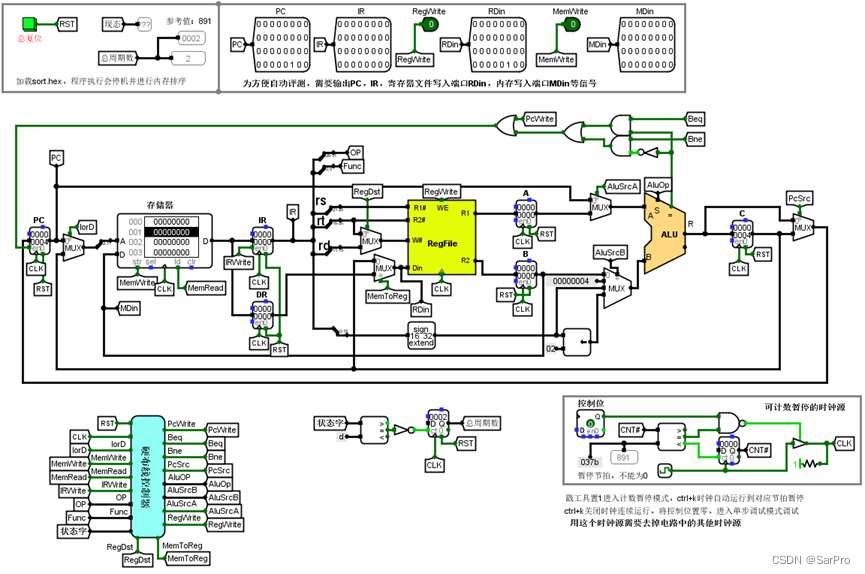

По сравнению с трактом данных многотактного процессора MIPS для реализации контроллера используется метод проектирования микропрограммного контроллера, и создается многотактный процессор MIPS, который необходим для поддержки 8 основных инструкций MIPS, указанных в таблице. наконец разработанный и реализованный процессор MIPS может провести эксперимент. Тестовая программа пузырьковой сортировки sort.asm в пакете автоматически записывает 16 данных в виде слов от 0 до 15 в память данных, а затем использует пузырьковую сортировку для сортировки данных в возрастающем порядке. Экспериментальная схема должна иметь возможность автоматически подсчитывать количество инструкций и количество тактовых циклов.

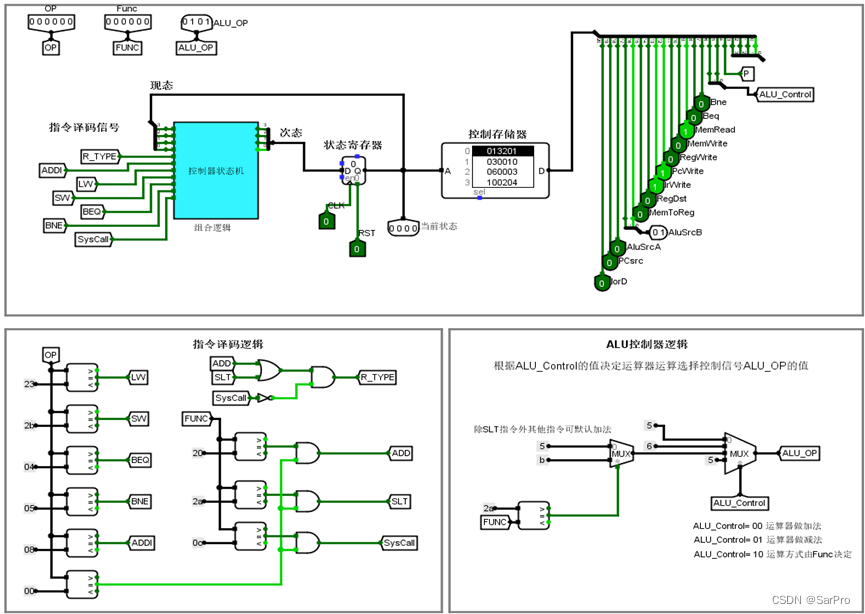

🌼Уровень 4: Проектирование конечного автомата аппаратного контроллера

Откройте файл data.circ в экспериментальном пакете в logisim и завершите схему обнаружения ошибок четности в соответствующей схеме. Вход: 17-битный контрольный код, контрольная цифра хранится в старшем бите. Выход: 16-битные исходные данные, 1 бит обнаружения ошибок. Определение входа и выхода экспериментальной схемы. Обратите внимание, что каждый бит 17-битного контрольного кода; проходит через отвод. Устройство вводится с помощью туннельных меток, что удобно для использования при проведении экспериментов.

🌼Уровень 5: Проектирование ЦП многотактного аппаратного контроллера MIPS (программа секвенирования)

(1) Создайте основные функциональные компоненты и пути к данным.

Основные функциональные компоненты, необходимые для разработки многотактного процессора MIPS, разработаны на платформе Logisim. Файл регистров использует стандартную библиотеку cs3410. Арифметический оператор может использовать либо собственный арифметический оператор в арифметическом эксперименте, либо стандартную библиотеку. Модуль ALU создает многоцикловый путь данных процессора MIPS и в конечном итоге соединяет различные функциональные компоненты для формирования пути данных.

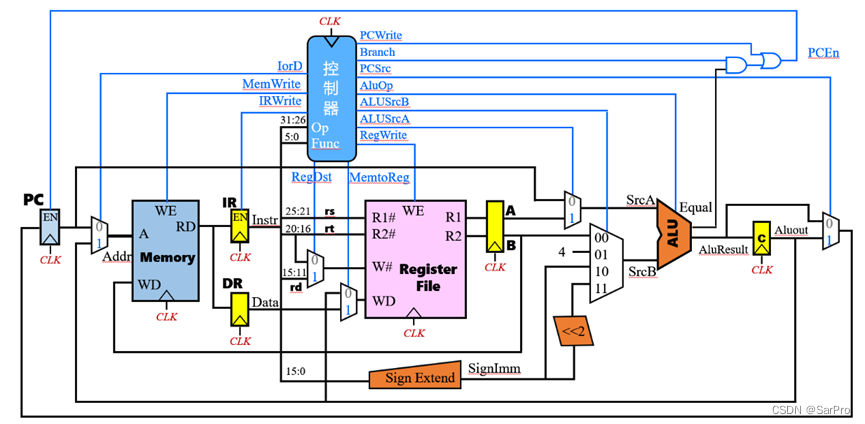

Рисунок 4.1-2

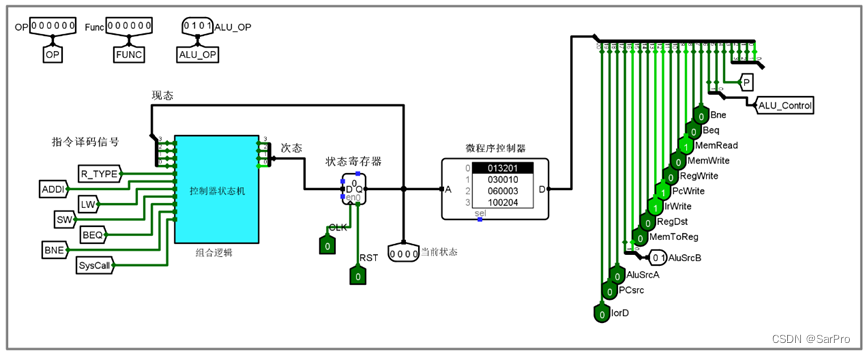

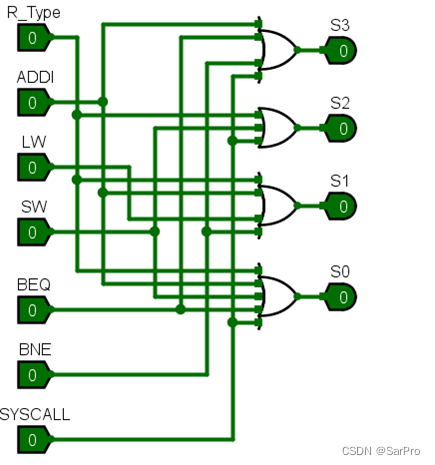

(2) Создайте проводной контроллер.

Создайте аппаратный контроллер на основе заданного конечного автомата.

Рисунок 4.1-3

Требуется поддержка 8 основных инструкций.

Рисунок 4.1-4

Рисунок 4.1-5

🌷3. Шаги для прохождения уровня.

🌼Уровень 1: Проектирование однотактного процессора MIPS

Рисунок 4.1-6

🌼Уровень 2: Разработка логики передачи адреса микропрограммы.

Рисунок 4.1-7

🌼Уровень 3: Проектирование процессора микропрограммы MIPS

Рисунок 4.1-8

🌼Уровень 4: Проектирование конечного автомата аппаратного контроллера

Рисунок 4.1-9

🌼Уровень 5: Проектирование ЦП многотактного аппаратного контроллера MIPS (программа секвенирования)

Рисунок 4.1-10

🌷4. Краткое описание прорыва уровня.

🌼Уровень 1: Проектирование однотактного процессора MIPS

1. Поймите, что однотактный процессор MIPS означает, что выполнение одной инструкции завершается за один такт, а затем начинается выполнение следующей инструкции, то есть одна инструкция завершается за один такт.

2. Появляется сообщение «невозможно найти библиотеку jar cs3410.jar». Поскольку пути к cs3410.jar и cs3410.jar на тестовой платформе различаются, вы можете сначала переместить локальный файл cs3410.jar в тот же каталог, что и cpu.circ, и затем откройте cpu. circ, logisim сообщит, что cs3410.jar не найден, перенаправьте в тот же каталог. cs3410.jar, сохраните и выйдите, а затем повторно загрузите текстовое содержимое схемы, чтобы решить проблему.

🌼Уровень 2: Разработка логики передачи адреса микропрограммы.

1. Логическая схема передачи адреса используется для генерации адреса следующей микрокоманды и в основном состоит из двухуровневых вентилей И и вентилей ИЛИ. Сигналы данных, необходимые для логики передачи адреса, включают в себя: последующие микроадреса μA3-μA0, бит дискриминации P1 и коды операций команд IR7-IR5.

2. Регистр микроадреса 74LS175 содержит адрес микрокоманды для управляющей памяти. Когда CLR = 0, регистр микроадреса очищается и микропрограмма выполняется с адреса управляющей памяти 00H. Логика передачи адреса генерирует адрес следующей микрокоманды. Если сигналы синхронизации поступают непрерывно, микро- инструкции также будут выводиться в определенном порядке.

🌼Уровень 3: Проектирование процессора микропрограммы MIPS

1. Идея проекта: в подсхеме многоциклового ЦП (микропрограммы) MIPS постройте путь данных ЦП ПК, MEM, IR, DR, RegFile, ALU и контроллер.

2. Реализация логики передачи адреса микропрограммы может быть известна из диаграммы перехода состояний команды.

🌼Уровень 4: Проектирование конечного автомата аппаратного контроллера

Идея дизайна: во-первых, проанализировать последовательность микроопераций цикла выполнения, цикла косвенного адреса, цикла выполнения и цикла прерывания всех инструкций. Последовательность микроопераций цикла выполнения, цикла косвенного адреса и цикла прерывания является общей для всех команд. все инструкции и выполнение различных инструкций. Циклы различаются, затем выбирают режим управления ЦП. Каждая инструкция состоит из соответствующей последовательности микроопераций. Затем первый шаг последовательности микроопераций делится на такты каждой. Нарисованы машинный цикл и все диаграммы микроопераций машинного цикла, тактов и инструкций, используйте это для записи комбинационного логического выражения каждой микрооперации и используйте это для проектирования схемы.

🌼Уровень 5: Проектирование ЦП многотактного аппаратного контроллера MIPS (программа секвенирования)

По сравнению с однотактным ЦП конструкция проводного контроллера многотактного ЦП MIPS только заменяет контроллер микроинструкций на проводной контроллер, но другие части не изменились, поэтому часть пути данных такая же, как и у Многотактный процессор MIPS контроллера микроинструкций.

Учебное пособие по Jetpack Compose для начинающих, базовые элементы управления и макет

Код js веб-страницы, фон частицы, код спецэффектов

【новый! Суперподробное】Полное руководство по свойствам компонентов Figma.

🎉Обязательно к прочтению новичкам: полное руководство по написанию мини-программ WeChat с использованием программного обеспечения Cursor.

[Забавный проект Docker] VoceChat — еще одно приложение для мгновенного чата (IM)! Может быть встроен в любую веб-страницу!

Как реализовать переход по странице в HTML (html переходит на указанную страницу)

Как решить проблему зависания и низкой скорости при установке зависимостей с помощью npm. Существуют ли доступные источники npm, которые могут решить эту проблему?

Серия From Zero to Fun: Uni-App WeChat Payment Practice WeChat авторизует вход в систему и украшает страницу заказа, создает интерфейс заказа и инициирует запрос заказа

Серия uni-app: uni.navigateЧтобы передать скачок значения

Апплет WeChat настраивает верхнюю панель навигации и адаптируется к различным моделям.

JS-время конвертации

Обеспечьте бесперебойную работу ChromeDriver 125: советы по решению проблемы chromedriver.exe не найдены

Поле комментария, щелчок мышью, специальные эффекты, js-код

Объект массива перемещения объекта JS

Как открыть разрешение на позиционирование апплета WeChat_Как использовать WeChat для определения местонахождения друзей

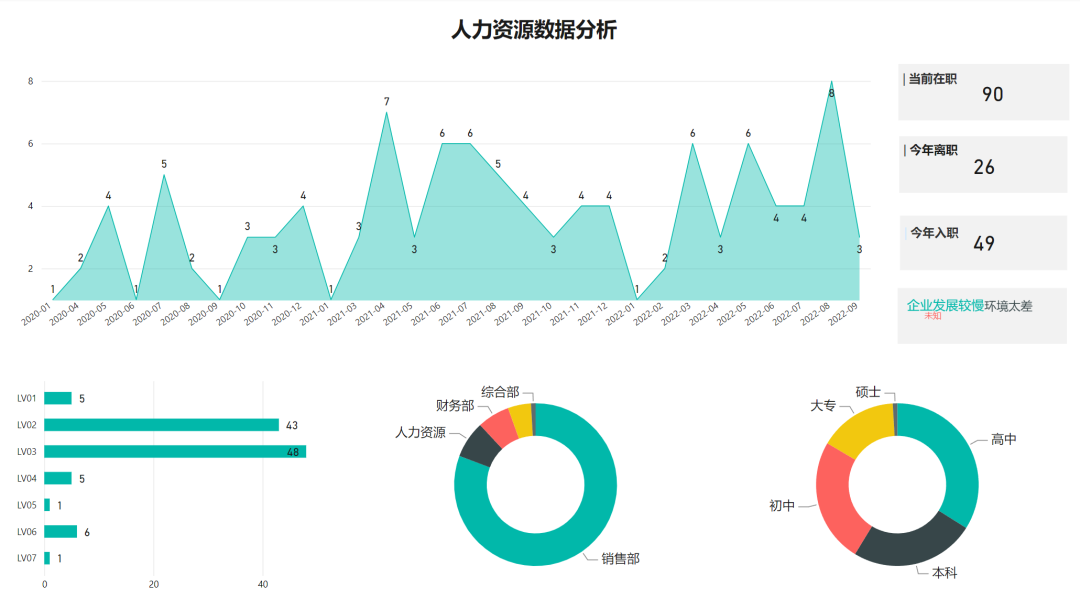

Я даю вам два набора из 18 простых в использовании фонов холста Power BI, так что вам больше не придется возиться с цветами!

Получить текущее время в js_Как динамически отображать дату и время в js

Вам необходимо изучить сочетания клавиш vsCode для форматирования и организации кода, чтобы вам больше не приходилось настраивать формат вручную.

У ChatGPT большое обновление. Всего за 45 минут пресс-конференция показывает, что OpenAI сделал еще один шаг вперед.

Copilot облачной разработки — упрощение разработки

Микросборка xChatGPT с низким кодом, создание апплета чат-бота с искусственным интеллектом за пять шагов

CUDA Out of Memory: идеальное решение проблемы нехватки памяти CUDA

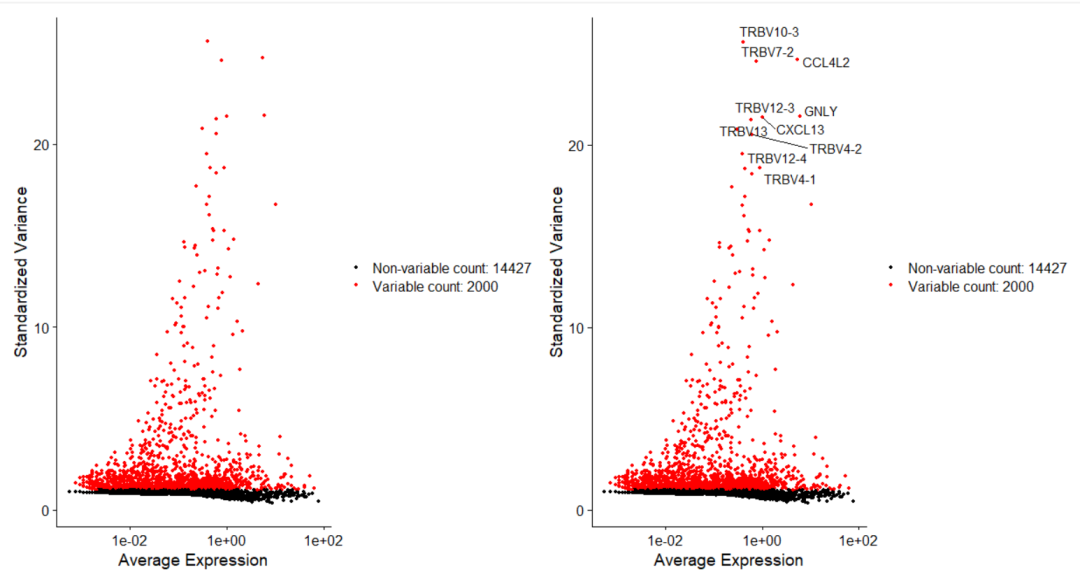

Анализ кластеризации отдельных ячеек, который должен освоить каждый&MarkerгенетическийВизуализация

vLLM: мощный инструмент для ускорения вывода ИИ

CodeGeeX: мощный инструмент генерации кода искусственного интеллекта, который можно использовать бесплатно в дополнение к второму пилоту.

Машинное обучение Реальный бой LightGBM + настройка параметров случайного поиска: точность 96,67%

Бесшовная интеграция, мгновенный интеллект [1]: платформа больших моделей Dify-LLM, интеграция без кодирования и встраивание в сторонние системы, более 42 тысяч звезд, чтобы стать свидетелями эксклюзивных интеллектуальных решений.

LM Studio для создания локальных больших моделей

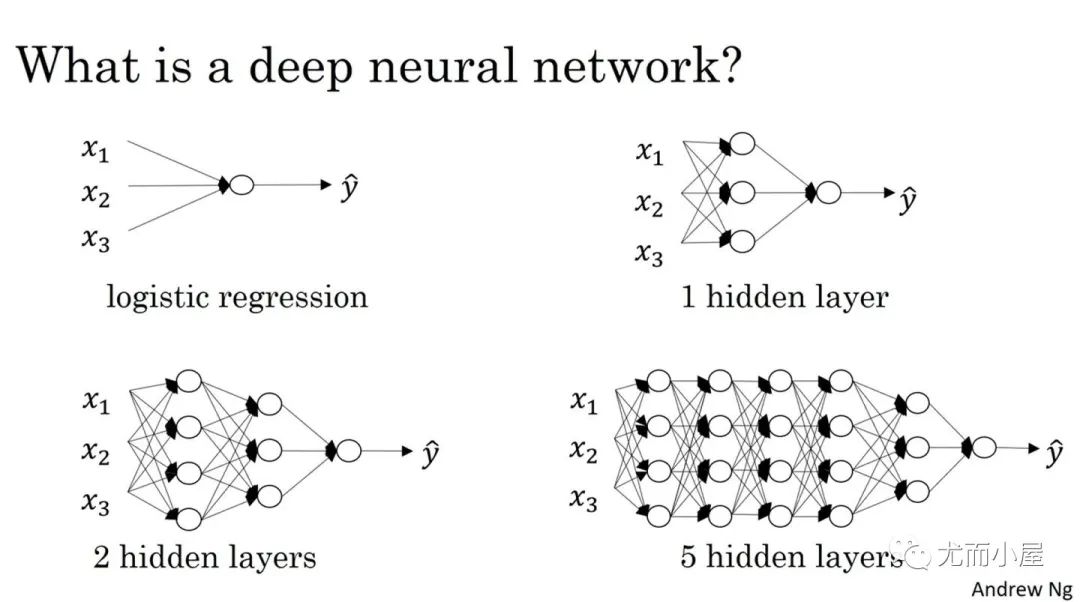

Как определить количество слоев и нейронов скрытых слоев нейронной сети?