[Нарисуйте свой собственный процессор] Дизайн калькулятора

🌷1. Цель

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

(1) освоить логику реализации однобитного полного сумматора и логику реализации многобитной управляемой схемы сложения и вычитания;

(2) Быть знакомым с основными функциями платформы Logisim и уметь реализовывать в Logisim многоразрядные управляемые схемы сложения и вычитания.

🌼Уровень 2: проектирование схемы с четырехбитным переносом CLA182.

(1) Овладеть принципом переноса вперед в быстрых сумматорах и уметь использовать соответствующие знания для проектирования 4-битной схемы переноса вперед;

(2) Используйте разработанную 4-битную схему переноса, чтобы построить 4-битный быстрый сумматор и проанализировать временную задержку соответствующей схемы.

🌼Уровень 3: проектирование 4-битного быстрого сумматора

(1) Овладеть принципом переноса вперед в быстрых сумматорах и уметь использовать соответствующие знания для проектирования 4-битной схемы переноса вперед;

(2) Используйте разработанную 4-битную схему переноса, чтобы построить 4-битный быстрый сумматор и проанализировать временную задержку соответствующей схемы.

🌼Уровень 4: проектирование 16-битного быстрого сумматора

(1) Понимать концепции функции генерации группового переноса и функции передачи группового переноса, а также быть знакомым с концепцией подсхемы платформы Logisim;

(2) Используйте 4-битную подсхему переноса вперед и 4-битную подсхему быстрого сумматора, включенные в вышеупомянутые эксперименты, для построения 16-битных, 32-битных и 64-битных быстрых сумматоров и используйте соответствующие знания для анализа времени. задержка соответствующей схемы и понимание схемы. Понятие параллелизма.

🌼Уровень 5: проектирование 32-битного быстрого сумматора

(1) Понимать концепции функции генерации группового переноса и функции передачи группового переноса, а также быть знакомым с концепцией подсхемы платформы Logisim;

(2) Используйте 4-битную подсхему переноса вперед и 4-битную подсхему быстрого сумматора, включенные в вышеупомянутые эксперименты, для построения 16-битных, 32-битных и 64-битных быстрых сумматоров и используйте соответствующие знания для анализа времени. задержка соответствующей схемы и понимание схемы. Понятие параллелизма.

🌼Уровень 6: проектирование 5-битного беззнакового множителя массива

(1) Освоить принципы реализации массивных умножителей;

(2) Проанализируйте производительность 5-битного умножителя массива и нарисуйте схему умножителя массива в Logisim.

🌼Уровень 7: 6-битный множитель дополняющего массива со знаком

(1) Освоить принцип реализации множителя дополнительного массива;

(2) Проанализируйте производительность 6-битного умножителя массива и нарисуйте схему умножителя массива в Logisim.

🌼Уровень 8: Проектирование конвейера умножения

(1) освоить основные концепции вычислительного конвейера и понять идею разделения сложных вычислительных этапов на подпроцессы;

(2) Реализуйте простой конвейер умножения.

🌼Уровень 9: Оригинальный код однобитного множителя.

(1) Овладеть основными принципами операции однобитового умножения исходного кода;

(2) Быть опытным в использовании регистровых схем Logisim и уметь спроектировать и реализовать 8*8-битный беззнаковый умножитель на платформе Logisim.

🌼Уровень 10: конструкция с однодополнительным однобитным множителем

(1) Освоить основные принципы умножения с однобитным дополнением;

(2) Быть опытным в использовании регистровых схем Logisim и быть в состоянии спроектировать и реализовать 8*8-битный однобитный умножитель Booth на платформе Logisim.

🌼Уровень 11: Проектирование оператора MIPS

(1) Понять базовую структуру блока арифметико-логических операций (АЛУ) и освоить использование различных вычислительных компонентов в Logisim;

(2) Быть знакомым с использованием мультиплексоров и уметь использовать 32-битный сумматор, выполненный в вышеупомянутом эксперименте, и арифметические компоненты в Logisim для построения блока ALU с заданными характеристиками.

🌷2. Прорывной контент

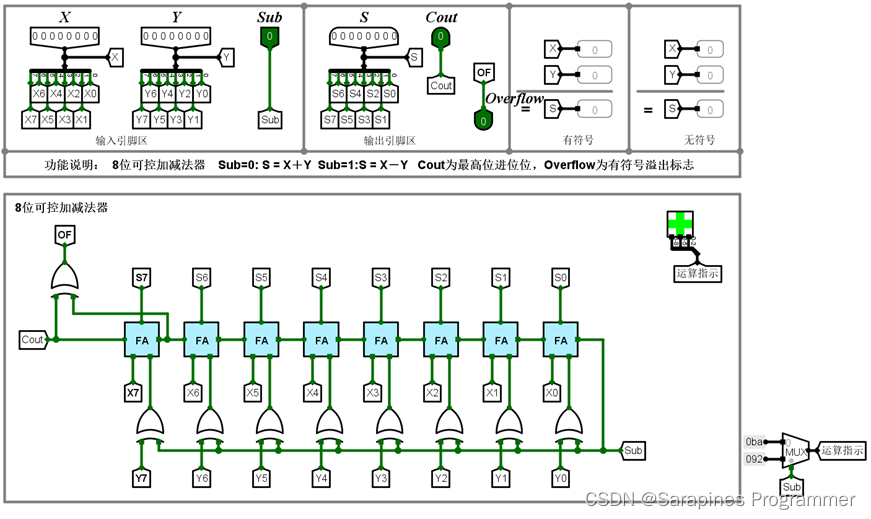

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

Откройте файл alu.circ в симуляторе Logisim и используйте упакованный полный сумматор в соответствующей подсхеме для разработки 8-битной последовательной управляемой схемы сложения и вычитания. Пользователь может напрямую использовать соответствующую метку туннеля в схеме, где X и. Y — два входных числа, Sub — сигнал управления сложением и вычитанием, S — выход результата операции, Cout — выход переноса, а OF — бит переполнения операции со знаком.

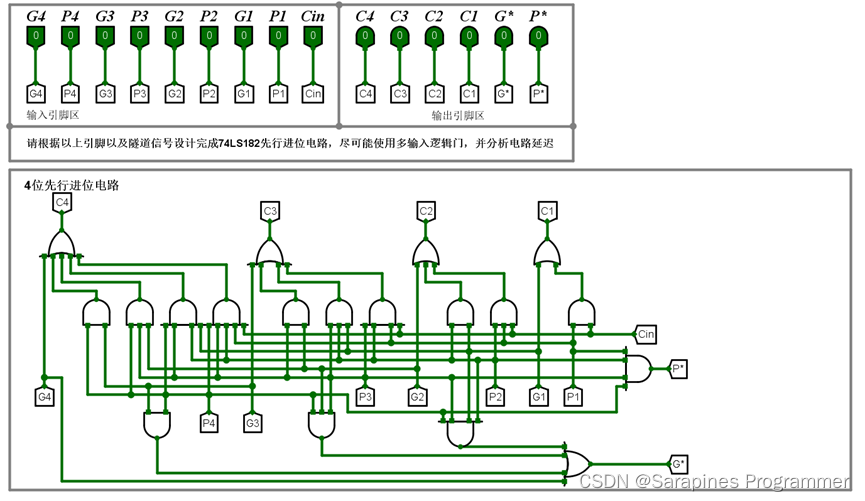

🌼Уровень 2: проектирование схемы с четырехбитным переносом CLA182.

Откройте файл alu.circ в Logisim и реализуйте каскадную 4-битную схему опережающего переноса в соответствующей подсхеме. Среди них Gi и Pi — функция генерации переноса и передаточная функция, Cin — вход переноса, C1 ~ C4 — выход переноса, G и P — функция генерации группового переноса и передаточная функция группового переноса.

🌼Уровень 3: проектирование 4-битного быстрого сумматора

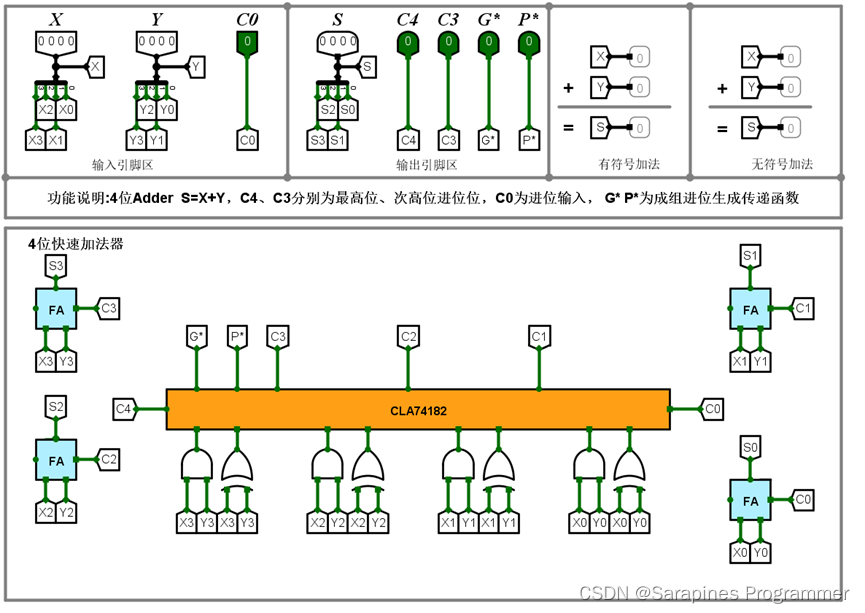

Используйте четырехбитную схему упреждающего переноса, разработанную на предыдущем шаге, для построения четырехбитного быстрого сумматора, где X и Y — четырехбитные слагаемые, Cin — вход переноса, S — выход суммы, Cout — выход переноса. , G и P — 4-битная функция генерации упакованного переноса и функция передачи упакованного переноса.

🌼Уровень 4: проектирование 16-битного быстрого сумматора

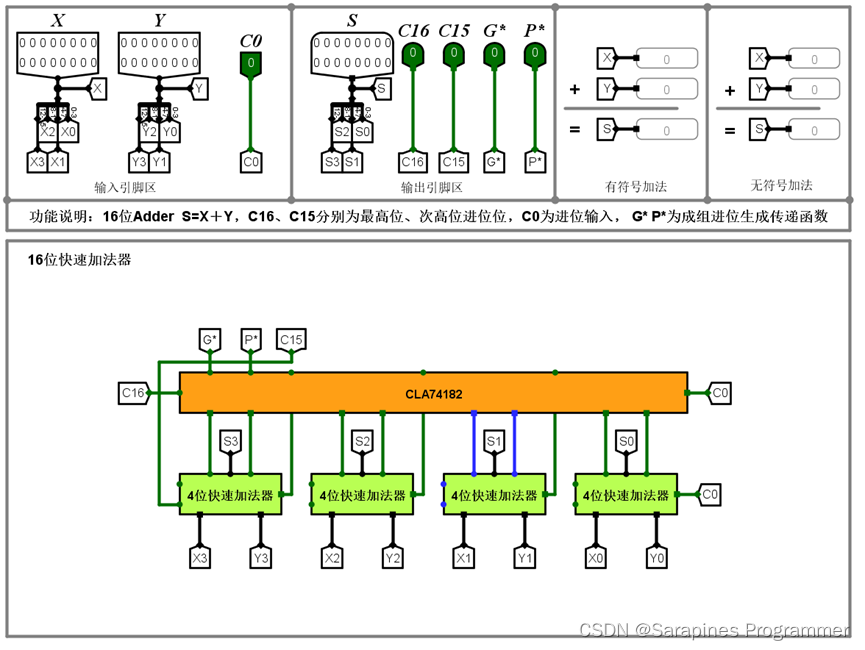

Откройте файл alu.circ в Logisim, используйте четырехбитную схему переноса вперед и четырехбитный быстрый сумматор в соответствующей подсхеме, чтобы построить шестнадцатибитный быстрый сумматор с межгрупповым переносом, и проверьте, совпадают ли их функции. нормальный. . Среди них,

🌼Уровень 5: проектирование 32-битного быстрого сумматора

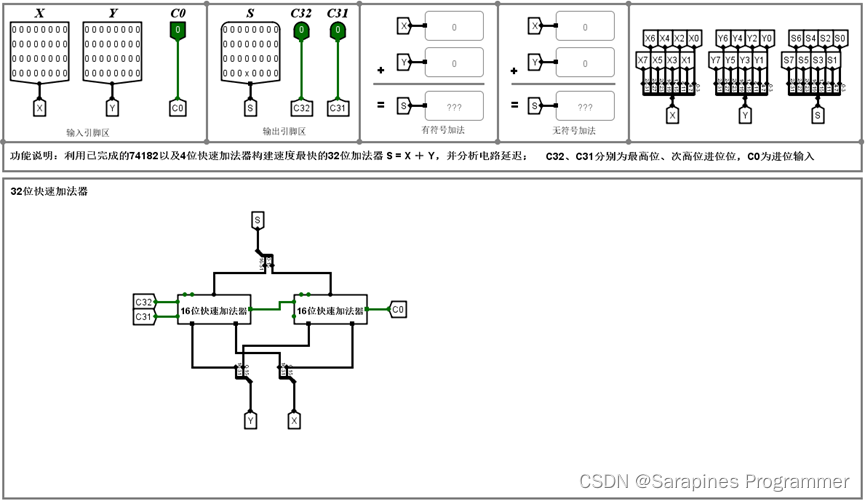

32-битный быстрый сумматор построен с использованием 16-битного быстрого сумматора и схемы переноса, и обсуждается его временная задержка. Возможные решения:

(1) Два 16-битных сумматора соединены напрямую последовательно, и сигнал C16 использует выход переноса нижнего уровня;

(2) Два 16-битных сумматора соединены напрямую последовательно, а вход переноса C16 использует верхний выход переноса;

(3) На основе 16-битного быстрого сумматора добавьте схему межгруппового опережающего переноса первого уровня, аналогичную методу 64-битного быстрого сумматора, и проанализируйте возможные общие задержки трех различных решений; выберите самое быстрое решение для достижения быстрого 32-битного сумматора и проанализируйте его временную задержку. Среди них X и Y — 32-битные слагаемые, Cin — вход переноса, S — выход суммы, Cout — выход переноса, а Overflow — сигнал переполнения операции сложения со знаком.

🌼Уровень 6: проектирование 5-битного беззнакового множителя массива

Откройте файл alu.circ в Logisim и реализуйте множитель массива косого переноса в 5-битном множителе массива, где X и Y — 5-битное множимое и множитель, P — выходное произведение, а для умножения массива требуется 25. Произведение члены поразрядного И генерируются через вспомогательную схему, а все термины продукта передаются через метки туннеля. Пользователю нужно только выполнить простые соединения в данной структуре схемы, чтобы завершить 5-битный умножитель массива.

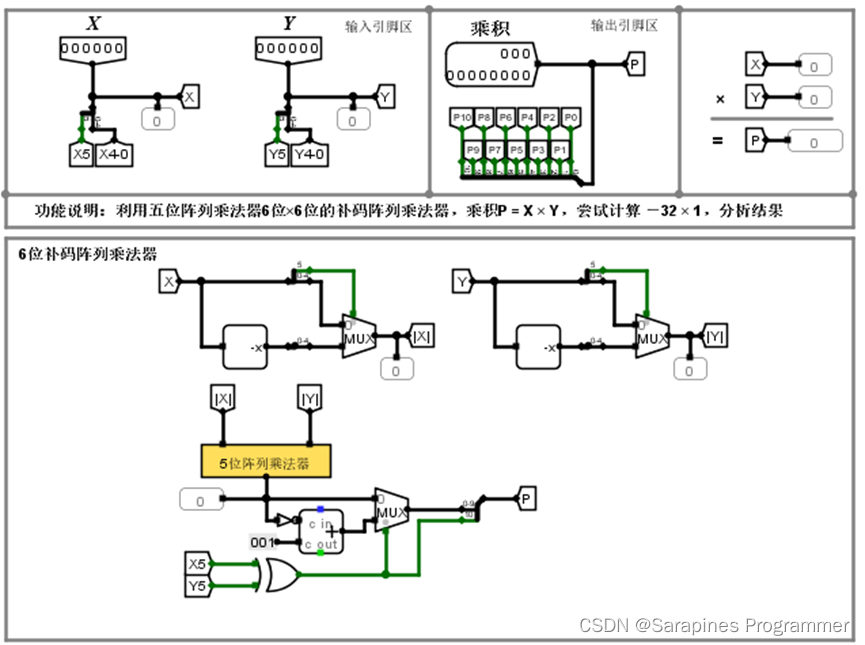

🌼Уровень 7: 6-битный множитель дополняющего массива со знаком

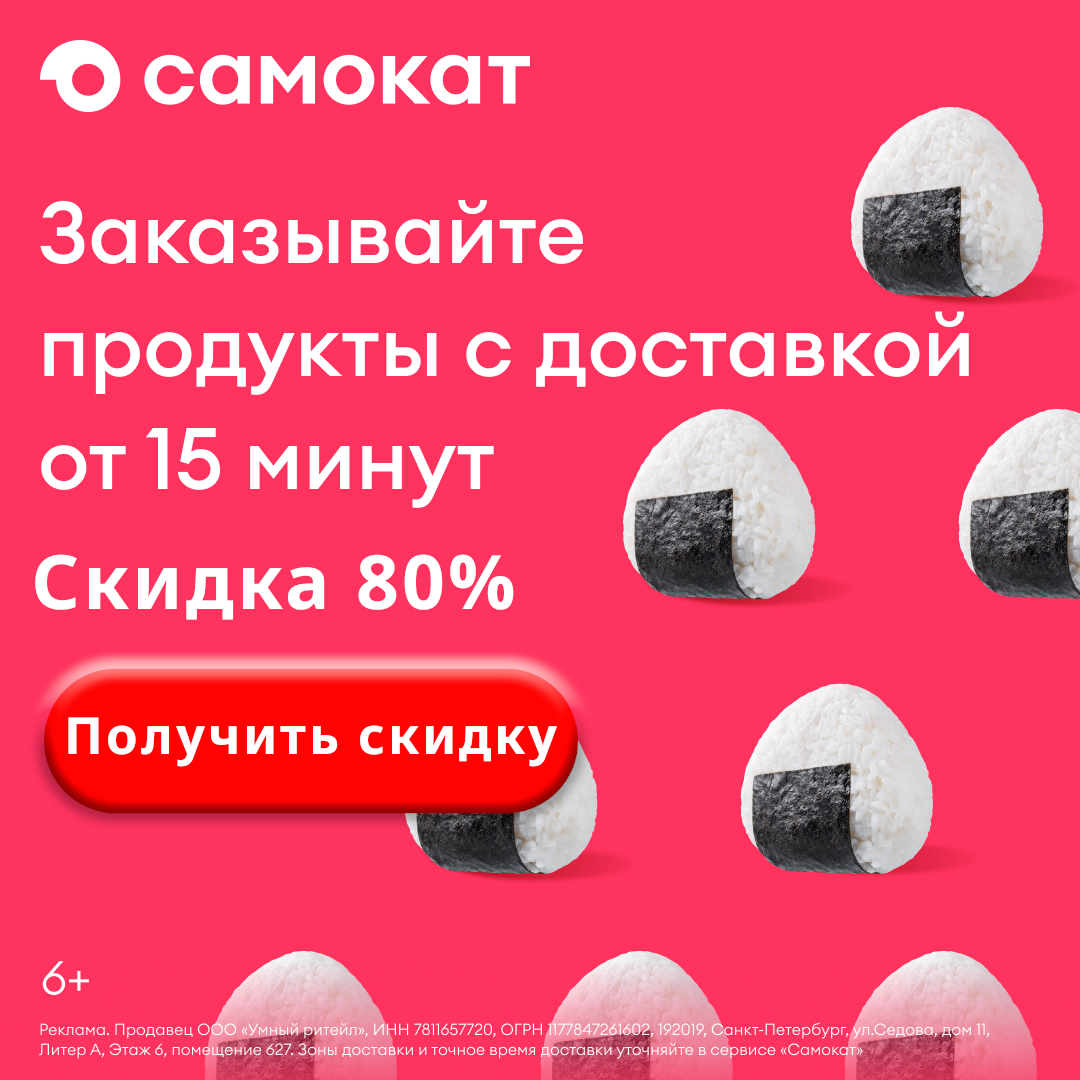

Откройте файл alu.circ в Logisim и используйте 5-битный множитель и дополнитель массива, чтобы реализовать множитель дополнительного массива в 6-битном множителе дополнительного массива. Схема эксперимента показана на рисунке 2-1:

Рисунок 2-1

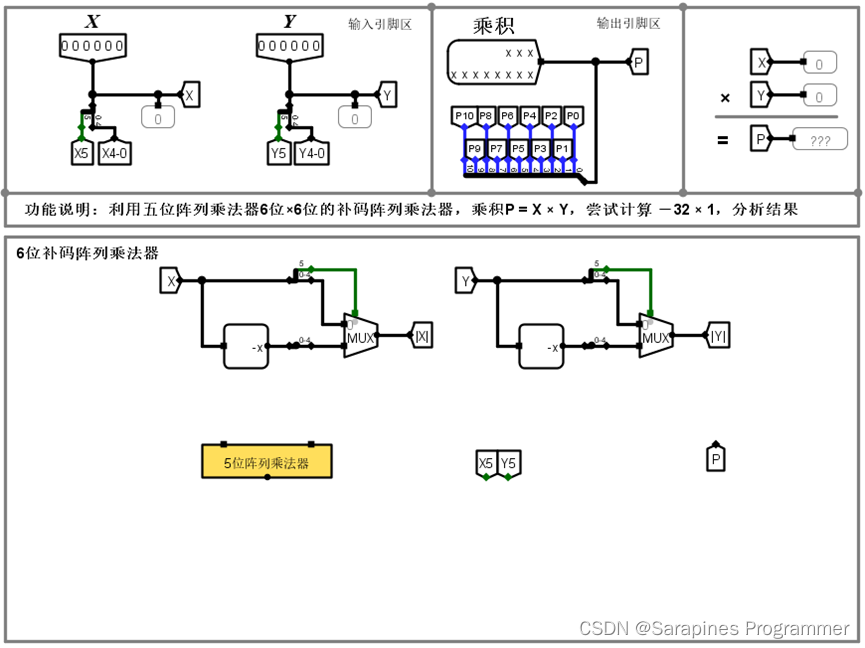

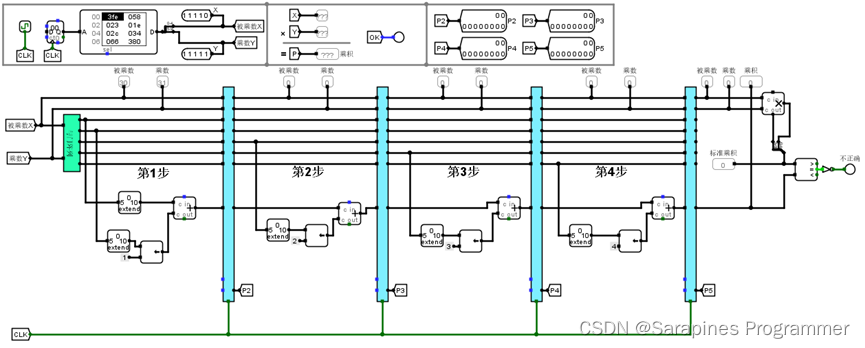

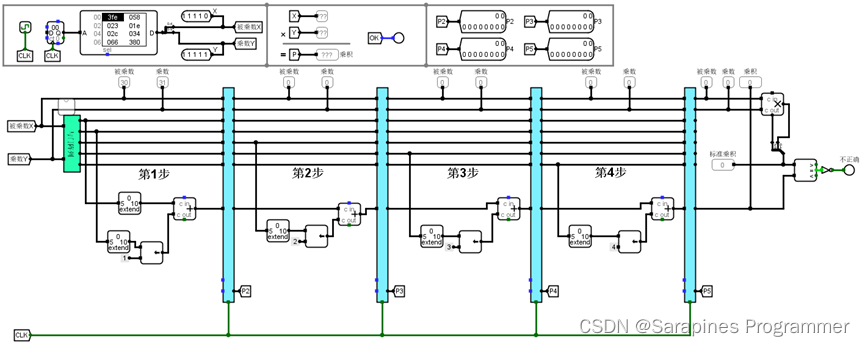

🌼Уровень 8: Проектирование конвейера умножения

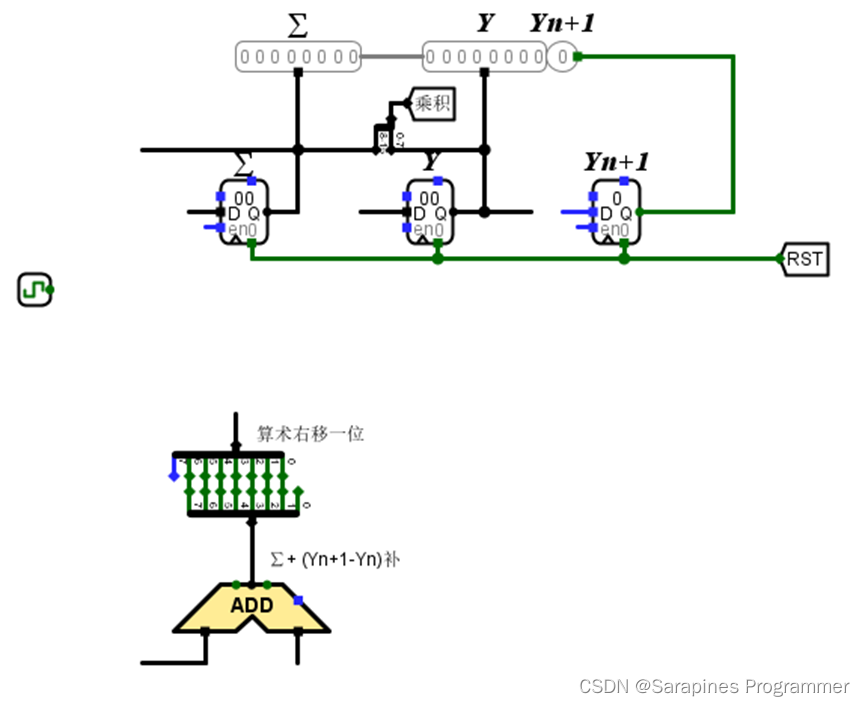

Откройте файл alu.circ в Logisim и используйте 5-битный множитель и дополнитель массива, чтобы реализовать множитель дополнительного массива в 6-битном множителе дополнительного массива. Схема эксперимента показана на рисунке 2-2:

Рисунок 2-2

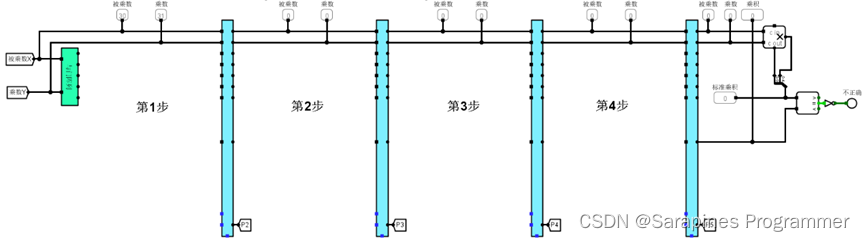

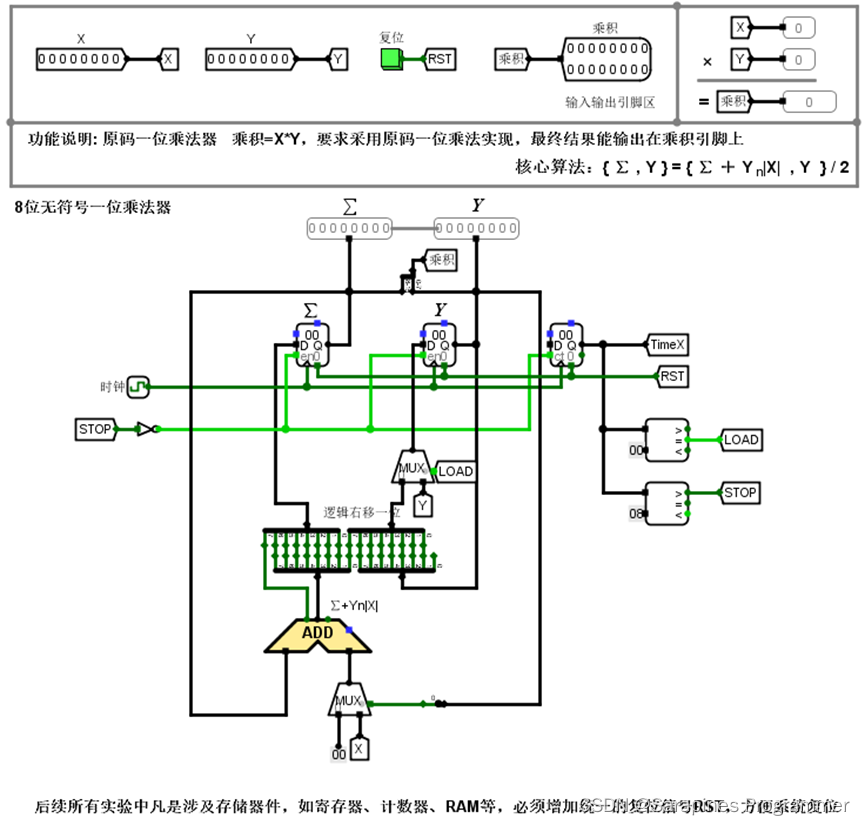

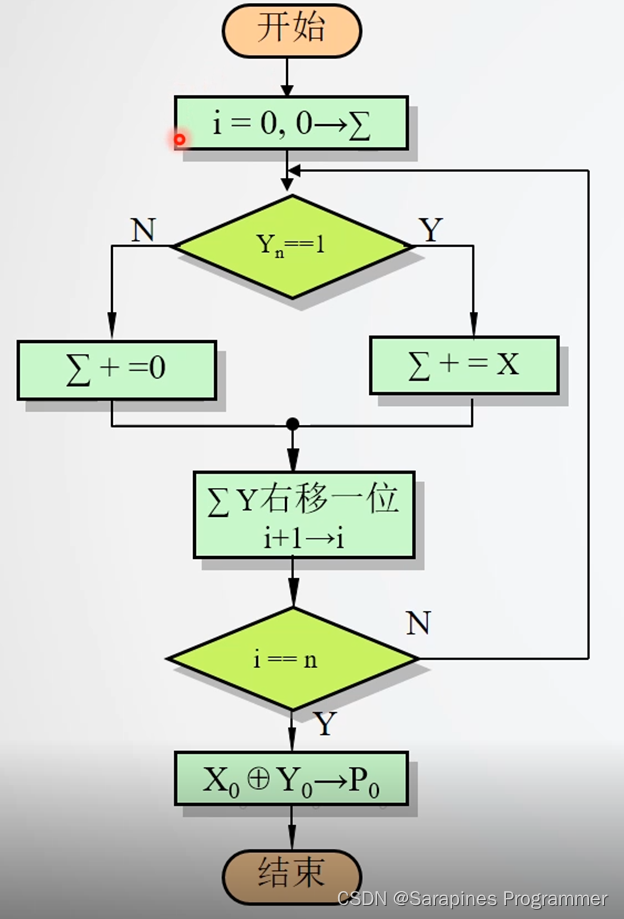

🌼Уровень 9: Оригинальный код однобитного множителя.

В исходную подсхему однобитового умножителя в файле alu.circ добавляются схема управления и путь данных, чтобы схема могла автоматически выполнять однобитовую операцию умножения 8-битных беззнаковых чисел. Затем установите начальное значение вывода, а затем запустите часы для автоматической имитации, и схема сможет автоматически завершить операцию. Операция завершена, и результат передается на выходной вывод. В конце операции экспериментальная структура показана на рисунке 2-3:

Рисунок 2-3

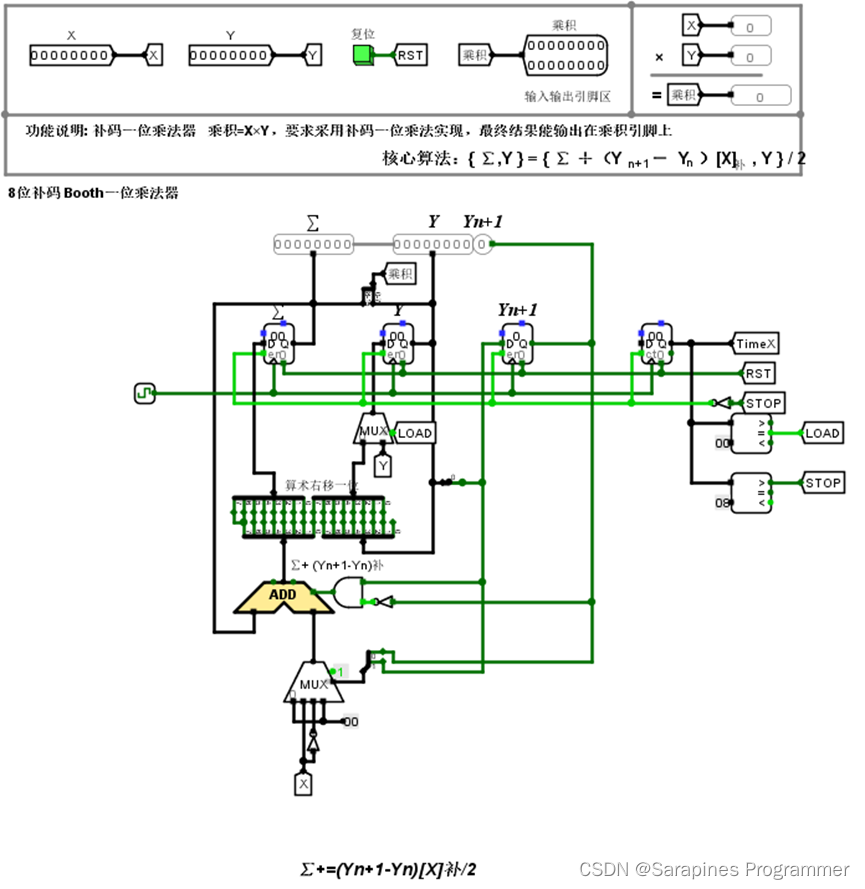

🌼Уровень 10: конструкция с однодополнительным однобитным множителем

В подсхему однодополнительного однобитового умножителя в файле alu.circ добавляются схема управления и путь данных, чтобы схема могла автоматически выполнять 8-битную операцию умножения с одним дополнением. Затем установите начальное значение вывода, а затем запустите часы для автоматической имитации, и схема сможет автоматически завершить операцию. Операция завершена, и результат передается на выходной вывод. В конце операции схема должна автоматически остановиться. Схема эксперимента показана на рисунке 2-4:

Рисунок 2-4

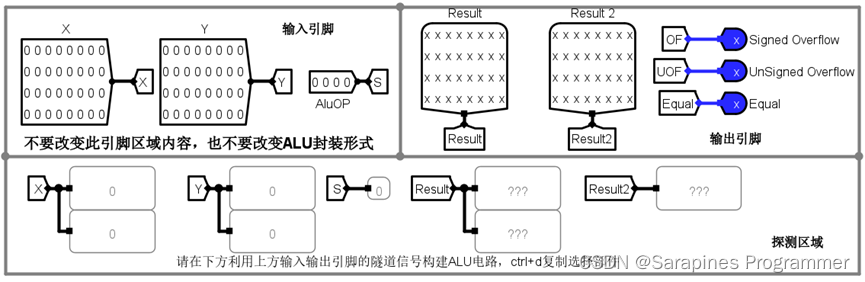

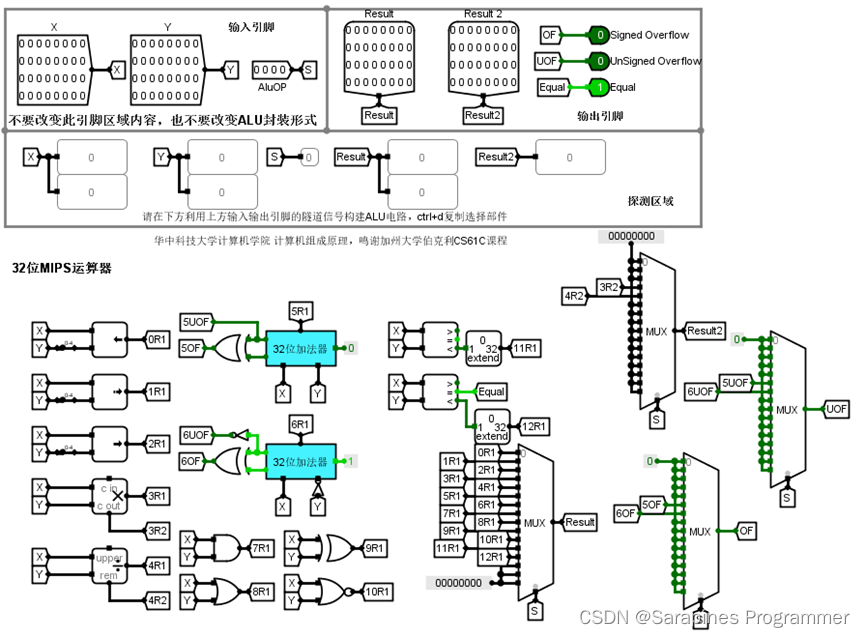

🌼Уровень 11: Проектирование оператора MIPS

Используйте 32-битный сумматор, инкапсулированный в предыдущем эксперименте, и существующие вычислительные компоненты платформы Logisim, чтобы создать 32-битный блок арифметических логических операций (отключите сумматор и вычитатель, поставляемые с системой Logisim), который может поддерживать арифметическое сложение. вычитание, умножение, деление, логическое И, ИЛИ, НЕ, операция исключающее ИЛИ, логический сдвиг влево, логический сдвиг вправо, арифметическая операция сдвига вправо, поддерживает общие флаги состояния программы (переполнение со знаком OF, переполнение без знака UOF, результат равен), ALU Функции, а также входные и выходные контакты показаны в таблице ниже. Подробно протестируйте самокомплектный АЛУ в основной схеме и проанализируйте преимущества и недостатки оператора. Схема эксперимента показана на рисунке 2-:

Рисунок 2-5

🌷3. Шаги для прохождения

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

Рисунок 2-6

🌼Уровень 2: проектирование схемы с четырехбитным переносом CLA182.

Рисунок 2-7

🌼Уровень 3: проектирование 4-битного быстрого сумматора

Рисунок 2-8

🌼Уровень 4: проектирование 16-битного быстрого сумматора

Рисунок 2-9

🌼Уровень 5: проектирование 32-битного быстрого сумматора

Рисунок 2-10

🌼Уровень 6: проектирование 5-битного беззнакового множителя массива

Рисунок 2-11

🌼Уровень 7: 6-битный множитель дополняющего массива со знаком

Рисунок 2-12

🌼Уровень 8: Проектирование конвейера умножения

Рисунок 2-13

🌼Уровень 9: Оригинальный код однобитного множителя.

Рисунок 2-14

🌼Уровень 10: конструкция с однодополнительным однобитным множителем

Рисунок 2-15

🌼Уровень 11: Проектирование оператора MIPS

Рисунок 2-16

🌷4. Краткое описание прохождения уровней

🌼Уровень 1: 8-битная схема управляемого сложения и вычитания.

1. Параллельный сумматор: Выход переноса связан только с наименьшим входом переноса C0 (Cn=Gn+PnGn-1+PnPn-1Gn-2+PnPn-1Pn-2Gn-3…+PnPn-1…P1C0), а не опираясь на перенос младшего порядка (Cn= Gn + Pn Cn-1).

2. Аппаратная реализация: управляемый противофазный вентиль XOR. С помощью вентиля XOR Sub может реализовать Y и не-Y, установив значение от 0 до 1, а также может использоваться в качестве входного сигнала 0 и 1 для Cin. OF — это флаг переполнения, а выход переполнения равен 1 (здесь 1 — это). высокий уровень). Аппаратная реализация для определения переполнения операций сложения и вычитания знаковых чисел: перенос старшего бита ⊕ перенос знакового бита, 1 указывает на переполнение.

🌼Уровень 2: проектирование схемы с четырехбитным переносом CLA182.

Принцип эксперимента: откройте файл alu.circ в симуляторе Logisim и используйте упакованный полный сумматор в соответствующей подсхеме для разработки 8-битной последовательной управляемой схемы сложения и вычитания. Вы можете напрямую использовать соответствующую метку туннеля в схеме. где X и Y — два входных числа, Sub — сигнал управления сложением и вычитанием, S — выход результата операции, Cout — выход переноса, а OF — переполнение операции со знаком.

🌼Уровень 3: проектирование 4-битного быстрого сумматора

Идеи для решения проблемы: используйте четырехбитную схему опережающего переноса, разработанную на уровне 2, для построения четырехбитного быстрого сумматора. X и Y — четырехбитные слагаемые, Cin — вход переноса, S — выходная сумма, Cout — это. выход переноса, а G, P — 4-битная функция генерации упакованного переноса и передаточная функция упакованного переноса.

🌼Уровень 4: проектирование 16-битного быстрого сумматора

1. Принцип полного сумматора. Полный сумматор представляет собой схему двоичного сложения, способную вычислять перенос младшего порядка. По сравнению с полусумматором, полный сумматор не только учитывает наличие переноса в результате вычисления локального бита, но также учитывает перенос предыдущего бита в локальный бит, к которому можно каскадно подключить несколько однобитовых полных сумматоров. сделать многобитный полный сумматор.

2. Принцип эксперимента: четыре четырехбитных полных сумматора используются для сложения двух многозначных двоичных чисел и одновременной генерации переноса. При добавлении двух двоичных чисел термин переноса из младшего бита должен быть добавлен при добавлении старших битов.

🌼Уровень 5: проектирование 32-битного быстрого сумматора

Принцип эксперимента: два 16-битных полных сумматора используются для сложения двух многозначных двоичных чисел и одновременной генерации переноса. При добавлении двух двоичных чисел термин переноса из младшего бита должен быть добавлен при добавлении старших битов.

🌼Уровень 6: проектирование 5-битного беззнакового множителя массива

Принцип эксперимента: цифровая логика представляет собой программируемую вентильную матрицу, которая является продуктом дальнейшей разработки на основе программируемых устройств, таких как PAL, GAL и CPLD. Он выглядит как полузаказная схема в области интегральных схем специального назначения (ASIC). Он не только устраняет недостатки нестандартных схем, но также устраняет недостатки ограниченного числа исходных схем программируемых устройств. Каждый бит. множитель используется для умножения множимого, а затем непосредственно умножает каждый бит веса на множимое, чтобы получить частичный продукт, и выравнивает последнюю цифру частичного продукта в каждой строке подряд с соответствующей цифрой множителя, чтобы отразить вес соответствующей цифры. Окончательный вес соответствующей цифры получается путем суммирования частичных произведений каждого времени.

🌼Уровень 7: 6-битный множитель дополняющего массива со знаком

Принцип эксперимента: для входных данных X и Y, если они оба положительные числа, бит знака удаляется, и абсолютное значение вводится в 5-битный множитель массива. Если все они отрицательные числа, сначала отправьте XY в комплементар. Вы получите абсолютное значение X и Y, а затем введите его в 5-битный множитель массива.

🌼Уровень 8: Проектирование конвейера умножения

Этот тест проще, чем для, и его процесс показан на рисунке 2-17.

Рисунок 2-17

🌼Уровень 9: Оригинальный код однобитного множителя.

1. Контроль количества перемещений: Используйте аппаратную реализацию счетчика + компаратора Просто управляйте правым сдвигом 9 раз (в вопросе есть подсказка). При LOAD = 0 подается сигнал 1; правый регистр и другой. Когда =0, регистр справа обновляется в соответствии со смещением.

2. Реализация смещения: используются четыре группы верхних и нижних разделителей шириной 8 бит. Старший бит слева — младший бит справа. Произведение сдвигается вправо. Самый старший бит получается при переносе. вход восьмибитного сумматора. Всплывающие данные правого сдвига используются для развертывания селектора данных. Время равно +0 или +a.

🌼Уровень 10: конструкция с однодополнительным однобитным множителем

1. Селектор реализован для оценки данных Yn+1Yn, чтобы определить, следует ли добавлять 0, дополнение [x] или дополнение [-x] на основе суммы: входной конец выбора селектора - Yn+1Yn и селектор 0-й и 3-й Все биты подключены к 0, и первый вход соответствует дополнению [x]. В сумматоре ADD, когда Yn+1Yn=01, вход переноса равен 1. В это время добавляется дополнение [-x]. . В селекторе Второй входной бит — x.

2. Управление сдвигом: в этот момент выполняется арифметический сдвиг вправо, младший бит удаляется, а старший бит копируется исходный старший бит. Этого можно добиться с помощью разделителя. 16-битные данные после сдвига вправо, 8 бит слева — это частичные произведения, хранящиеся в регистре частичного произведения, восемь бит справа — это старшие битовые данные младшего произведения + y, сдвинутые вправо; (младшие битовые данные управляются часами каждый раз, когда вычисляются и удаляются) и сохраняются в регистре Y.

🌼Уровень 11: Проектирование оператора MIPS

1. Проект таможенного оформления: используйте 32-битный сумматор, включенный в предыдущий эксперимент, и существующие вычислительные компоненты платформы logisim, чтобы создать 32-битный сумматор. Блок битовых арифметических логических операций посредством мультиплексной обработки выполняет сложение, вычитание, умножение, деление, логические операции И, ИЛИ, НЕ, исключающее ИЛИ, логический сдвиг влево, логический сдвиг вправо и арифметический сдвиг вправо соответственно и получает результаты. результат, соответствующий выбранному методу операции, передается в Result через мультиплексор. Во время операций умножения и деления результат старшего порядка или остаток передается в Result2. В других случаях результат Result2 равен 0.

2. Используйте сдвигатели для реализации логических операций сдвига влево, сдвига вправо и арифметических операций сдвига вправо.

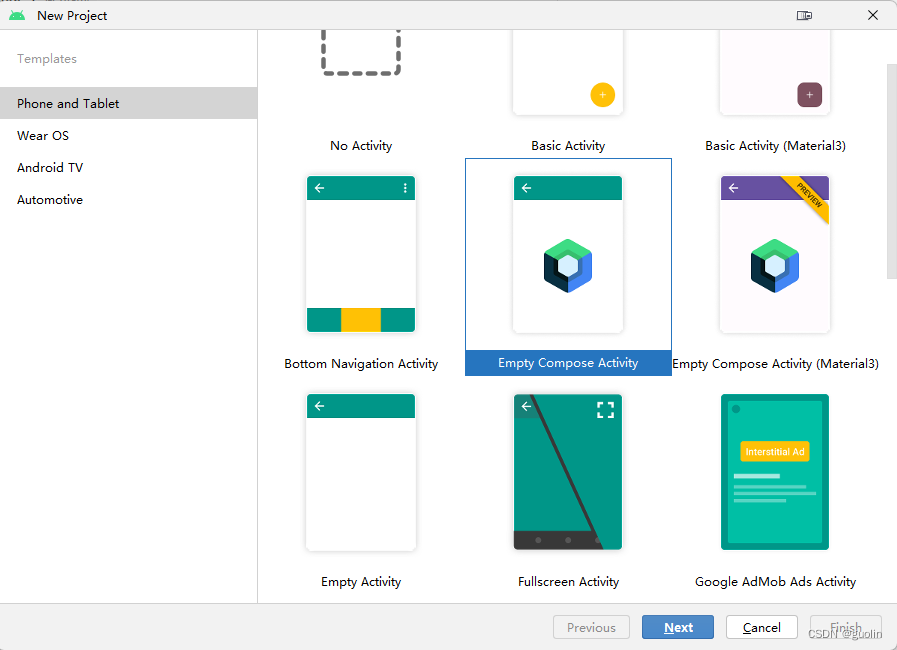

Учебное пособие по Jetpack Compose для начинающих, базовые элементы управления и макет

Код js веб-страницы, фон частицы, код спецэффектов

【новый! Суперподробное】Полное руководство по свойствам компонентов Figma.

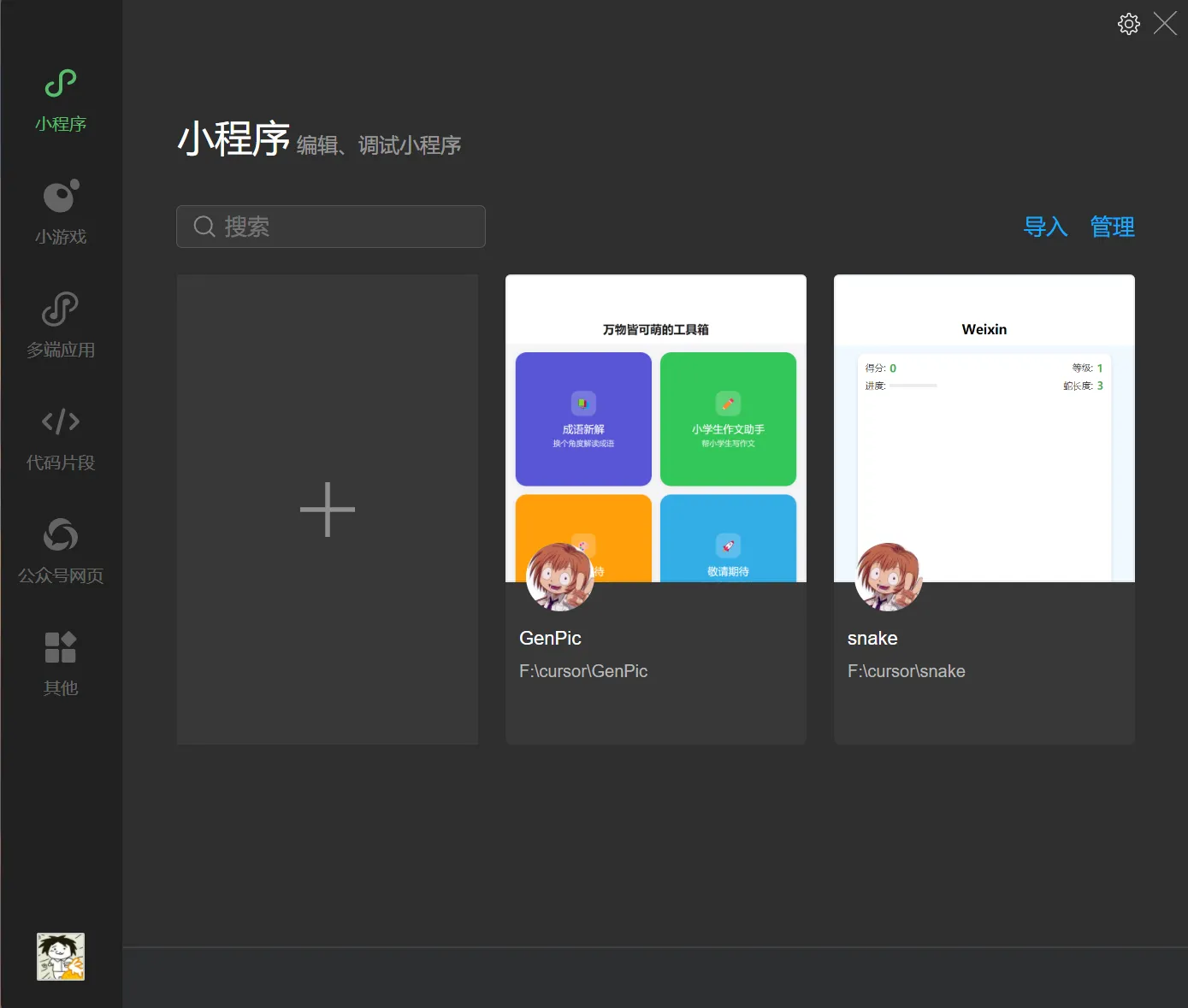

🎉Обязательно к прочтению новичкам: полное руководство по написанию мини-программ WeChat с использованием программного обеспечения Cursor.

[Забавный проект Docker] VoceChat — еще одно приложение для мгновенного чата (IM)! Может быть встроен в любую веб-страницу!

Как реализовать переход по странице в HTML (html переходит на указанную страницу)

Как решить проблему зависания и низкой скорости при установке зависимостей с помощью npm. Существуют ли доступные источники npm, которые могут решить эту проблему?

Серия From Zero to Fun: Uni-App WeChat Payment Practice WeChat авторизует вход в систему и украшает страницу заказа, создает интерфейс заказа и инициирует запрос заказа

Серия uni-app: uni.navigateЧтобы передать скачок значения

Апплет WeChat настраивает верхнюю панель навигации и адаптируется к различным моделям.

JS-время конвертации

Обеспечьте бесперебойную работу ChromeDriver 125: советы по решению проблемы chromedriver.exe не найдены

Поле комментария, щелчок мышью, специальные эффекты, js-код

Объект массива перемещения объекта JS

Как открыть разрешение на позиционирование апплета WeChat_Как использовать WeChat для определения местонахождения друзей

Я даю вам два набора из 18 простых в использовании фонов холста Power BI, так что вам больше не придется возиться с цветами!

Получить текущее время в js_Как динамически отображать дату и время в js

Вам необходимо изучить сочетания клавиш vsCode для форматирования и организации кода, чтобы вам больше не приходилось настраивать формат вручную.

У ChatGPT большое обновление. Всего за 45 минут пресс-конференция показывает, что OpenAI сделал еще один шаг вперед.

Copilot облачной разработки — упрощение разработки

Микросборка xChatGPT с низким кодом, создание апплета чат-бота с искусственным интеллектом за пять шагов

CUDA Out of Memory: идеальное решение проблемы нехватки памяти CUDA

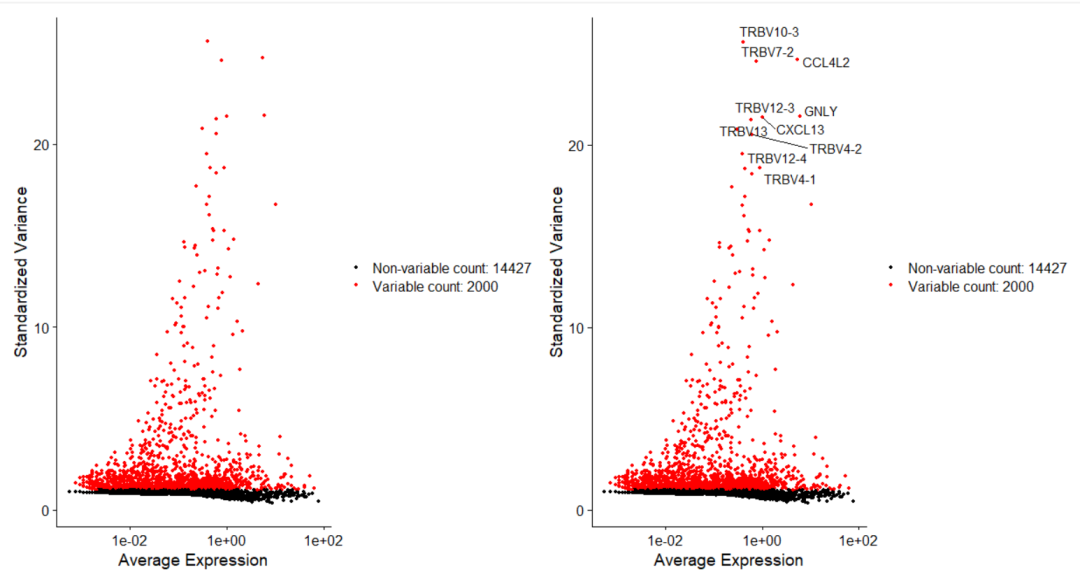

Анализ кластеризации отдельных ячеек, который должен освоить каждый&MarkerгенетическийВизуализация

vLLM: мощный инструмент для ускорения вывода ИИ

CodeGeeX: мощный инструмент генерации кода искусственного интеллекта, который можно использовать бесплатно в дополнение к второму пилоту.

Машинное обучение Реальный бой LightGBM + настройка параметров случайного поиска: точность 96,67%

Бесшовная интеграция, мгновенный интеллект [1]: платформа больших моделей Dify-LLM, интеграция без кодирования и встраивание в сторонние системы, более 42 тысяч звезд, чтобы стать свидетелями эксклюзивных интеллектуальных решений.

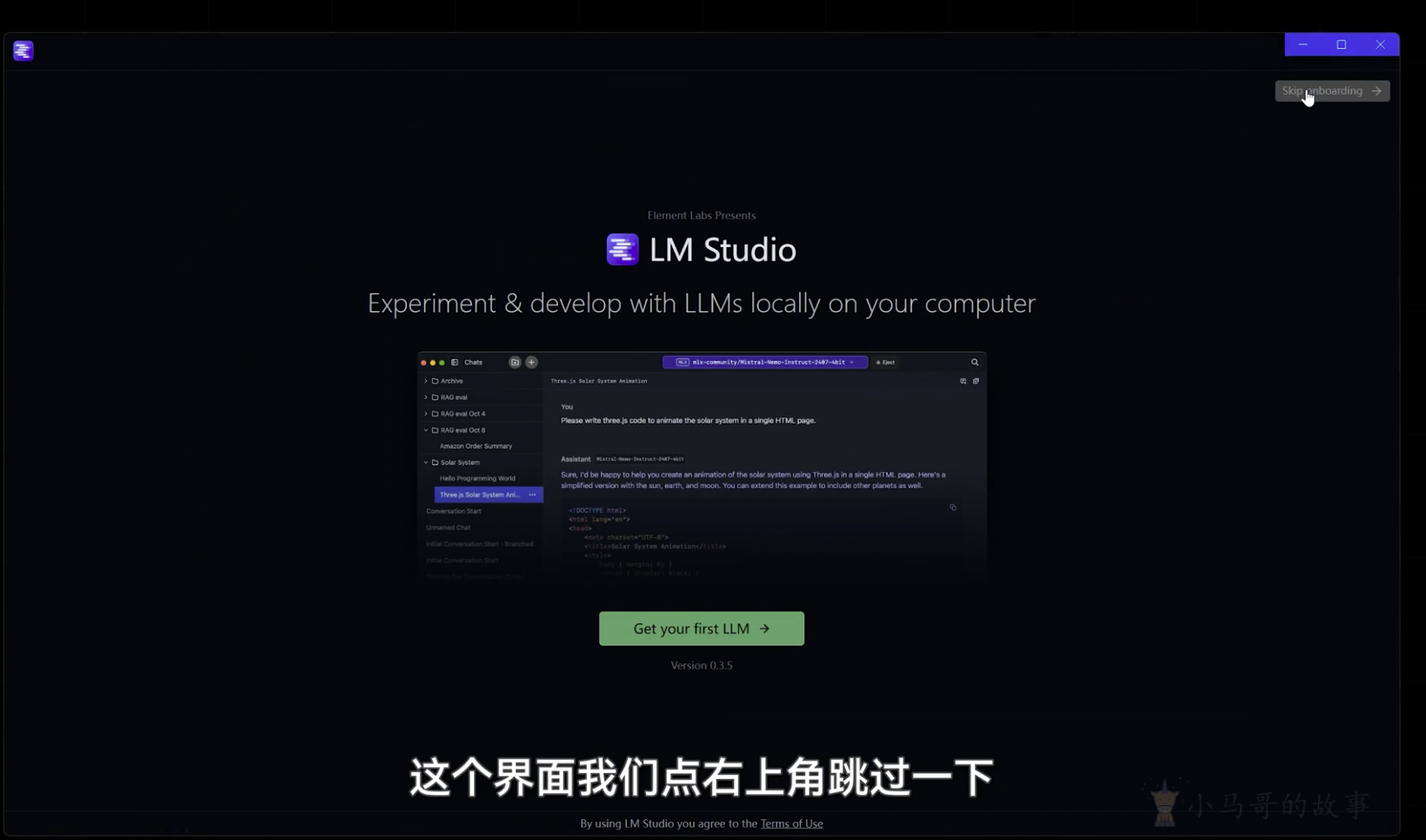

LM Studio для создания локальных больших моделей

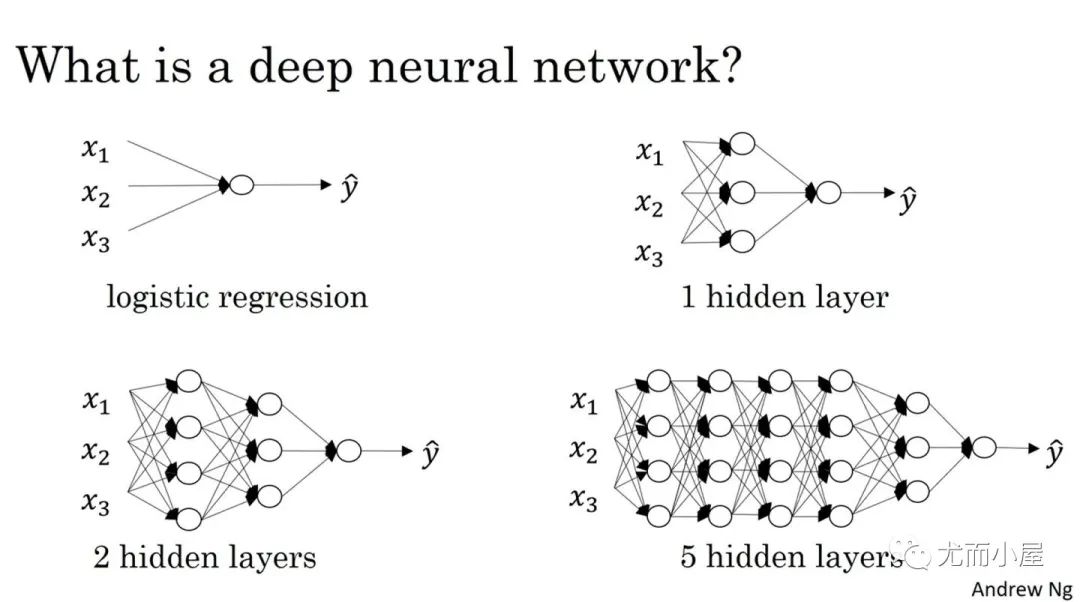

Как определить количество слоев и нейронов скрытых слоев нейронной сети?