Начало работы с RecoNIC: разгрузка вычислений с поддержкой RDMA на SmartNIC-FPGA-SmartNIC-AMD-Xilinx

краткое содержание

Сегодняшние центры обработки данных состоят из тысяч подключенных к сети хостов, каждый из которых оснащен процессорами и ускорителями, такими как графические процессоры и FPGA. Эти хосты также содержат сетевые карты (NIC), работающие со скоростью 100 Гбит/с или выше для связи друг с другом. Мы представляем RecoNIC, платформу SmartNIC на базе FPGA с поддержкой RDMA, предназначенную для ускорения вычислений за счет максимально близкого приближения сетевых данных к вычислениям, одновременно сводя к минимуму необходимость в копиях данных (в системах-ускорителях, ориентированных на ЦП), связанных с накладными расходами. Поскольку RDMA де-факто является протоколом транспортного уровня, используемым для улучшения связи рабочей нагрузки центра обработки данных, RecoNIC включает в себя механизм разгрузки RDMA для передачи данных с высокой пропускной способностью и низкой задержкой. Разработчики имеют возможность создавать ускорители с использованием RTL, HLS или Vitis Networking P4 в программируемых вычислительных модулях RecoNIC. Эти вычислительные блоки могут получать доступ к памяти хоста, а также к памяти удаленных узлов через механизм разгрузки RDMA. Кроме того, механизм разгрузки RDMA используется совместно хостом и вычислительными блоками, что делает RecoNIC очень гибкой платформой. Наконец, мы открываем исходный код RecoNIC для исследовательского сообщества, чтобы дать возможность экспериментировать с приложениями на основе RDMA и вариантами использования.

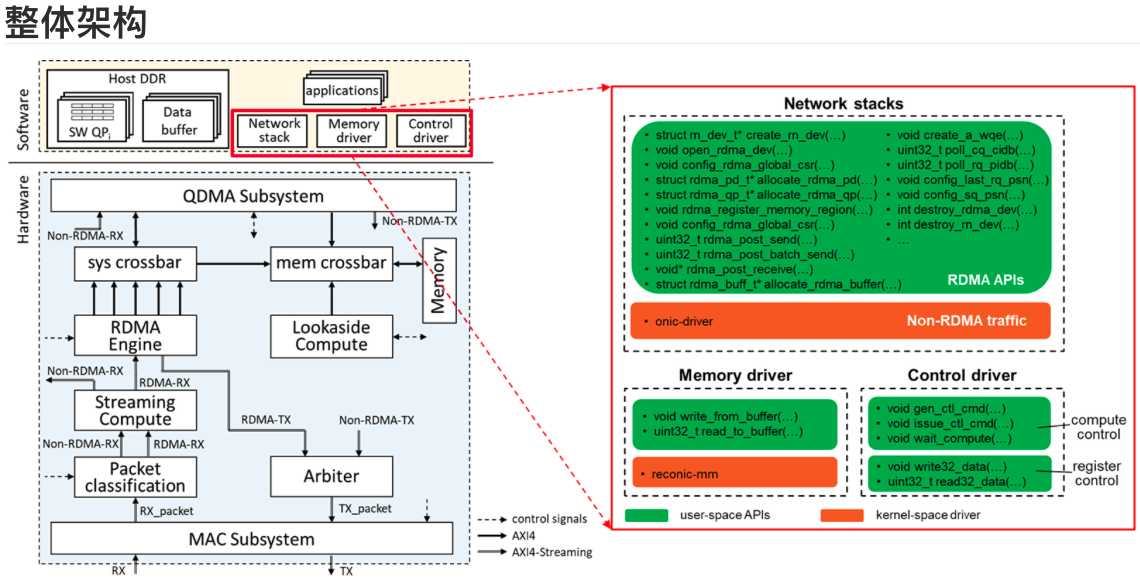

Общая архитектура:

1. Введение

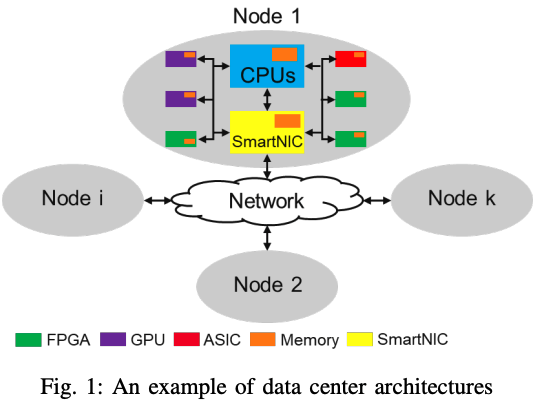

Чтобы справиться со взрывным ростом данных и рабочих нагрузок/приложений, современные центры обработки данных состоят из большого количества подключенных к сети хостов, каждый из которых имеет несколько ядер. CPU и ASIC、FPGA и/или GPU форма ускорителя. Эти хосты используют сетевые карты. (NIC) Взаимное общение. Всего за несколько секунд, центр обработки данныхсетьПропускная способность выросла более чем в 100 раз,от 1GbE повышен до 100GbE Еще выше. Этот замечательный рост намного превосходит CPU Развитие вычислительной мощности. При такой высокой пропускной способности традиционная зависимость от CPU Проведение сетевой обработки и передачи данных приведет к CPU Увеличение использования, что приводит к увеличению задержек, снижению пропускной способности и увеличению затрат на предоставление услуг центра обработки данных клиентам. [1]。 Это привело к SmartNIC появление технологий [1], [4], что удаляет сетевые функции с хоста CPU Выгрузить в SmartNIC начальство. В этой архитектуре центра обработки данных SmartNIC Играет жизненно важную роль, выступая в роли промежуточного узла, как показано на рисунке. 1 показано.

Весь сетевой трафик проходит через SmartNIC передается на различные вычислительные элементы, например. CPU、GPU、FPGA и ASIC。 Служит партнером для внешних сетевых подключений. Существуют различные SmartNIC архитектуры, в том числе на основе ASIC решения (например, оснащенные RDMA Удалить ARM процессор NVIDIA BlueField [4]), на основе P4 Программируемые конструкции (напр. AMD Pensando [5])ина основе FPGA из SmartNIC (например, AMD Alveo SN1000) [6] и Microsoft Azure SmartNIC [1])。 Хотя с ASIC и P4 По сравнению с программируемыми решениями на основе FPGA ИзSmart NIC Кривая обучения более крутая, но Microsoft Azure центр обработки данных [1] было продемонстрировано на основе FPGA Достигнуто масштабное развертывание интеллектуальной сетевой карты CPU Невозможно достичь извысокой производительность и эффективность и обеспечивает программируемость, выходящую далеко за рамки ASIC Мы можем предоставить широкий ассортимент продукции по разумной цене. В этой работе мы в основном концентрируемся на FPGA из SmartNIC решение. центр обработки Спрос на рабочие нагрузки в области данных продолжает расти, включая обучение машинному обучению/высокая обработка выводов. производительность вычислительных приложений, нуждаться в высокой пропускной способности, низкой задержке и минимальной CPU Накладные расходы из высокоскоростного набора. Эта потребность стимулирует удаленный прямой доступ к памяти. (RDMA) из появляется и становится скоростным центром обработки данныхсетьизфактначальствоизстандарт. RoCEv2 (начальное руководство по конвергентному Ethernet) RDMA Версия 2) Как популярный из RDMA Соглашение выделяется в NVIDIA BlueField и т. д. на основе ASIC из SmartNIC Получите хорошую поддержку и удалите [4]。 Однако существующие основе FPGA из SmartNIC [1]、[2]、[7]、[10] верно RDMA Удализ имеет ограниченную поддержку. Мы запускаем RecoNIC, который является поддержкой RDMA из Открытый исходный код SmartNIC Имея функцию ускорения вычислений, он направлен на достижение дополнительного ускорения вычислений в сети и минимизацию накладных расходов, связанных с копированием данных. Разработчики имеют возможность RecoNIC изпрограммируемый вычислительный модульиспользовать RTL、HLS или Vitis Networking P4 проектировать ускорители。 Это позволяет обрабатывать сетевые данные без необходимости создания нескольких копий данных, что часто имеет место в традиционных системах. CPU Для центра из решения из характеристик. На основе FPGA из SmartNIC может трансформировать традиционные CPU Центрированные решения трансформируются в FPGA Для центра решений существует хранилище данных «Воласеть». SmartNIC изоборудования Память, от и значительно снижено PCIe начальствоиз Скопируйте данные и сохраните их как можно ближе к расчету. Выполнение логики внутри блоков вычислений пройти RDMA Доступ к удаленной вере и другим точкам в из Хозяини Память устройства. Наш вклад можно резюмировать следующим образом:

• Реко НИК, ПЛИС, поддержка RDMA из Открытый исходный код SmartNIC платформа.

• RecoNIC Поддержка РДМА и нетRDMA трафика, а также потоковую передачу и резервное ускорение вычислений. Расчетные блоки позволяют пользователям проходить Vitis Networking P4、HLS и RTL Ускоритель развития.

• RDMA удалитьдвигатель Зависит от ХозяинCPU(проходитьPCIe)иFPGA Вычислительные блоки являются общими, что делает платформу очень гибкой. RDMA очередьверно (QP) Можетсуществовать Хозяинилиоборудование Памятьначальствораспространять

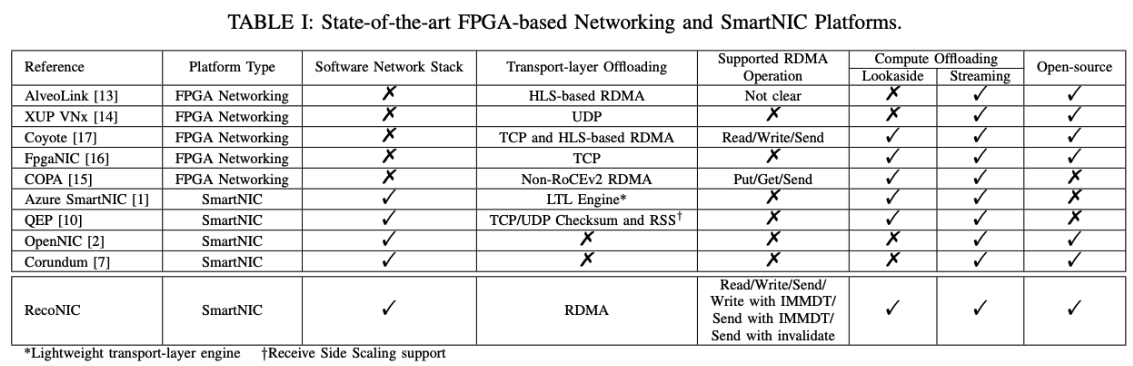

поверхность Я: Самый продвинутый изна основе FPGA изсетьи SmartNIC платформаверно Сравнивать

2. Сопутствующая работа

на основе FPGA изсети решения можно разделить на две категории: основе FPGA изсетьплатформаина основе FPGA из SmartNIC платформа. на основе FPGA исетьплатформа может работать как автономный узел и оснащена механизмом разгрузки транспортного уровня, механизмом контроля доступа к среде (MAC) Компоненты, обеспечивающие адаптивные ускорители общение. на основе FPGA из SmartNIC действовать как NIC, в дополнение к некоторым расширенным сетевым функциям, предоставляет хосту CPU Обеспечивает стандартную сетевую функциональность. Основные различия между этими двумя категориями заключаются в следующем:

• на основеFPGA изSmartNIC Платформа может заменить традиционные сетевые карты (NIC) и обеспечиваем стандарты NIC Такие функции, как выполнение стека программного обеспечения, обрабатывающего различные протоколы, управление трафиком и поддержка виртуального коммутатора. 。

• на основеFPGA изSmartNIC может поддерживать дополнительные сетевые карты платформы Такие функции, как измерение и телеметрия с различными протоколами, выполняются с удалением или без него.

• на основеFPGA изSmartNIC Платформа способна обрабатывать 4-е протоколы уровня и начального уровня, эти протоколы не будут использоваться в качестве протоколов транспортного уровня. Выгрузить ваппаратное обеспечениесередина.

поверхность I Обзор доступных новейших технологий основе FPGA изсетьи SmartNIC платформа.на основе FPGA изсетьплатформа [13]、[14]、[15]、[16]、[17] включать Оснащен двигателем разгрузки транспортного уровня и продублирует эти соединения двигателя из других плат FPGA, встроенных в коммуникацию. Однако,потому что не хватает мягких частей сетевого стека, эти платформы не могут поддерживать свой транспортный уровень удалить двигатель Не поддерживаетсяиз Нет. 4 протоколы уровня с другими устройствами (FPGA Запрет или Традиция NIC) для связи. Напротив, на основе FPGA из SmartNIC платформа [1]、[2]、[7]、[10] Используйте программные сетевые стеки для связи с другими устройствами, независимо от того, FPGA Совет по-прежнему традиционный NIC。 Однако большая часть основе FPGA из SmartNIC платформа [2], [7], [10], в дополнение к поддержке, обеспечиваемой легким транспортным слоем разгрузочной машины Microsoft Azure SmartNIC [1] Кроме того, все они сильно зависят от хоста. CPU Процесс Сетевые данные. Эта зависимость может привести к недостаточной пропускной способности и высокой задержке, особенно на высоких скоростях. (>= 100Gb/s) середина. RDMA такое машинное обучение ивысокая производительность высокоскоростной передачи данных в вычислительных приложениях коммуникацияизфакты начальствоизстандарта. Стоит отметить, что это самый продвинутый основе FPGA из SmartNIC платформа [1]、[2]、[7]、[10] Не поддерживается RDMA。 существоватьна основе FPGA иссетьплатформа, три рабочих места [13]、[15]、[17] включать RDMA Деинсталлируйте двигатель. COPA [15] Используйте не- RoCEv2 RDMA сними двигатель пока AlveoLink [13] и Coyote [17] Затем используйте на основе HLS из RDMA удалитьдвигатель,нравитьсяповерхность I показано.AlveoLink из RDMA двигатель [13] иметь AXI4-Streaming интерфейс, Отсутствие поддержки по этому поводу со стороны RDMA Исчерпывающая информация по эксплуатации. Напротив, Койот [17] Разработан индивидуальнона основе HLS из RoCEv2 RDMA изSimplify Версия, поддержка RDMA Операции чтения/записи/отправки. существующаяизна основе FPGA По сравнению с иссетплатформа[13], [14], [15], [16], [17], RecoNIC это одининдивидуальныйна основе FPGA из SmartNIC можно использовать мягкий стек платформы для управления кросс-сетью не RDMA поток. Различные протоколы транспортного уровня, не все эти протоколы аппаратно Деинсталлируйте двигатель. существуют самые передовые изна основе FPGA из SmartNIC платформа [1]、[2]、[7]、[10] Когда, Реко НИК Обеспечить адаптивный SmartNIC инфраструктура, обеспечивающая RoCEv2 RDMA Удалить двигатель и резервную версию и потоковую передачу Для дополнительного ускорения сети из расчетного блока

3. Платформа РЕКОНИК

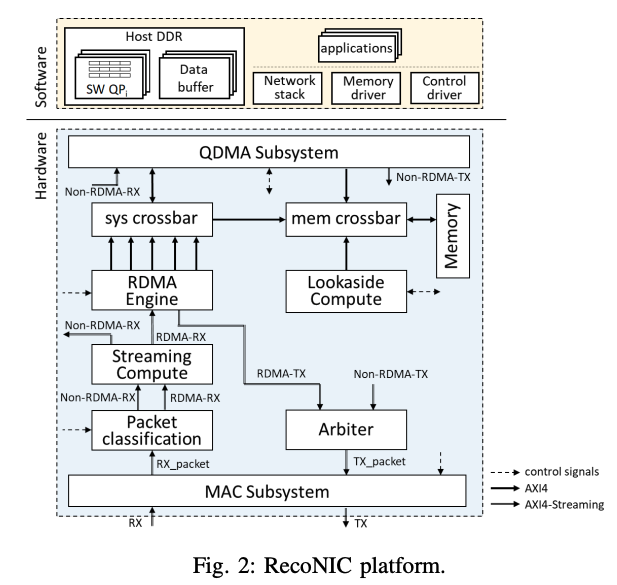

RecoNIC платформанравитьсякартина 2 Как показано,Зависит отаппаратное обеспечениеимягкийэлемент виджетасостав. Аппаратная оболочка включает Классификацию пакетовмодуль、RDMA двигатель, два индивидуальных программируемых вычислительных модуля (Lookaside и потоковые вычисления) и включить MAC Подсистемаи DMA Подсистема (QDMA) изBasic NIC модуль. Кроме того, он содержит связующую логику, такую как система/Память перекладины и арбитра. RDMA двигатель отвечает за обработку RDMA Трафик, обеспечивает возможность получить доступ к соединению из удаленных верных и других точек и з Хозяинили оборудование Память из данных. Пользовательский ускоритель, реализованный в блоке потоковых вычислений и резервных вычислений, может непосредственно обрабатывать данные в устройстве Память и, включительно, получать эти данные. Что касается программного обеспечения, оно содержит три компонента: (1) Сетевой драйвер, управление TCP/IP、UDP/IP、QUIC и ARP Подождите, пока не RDMA поток; (2) «Памятьводитель» для обеспечения бесперебойной передачи «Память» между устройствами Хозяини; (3) контрольводитель, отвечающий за настройку различных компонентов аппаратной оболочки.

A. RDMA двигатель RecoNIC использовать AMD ERNIC IP [3] как это RDMA Удалите двигатель, который разработан в соответствии с RoCEv2 стандарт. ERNIC IP Первоначально использовался как встроенный RDMA мягкий IP,иметь Зависит от ARM или MicroBlaze Оркестровка процессора из-под контроля операций. RecoNIC из уникальности существуют, кроме программируемого вычислительный Помимо блока это может быть и Воля ERNIC IP и x86 Хозяин CPU интерфейс. RDMA двигательиметьдваиндивидуальныйиспользуется для RDMA RX/TX Пакет данных AXI4-Streaming Интерфейс ввода/вывода индивидуальный AXI4-MM интерфейс, используемый для получения элементов рабочей очереди, обработки данных полезной нагрузки и записи записей очереди завершения. Кроме того, РДМА двигательиз Конфигурацияпроходить PCIe AXI4-Lite Интерфейс завершен. RecoNIC Еще одной примечательной особенностью индивидуального является возможность гибкого распределения очередей в существующем Хозяин Памятьили оборудование Память (QP) и буфер полезной нагрузки. Двигатель RDMA может быть предоставлен в соответствии со смещением адреса, полученнымsys. crossbarиmem Crossbar обращается к этим буферам QPи. Например, в текущей реализации память устройства (16 ГБ DDR4)из диапазона адресовот 0xa350000000000000 приезжать 0xa3500003ffffffff, создавая таким образом 12 Кусочек MSB маска (т. 0xa35)。 Следовательно, любой имеет 0xa35 MSB из QP или Адреса буфера полезной нагрузки считываются в устройстве «Воляот Память».

B. программируемый вычислительный блок Существует два типа расчетных блоков: LC-loaside. вычислительные) блочные и потоковые вычисления (SC-streaming) вычислительный) блок. LC Блоки настроены на поддержку доступа Память (например, умножение матриц) и ускорителей. Напротив, СК Блок, предназначенный для нуждаться в обработке входящего пакета в потоковом режиме. Предназначен для приложений обработки данных.,Например Обработка пакетовисетьтелеметрия。

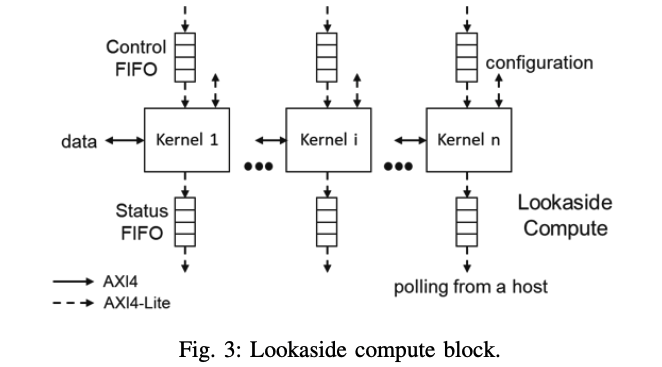

1) Резервный расчет (LC):нравитьсякартина 3 Как показано,

LC Блок может вместить несколько отдельных ядер возможностей. Эти ядра можно использовать HLS Инструменты RTL Кодирование для производства. Каждое ядро оснащено блоком управления. FIFO иодининдивидуальныйсостояние FIFO。 контроль FIFO Получить от Хозяина CPU новости изконтроля. контрольное сообщение похоже на вызов C Список параметров функции поверхности. Например, это может быть структура данных, состоящая из уникального идентификатора рабочей нагрузки, ряда параметров адреса и этих адресов в качестве параметров. Для запуска ядра Хозяин CPU может пройти AXI4-Lite Интерфейс для управления FIFO Отправить контрольное сообщение. одинрассветконтроль FIFO Если оно не пусто, ядро получит контрольное сообщение и начнет выполнение. использовать сообщение контроля в изадресе, ядро может пройти AXI4 Интерфейс данных получает доступ к данным, хранящимся в устройстве Хозяинили Память. Ядро может поддерживать несколько AXI4 интерфейс для увеличения пропускной способности доступа к Память и разрешения Хозяину CPU проходить AXI4-Lite Интерфейс обращается к регистрам, отображаемым в памяти. После завершения выполнения ядро выдает ассоциацию статуса FIFO Сигнализируйте о своем статусе. из статуса FIFO из пустого сигнала можно подключиться Система прерываний PCIe/Хозяиниз илииспользовать Память отображаемого регистра из системы опроса. система прерываний существует запроектировано, когда состояние FIFO Если не пусто, LC Ядро вызовет системное прерывание и позволит Хозяину обработать его соответствующим образом. При проектировании системы опроса, когда статус FIFO Когда носитель готов, LC Ядро записывает сигнал завершения в выделенный регистр, отображаемый в памяти. Хозяин следит за специальным регистром стоимости и реагирует соответствующим образом. О том, как LC Для объяснения ядра дизайна в модуле, пожалуйста, обратитесь к Нет. IV-C Фестиваль.

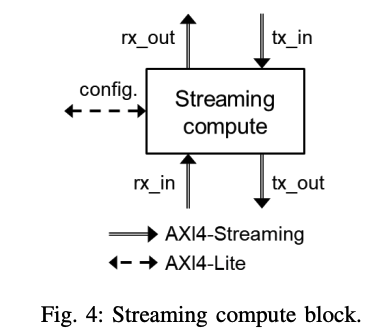

2) Потоковые вычисления (SC):SCкусокнравитьсякартина4Как показано,

Он предназначен для приложений, способных обрабатывать сетевой трафик в потоковом режиме. Используется для входного и выходного трафика сети. AXI4-Streaming интерфейс. SC Блокировать из ядра можно Vitis Networking P4 [12]、HLS или RTL Кодирование для достижения. О том, как SC Ядро внутриблочного проектирования из описания см. Нет. IV-D Фестиваль.

C. Классификация пакетов PКлассификация Модуль пакетов предназначен для классификации входящего сетевого трафика как RDMA и нет RDMA поток. RDMA Движение осуществляется за счет RDMA ручка двигателя, а не RDMA Трафик перенаправленприезжать QDMA Подсистема,Зависит от Хозяинначальствоизсетьводитель Впередииметь дело с。

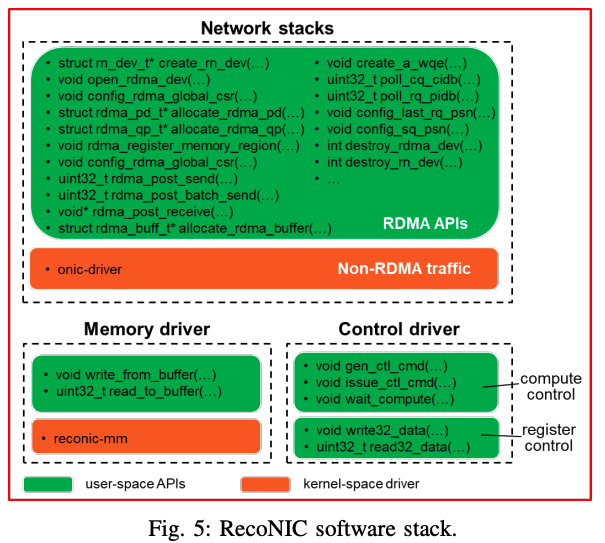

D. мягкая стопка кусочков RecoNIC измягкая стопка кусочковнравитьсякартина 5 Как показано,

Зависит отпространство ядраводительипользовательское пространство API состав.

- Драйвер пространства ядра предоставляется onic-driverreconicmmsoстав. onic-driver [9] это одининдивидуальныйна основе AMD qep-driver [10]、OpenNIC водитель [2] и libqdma [11] исетьводитель, поддержка не- RDMA поток. reconic-mm Это индивидуальное символьное устройство водитель, используемое для обработки запросов на чтение/запись от устройства Хозяиниз Память. onic-driver существовать RecoNIC был расширен для поддержки QDMA AXI4-Memory-Mapped канал и renic-mm Сотрудничайте сиспользуйте, чтобы получить доступ к устройству Память.

- пользовательское пространствоAPIвключать ПамятьAPI、контрольAPIиRDMA API。 Память API Устройство доступа для от Хозяин Память и контроля API серединаиз контроля расчета и контроля регистрации API соответственно предназначен для Lookaside Compute Блокировка контроля регистрации конфигурации. RDMA API предоставилиспользовать RDMA двигатель Отправить и получить RDMA Требуемый трафик из функции. пользовательское пространство API компилируются и группируются в libreconic библиотека. связанныйпользовательское пространство API Для получения дополнительной информации см. RecoNIC Репозиторий из lib Создать в папке doxygen документ

4.Пример

В этом разделе мы описываем RecoNIC В репозитории есть несколько индивидуальных примеров: DMA Тест, РДМА Тест, сеть Умножение матрицы систолического массива и Классификация пакетов。

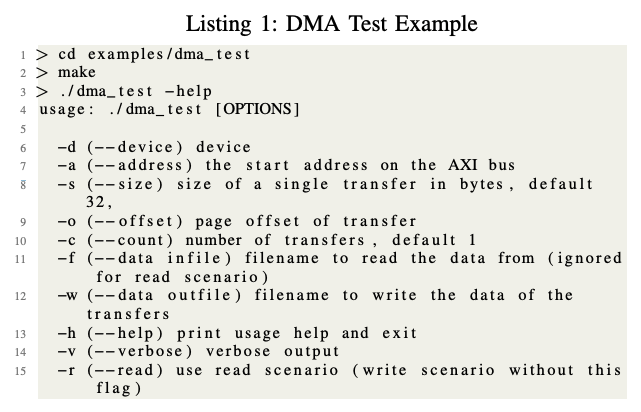

A. DMA тест, DMA В тестовом примере оценивается функциональность копирования данных между устройствами Хозяини Память. когда Хозяиндействовать как главное устройство, оно поддерживает, да NIC Памятьиз читать и писать. Его использование похоже на список 1 показано.

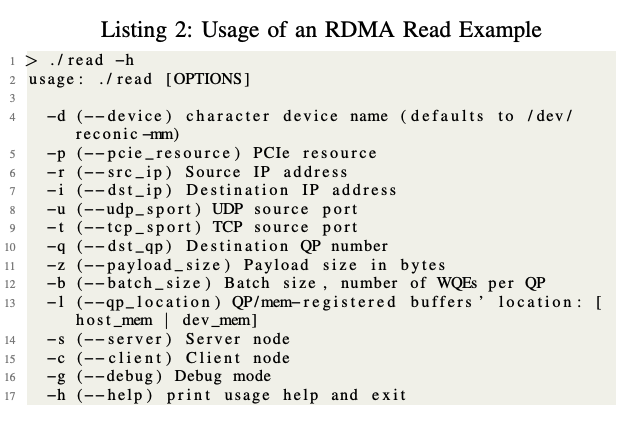

B. RDMA тест, RDMA Тесты включают использование libreconic API из RDMA Чтение, запись, отправка/получение и пример пакетного чтения/записи. Эти примеры соответствуют модели клиент-сервер, а элементы рабочей очереди описаны ниже. (WQE), очередь отправки (SQ), очередь приема (RQ),очередь завершения (CQ) иочередьверно (QP; автор SQ、RQ и CQ) термин.

• Чтение: клиентский узел отправляет серверному узлу запрос на чтение RDMA (один WQE на каждый дверной звонок SQ). Затем серверный узел отвечает пакетом ответа на чтение RDMA.

• Запись: клиентский узел отправляет запрос на запись RDMA непосредственно серверному узлу (один WQE на каждый дверной звонок SQ).

• Пакетное чтение(Пакетное чтение Читать): Клиентский узел передает соответственно количество запросов (размер пакета) в пакете. SQ Дверной звонок, который отправляет пакет на серверный узел RDMA запрос на чтение (каждый QP из группы WQE, имеют одинаковый размер полезной нагрузки). Затем серверный узел последовательно отвечает пакетами ответа на чтение RDMA.

• Пакетная запись Запись): клиентский узел отвечает в соответствии с размером пакета. SQ дверной звонок, отправка пакетов напрямую на серверные узлы burst RDMA, запрос на запись (каждый QP Группа одинаковых размеров груза из WQE)。

• Отправка/получение: серверный узел публикует RDMA. Получите заявку и дождитесь ее выделения изRQ изRDMA Отправить запрос. Затем клиентский узел выдает серверному узлу RDMA Отправить запрос.

Контрольный список 2 Показывает эти сценарии использования.

проходитьинструктировать“-l host mem”или“-l dev mem”,МожетсуществоватьХозяин Памятьилиоборудование Памятьсерединараспространять QP。

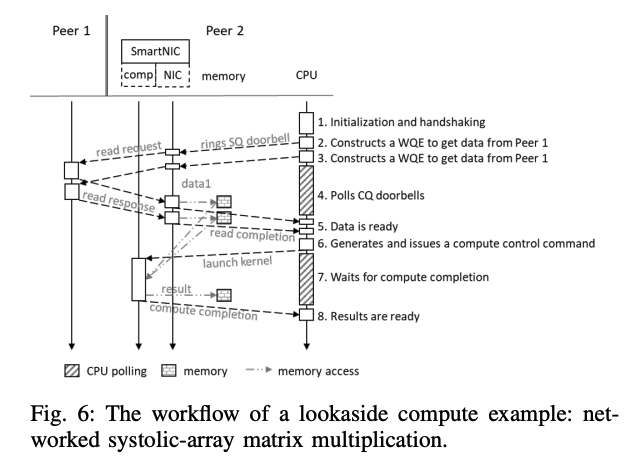

C. Резервный расчет: умножение матриц

Пример расчета резервного варианта описывает умножение матрицы сетевых подключений. (MM) Ядро по принципу работы. MM Расчет основе HLS C Среда из реализации систолического массива (следуйте Vitis [8] Один из примеров в из). В настоящее время из орудий используются два индивидуальныхверно и др., где данные хранятся в существующеверно и др. 1 и MM Рассчитать оборудование RecoNIC(действовать как SmartNIC) изверно и другие моменты 2 Законченный. картина 6 Объяснен рабочий процесс.

Peer2 от Peer1 Получите данные, выполните расчеты, затем сообщите об этом Хозяину CPU。

по Шагам1, ХозяинCPU инициализирует систему, устанавливает соединение, и иpeer1 обменивается информацией.

по шагам2и3, CPUсуществовать выделение изSQ сборки WQE, и прозвонить соответствующую изSQдверной Звонок, эта Воля запускает двигатель RecoNIC изRDMA для отправки запроса на чтение.

Затем процессор по шагам 4 При проведении опроса соответствующего из CQ Дверной звонок ждет звонка Peer1 изданные.

Как только данные RecoNIC изRDMAдвигатель Воля будут сохранены в его памяти, он шагам5серединапроходитьсуществоватьсоответствующийизCQдверной Звонок начальника отправляет сигнал завершения чтения, чтобы уведомить Хозяин ЦП. Затем,

по На шестом этапе ХозяинCPU генерирует команды управления вычислениями для ядра в резервном блоке вычислений. Во время выполнения ядра процессор по На шагах7 проводится опрос или прерывание ожидает сигнала завершения расчета. После того как расчет завершен и результат сохраняется в существующей памяти, по шагам8, ЦП может продолжить обработку следующего индивидуального запроса на расчет. существоватькогдавпередиз RecoNIC При реализации Хозяин несет ответственность за все контрольные операции. Однако эти контрольные операции могут существовать в будущем. в RecoNIC。

D. Потоковые вычисления:Классификация пакетов shell/-Классификация пакетов Оглавлениесерединаиз Классификация пакетов (PC) Блок иллюстрирует блок потоковых вычислений, где входящие пакеты классифицируются как RDMA и нет RDMA пакет. NonRDMA поток Впередприезжать Хозяин(проходить QDMA AXI-Streaming интерфейс), в то время как RDMA Движение осуществляется за счет RDMA двигательиметь дело с。 Блок PC написан на языке P4 и используется для анализа заголовков пакетов и генерации соответствующих метаданных, которые можно использовать для классификации трафика. Поля заголовка пакета. Некоторые примеры включают Ethernet, IP, UDP, RoCEv2. основные транспортные заголовки (BTH)、RDMA Расширенный транспортный заголовок (RETH)、ACK Расширенный транспортный заголовок (AETH), немедленные данные Расширенный транспортный заголовок (ImmDt) иневерный Расширенный транспортный заголовок заголовок (IETH). Затем,использовать Vivado Доступно в Vitis Networking Р4 (аббревиатура VitisNetP4, ранее известный как SDNet)[12] Воля P4 Реализация преобразована в RTL выполнить. Затем Воля RTL Осуществить интеграциюприезжать RecoNIC дизайнсередина. Дополнительная информация по ссылкеshell/Классификация. пакет/packet parser.p4

5. Эмуляция оборудования

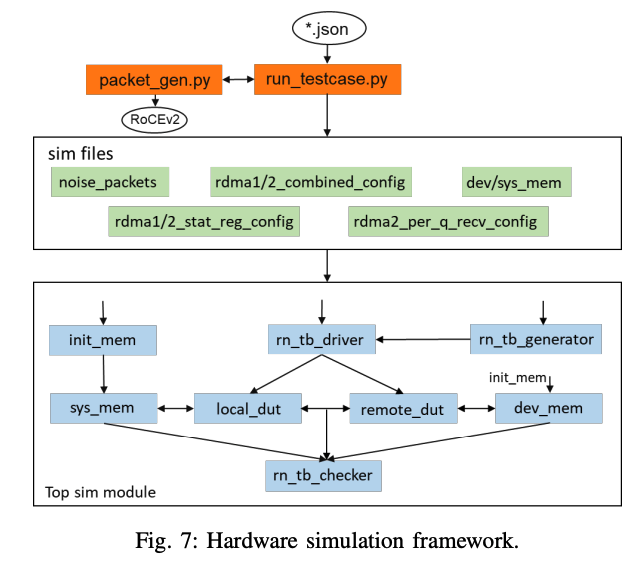

Фреймворки эмуляции оборудования, такие как картина7показано.

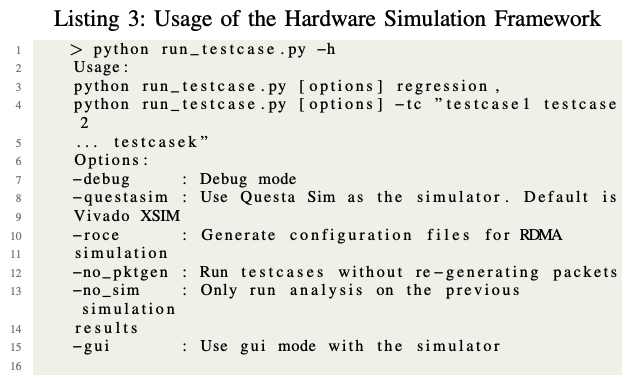

Идея этой платформы заключается в том, что Python генерирует файлы конфигурации RDMA на основе определяемых пользователем файлов JSON и позволяет модулю тестирования оборудования соответствующим образом настраивать RDMA. Таким образом, пользователю необходимо лишь изменить JSON Файлы конфигурации могут создавать несколько тестовых примеров, образуя более простую и гибкую среду тестирования и отладки. Сценарий Mock framework использует скрипт testcase.py, поддерживающий регрессионное тестирование. Стимулы, метаданные контроля и золотые данные packet gen.py Генерация скриптов, в которых пользователи могут указать свои собственные JSON файл в sim/testcases Создайте новые тестовые примеры в каталоге. бегать testcase.py Скрипт Воля автоматически читает эти сгенерированные файлы и записывает их как AXI В потоковом формате формируются пакеты, а также все сигналы, связанные с контролем (например, RDMA). Файл конфигурации включает регистр глобального контроля, регистрацию Память, QP. и WQE зарегистрируйтесь в конфигурации и статистический регистр). верно Для моделирования с точностью до цикла инфраструктура поддерживает Questa эмулятор (questasim) и Vivado эмулятор (xsim)。 Для получения дополнительной информации попробуйте использовать опцию «отладка» в примерах моделирования, таких как «Контрольный». список 3 Как показал,и проверь Кусочек на sim/testcases/your sim example из Создать файлы

6. Экспериментальная оценка

A. системные требования, Все последующие эксперименты проводились на компьютере со следующими настройками:

• Два сервера, каждый с возможностью проходить PCIe 3.0 x16 Розеточное подключение из AMD Alveo U250 FPGA Карта.

• Два Альвео U250 Картапроходить100Gb/s Кабельное прямое подключение или проход 100Гбит/с подключение переключателя.

• Ubuntu 20.04 и ядро Linux версии 5.4.0-125-generic.

• Python >= 3.8

• Vivado 2021.2,иметь Vitis Networking P4 и ERNIC лицензия

• Questa эмулятор 2021.3 (для моделирования)

Б. Производительность DMA

(1)Хозяин доступен как основное устройство RecoNIC оборудование Память:существоватьэта сценасередина,Хозяин CPU проходить QDMA AXI4-MM доступ к каналу FPGA Память устройства. DMA Эффективная пропускная способность чтения и записи соответственно равна ∼13.00 GB/s и ∼13.07 ГБ/с, да PCIe 3.0 x16 Теоретическая пиковая пропускная способность слота 82.5%。

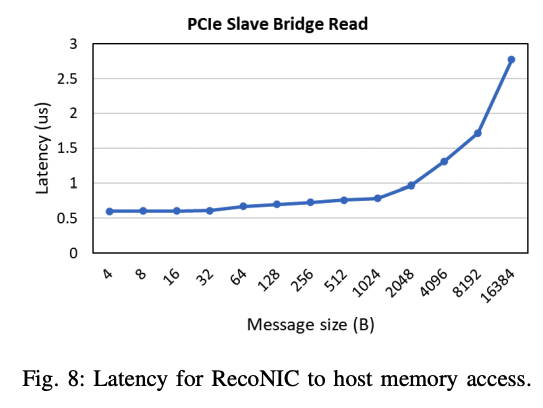

(2) RecoNIC как Хозяиндоступ Хозяин Память:существовать В этом случае,FPGA логикадействовать как Хозяинпроходить QDMA отмостинтерфейсдоступ Хозяин Память。 картина 8 Сообщается о задержке, размере сообщения и функциональной взаимосвязи, где FPGA нуждаться ∼600 ns приезжать ∼964 ns Чтобы получить доступ к небольшим новостям (<= 2048 B)。

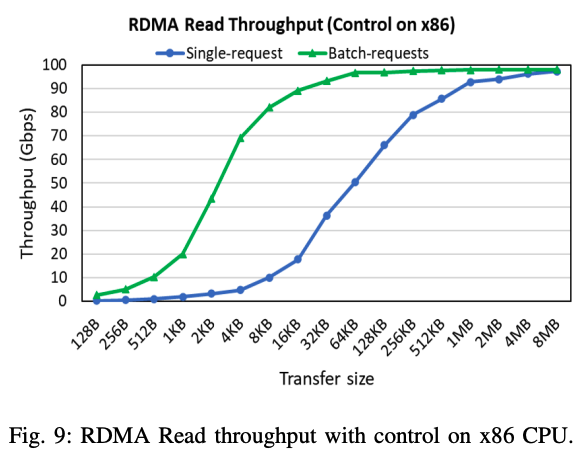

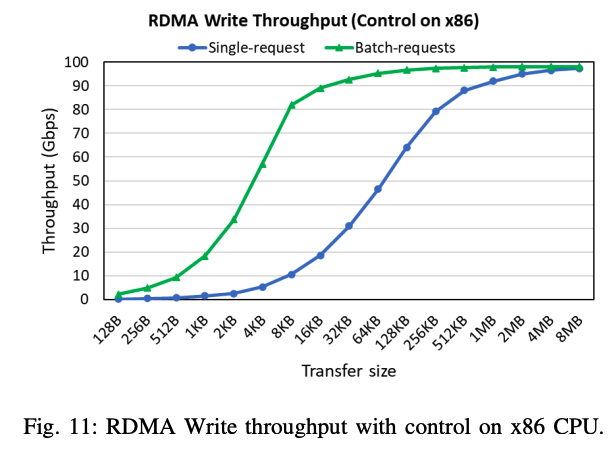

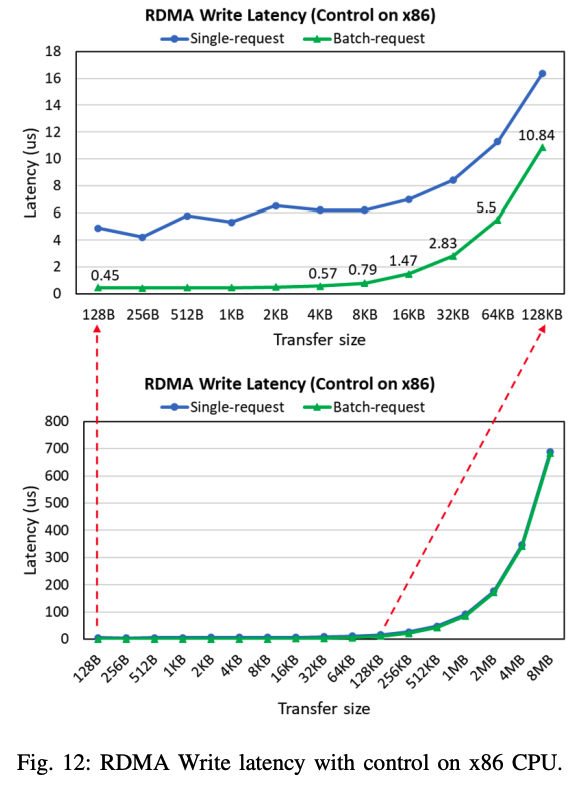

C. Производительность чтения/записи RDMA. В тесте чтения/записи RDMA мы используем два метода:

(1) измерить каждый WQE изпроизводительность, называемая единичным запросом;

(2) отмерить партию WQE означает производительность, называемую пакетным запросом. В методе массового запроса мы создаем n отдельные люди имеют одинаковый размер полезной нагрузки WQE, нажмите один раз SQ дверной звонок(Иголкавернонаконецодининдивидуальный WQE) и опрос CQ дверной звонок (вернее, стежок делается несколько раз), а не для каждого отдельного человека WQE серийный звуковой сигнал SQ дверной звонок и голосование CQ дверной звонок Как это сделано в рамках единого отдельного запроса. Мы используем н = 50, Хозяин ЦП отвечает за подготовку WQEиз, SQдверной звонокиз Звонить в колоколиCQдверной звонокиз Опрос.

картина 9 икартина 10 сообщается отдельно RDMA Пропускная способность чтения, задержка, размер передаваемых данных и функциональная взаимосвязь. Массовый запрос пропускной способности намного лучше, чем одиночный индивидуальный запрос пропускной способности, например, при передаче 16 KB При этом пропускная способность пакетных запросов составляет приблизительно 89 Гбит/с, а пропускная способность одного запроса составляет примерно 18 Gb/s。 Кроме того, пакетные запросы могут достигать скорости, близкой к скорости линии (ок. 92 Гбит/с), а размер данных намного меньше (32 KB)。 существовать Задержка,когда Передача небольшого размера данных(<= 4 КБ), пакетный запрос может достичь почти 10 Улучшение в разы, то есть каждый раз RDMA Прочитайте операцию прибл. 400 ns。 Операция записи RDMA с учетом пропускной способности и задержки соответственно, как картина11икартина12Как Как видно, его тенденция аналогична операциям чтения RDMA. Основной причиной значительного увеличения пакетных запросов на производительность является SQ дверной звонок Звонить в колоколи CQ дверной Опрос звонков из-за накладных расходов значительно сокращается. потому чтодверной звонок Звонить в колоколи Опроспроходить PCIe AXI4-Lite Интерфейс выполняется как операция чтения/записи регистра, которая по своей сути медленна, поэтому каждый n индивидуальный WQE SQ дверной звонок один раз CQ дверной однократный опрос звонка значительно снижает общую задержку. Кроме того, когда двигатель RDMA отмечает, что приезжает его производитель SQ, индекс дверной Когда звонок увеличивает n, он выполняет n отдельных операций чтения в конвейерном порядке. Например,несмотря на PCIe отмостнуждатьсяо 170 индивидуальныйцикл(680 ns)вернуться Нет.одининдивидуальный ВКС, но RDMA двигатель доступен за ок. 10 индивидуальныйцикл(40 нс) получить последующее наблюдение WQE。 Таким образом, по PCIe Автобус вызывает длительные задержки и накладные расходы пройтиодин Запуск и выпуск множестваиндивидуальный WQE Приходите, поделитесь. проходить PCIe Автобус находится в CQ Поведение, подобное приезжать, наблюдается при написании нескольких индивидуальных записей.

7. Заключение

Эта работа знакомит RecoNIC, это индивидуально основе 100Gb/s FPGA из SmartNIC платформа,оборудованный RDMA Разгрузите двигатели ускорения вычислений и сделайте их доступными в виде открытого исходного кода для более широкого исследовательского сообщества. Мы предоставляем и объясняем RecoNIC использовать встроенные примеры и обсуждать структуру эмуляции оборудования для отладки и тестирования. Наконец, мы обложили поверхность RecoNIC начальство RDMA Операции чтения и записи изпроизводительности. мы надеемся RecoNIC Воля позволяет исследователям создавать интересные дополнительные варианты использования ускорения.

ссылка

проект: https://github.com/ssbandjl/RecoNIC

бумага: https://arxiv.org/pdf/2312.06207

OFA2024: https://www.openfabrics.org/2024-ofa-virtual-workshop-agenda/

[1] D. Firestone、A. Putnam、S. Mundkur、D. Chiou、A. Dabagh、M.、Andrewartha、H. Angepat、V. Bhanu、A. Caulfield、E. Chung、H. K. Chandrappa、S. Chaturmohta 、M. Humphrey、J. Lavier、N. Lam、F. Liu、K. Ovtcharov、J. Padhye、G. Popuri、S. Raindel、T. Sapre、M. Shaw、G. Silva、M. Sivakumar、N Srivastava、A. Verma、Q. Zuhair、D. Bansal、D. Burger、K. Vaid、D. A. Maltz и A. Greenberg,“Azure Сеть ускорения: публичное облако в SmartNIC»,Том. 15 сессия USENIX Конференция по проектированию сетевых систем иосуществлять(NSDI'18),Нет. 51-64 Страница.

[2] AMD,«Проект AMD OpenNIC»,https://github.com/Xilinx/open-nic,Время доступа: 04.09.2023.

[3] AMD,“AMD ERNIC”,https://www.xilinx.com/products/intellectual-property/ef-di-ernic.html,доступвремя:2023 Год 10 луна 31 день.

[4] NVIDIA,“NVIDIA BlueField”,https://www.nvidia.com/en-sg/networking/products/data-processing-unit/,доступвремя:2023 Год 11 луна 7 день.

[5] AMD,«Программируемый блок обработки данных AMD Pensando P4»,https://www.amd.com/en/accelerators/pensando,Время доступа: 07.11.2023.

[6] AMD,“AMD Alveo SN1000 SmartNIC”,https://www.xilinx.com/products/boards-and-kits/alveo/sn1000.html,доступвремя:2023 Год 11 луна 7 день.

[7] A. Forencich、A. C. Snoeren、G. Porter и G. Папен, «Корунд: открытый исходный код». 100 Gbps Nic”,2020 Год IEEE Нет. 28 сессия Программируемые пользовательские компьютеры (FCCM) Международный симпозиум, Фейетвилл, АР, США, 2020 г. Год,Нет. 38-46 Страница, doi:10.1109/FCCM48280.2020.00015.

[8] AMD,«Пример Vitis Accel»,https://github.com/Xilinx/Vitis Accel Examples/blob/main/cpp kernels/systolic array/src/mmult.cpp, время доступа: 2023 г. Год 10 луна 12 день.

[9] Hyunok Kim,“onic-driver”,https://github.com/Hyunok-Kim/onic-driver,Время доступа: 01.11.2023.

[10] AMD,“qep-driver”,https://github.com/Xilinx/qep-drivers,доступвремя:2023 Год 11 луна 1 день.

[11] AMD,“libqdma”,https://github.com/Xilinx/dma ip драйверы/дерево/мастер/QDMA/linux-kernel/driver/libqdma, обращение: 2023 г. Год 11 луна 1 день.

[12] AMD,“Vitis Networking P4”,https://www.xilinx.com/products/intellectual-property/ef-di-vitisnetp4.html,доступвремя:2023 Год 11 луна 1 день.

[13] AMD,“AlveoLink”,https://github.com/Xilinx/AlveoLink,доступвремя:2023 Год 11 луна 1 день.

[14] AMD,«На примере сети XUP Витис»,https://github.com/Xilinx/xup vitis Пример сети, доступ: 2023 г. Год 11 луна 1 день.

[15] V. Krishnan、O. Serres и M. Blocksome, «Настраиваемый ускоритель сетевых протоколов» (COPA): Интеграция сетевого/ускорительного оборудования/мягкого программного обеспечения», 2020 г. Год IEEE Семинар по высокопроизводительному межсетевому соединению (HOTI), Пискатауэй, Нью-Джерси, США ,2020 Год,Нет. 17-24 Страница, doi:10.1109/HOTI51249.2020.00018.

[16] Z. Wang、H. Huang、J. Zhang、F. Wu и G. Алонсо, «FpgaNIC: для GPU изна основе FPGA из Многофункциональный 100Gb SmartNIC”,2022 Год USENIX Год Степень Техническая конференция (USENIX УВД), Карлсбад, Калифорния ,2022 Год,Нет. 967-986 Пейдж, isbn: 978-1-939133-29-25

[17] D. Korolija、T. Roscoe и G. Алонсо «Абстракция операционной системы в FPGA Имеет ли начальство смысл? ", Нет. 14 сессия USENIX Семинар по проектированию и внедрению операционных систем (OSDI 20),2020 Год,Нет. 991-1010 страница, isbn: 978-1-939133-19-9

Сяобин (ssbandjl)

блог: https://cloud.tencent.com/developer/user/5060293/articles | https://logread.cn | https://blog.csdn.net/ssbandjl | https://www.zhihu.com/people/ssbandjl/posts

столбец ДПУ

https://cloud.tencent.com/developer/column/101987

Технические друзья: Добро пожаловатьверноDPU/SmartNIC/Удалить/сеть,ускорение хранения данных/Интересуются такими технологиями, как изоляция безопасностииз Друзья присоединяйтесьТехнология ДПУКоммуникационная группа

Углубленный анализ переполнения памяти CUDA: OutOfMemoryError: CUDA не хватает памяти. Попыталась выделить 3,21 Ги Б (GPU 0; всего 8,00 Ги Б).

[Решено] ошибка установки conda. Среда решения: не удалось выполнить первоначальное зависание. Повторная попытка с помощью файла (графическое руководство).

Прочитайте нейросетевую модель Трансформера в одной статье

.ART Теплые зимние предложения уже открыты

Сравнительная таблица описания кодов ошибок Amap

Уведомление о последних правилах Points Mall в декабре 2022 года.

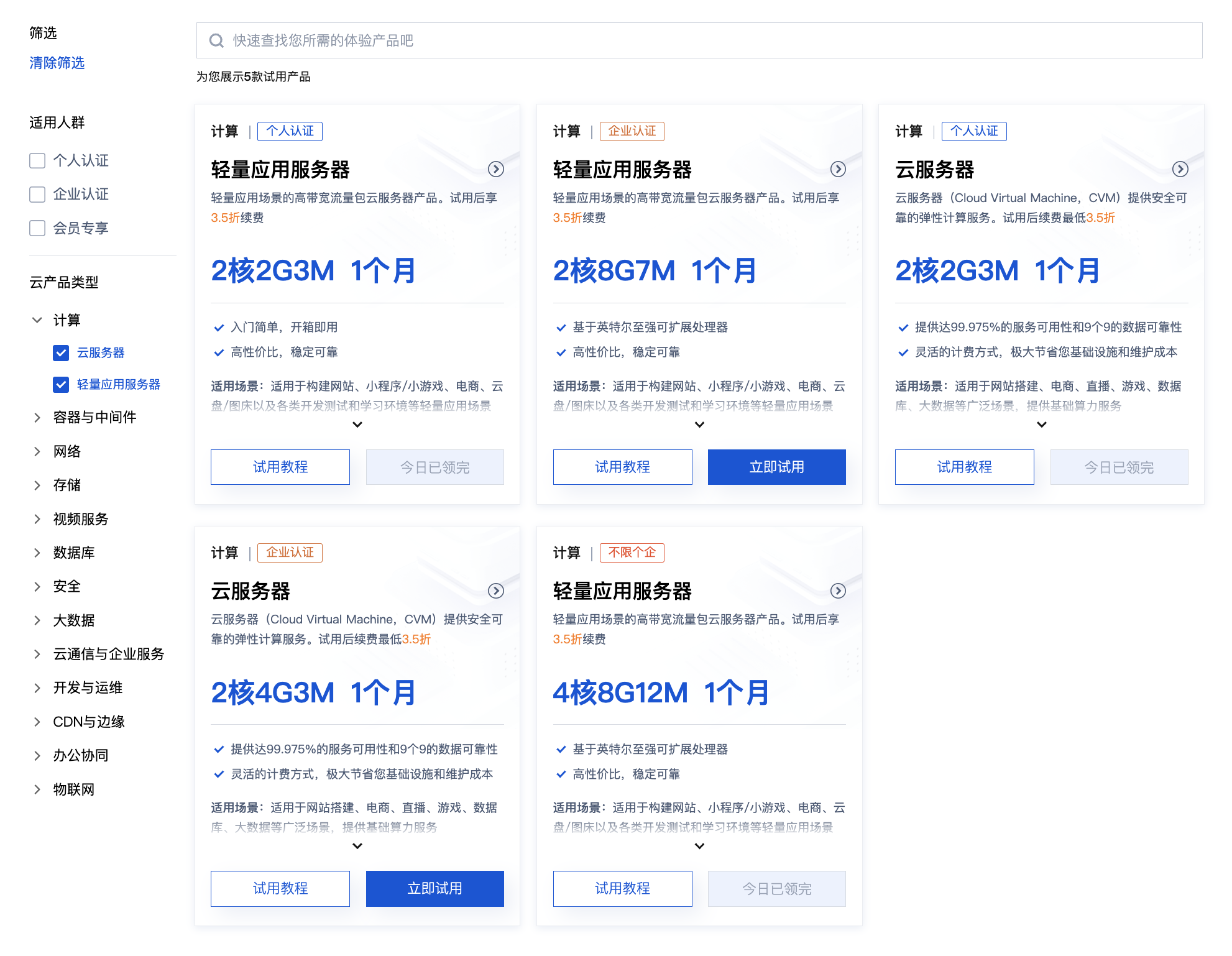

Даже новички могут быстро приступить к работе с легким сервером приложений.

Взгляд на RSAC 2024|Защита конфиденциальности в эпоху больших моделей

Вы используете ИИ каждый день и до сих пор не знаете, как ИИ дает обратную связь? Одна статья для понимания реализации в коде Python общих функций потерь генеративных моделей + анализ принципов расчета.

Используйте (внутренний) почтовый ящик для образовательных учреждений, чтобы использовать Microsoft Family Bucket (1T дискового пространства на одном диске и версию Office 365 для образовательных учреждений)

Руководство по началу работы с оперативным проектом (7) Практическое сочетание оперативного письма — оперативного письма на основе интеллектуальной системы вопросов и ответов службы поддержки клиентов

[docker] Версия сервера «Чтение 3» — создайте свою собственную программу чтения веб-текста

Обзор Cloud-init и этапы создания в рамках PVE

Корпоративные пользователи используют пакет регистрационных ресурсов для регистрации ICP для веб-сайта и активации оплаты WeChat H5 (с кодом платежного узла версии API V3)

Подробное объяснение таких показателей производительности с высоким уровнем параллелизма, как QPS, TPS, RT и пропускная способность.

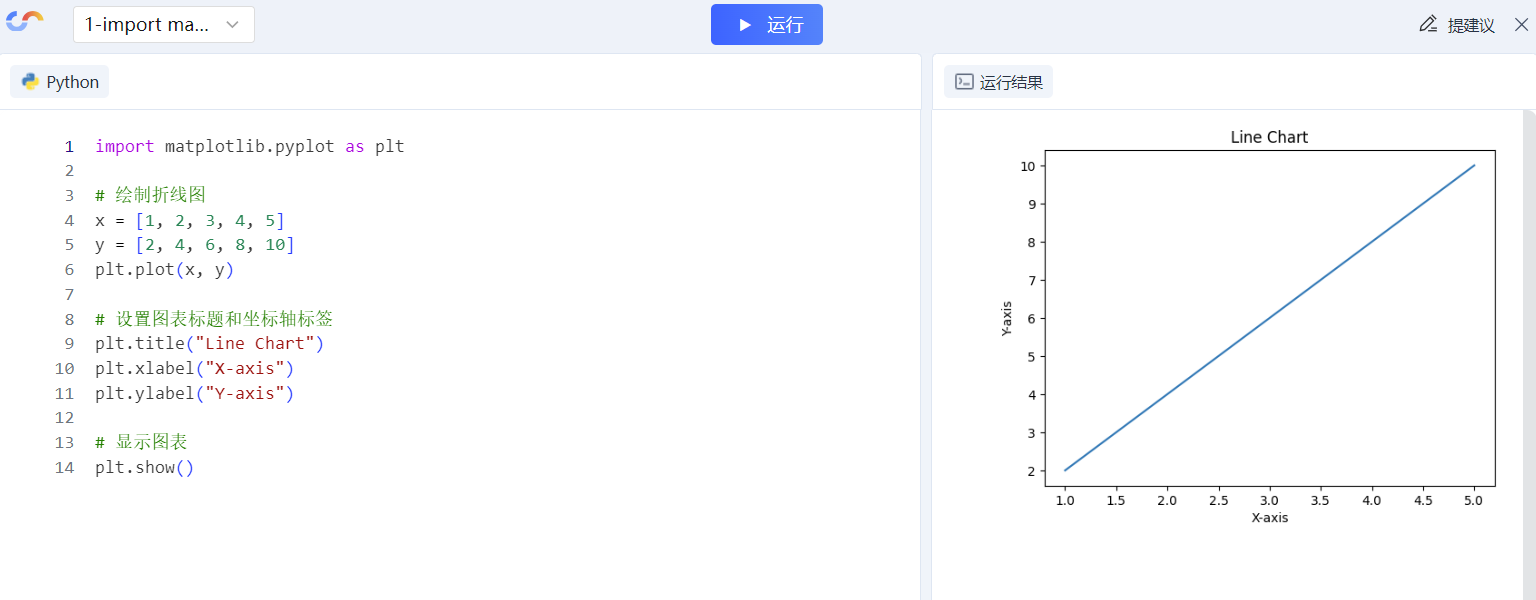

Удачи в конкурсе Python Essay Challenge, станьте первым, кто испытает новую функцию сообщества [Запускать блоки кода онлайн] и выиграйте множество изысканных подарков!

[Техническая посадка травы] Кровавая рвота и отделка позволяют вам необычным образом ощипывать гусиные перья! Не распространяйте информацию! ! !

[Официальное ограниченное по времени мероприятие] Сейчас ноябрь, напишите и получите приз

Прочтите это в одной статье: Учебник для няни по созданию сервера Huanshou Parlu на базе CVM-сервера.

Cloud Native | Что такое CRD (настраиваемые определения ресурсов) в K8s?

Как использовать Cloudflare CDN для настройки узла (CF самостоятельно выбирает IP) Гонконг, Китай/Азия узел/сводка и рекомендации внутреннего высокоскоростного IP-сегмента

Дополнительные правила вознаграждения амбассадоров акции в марте 2023 г.

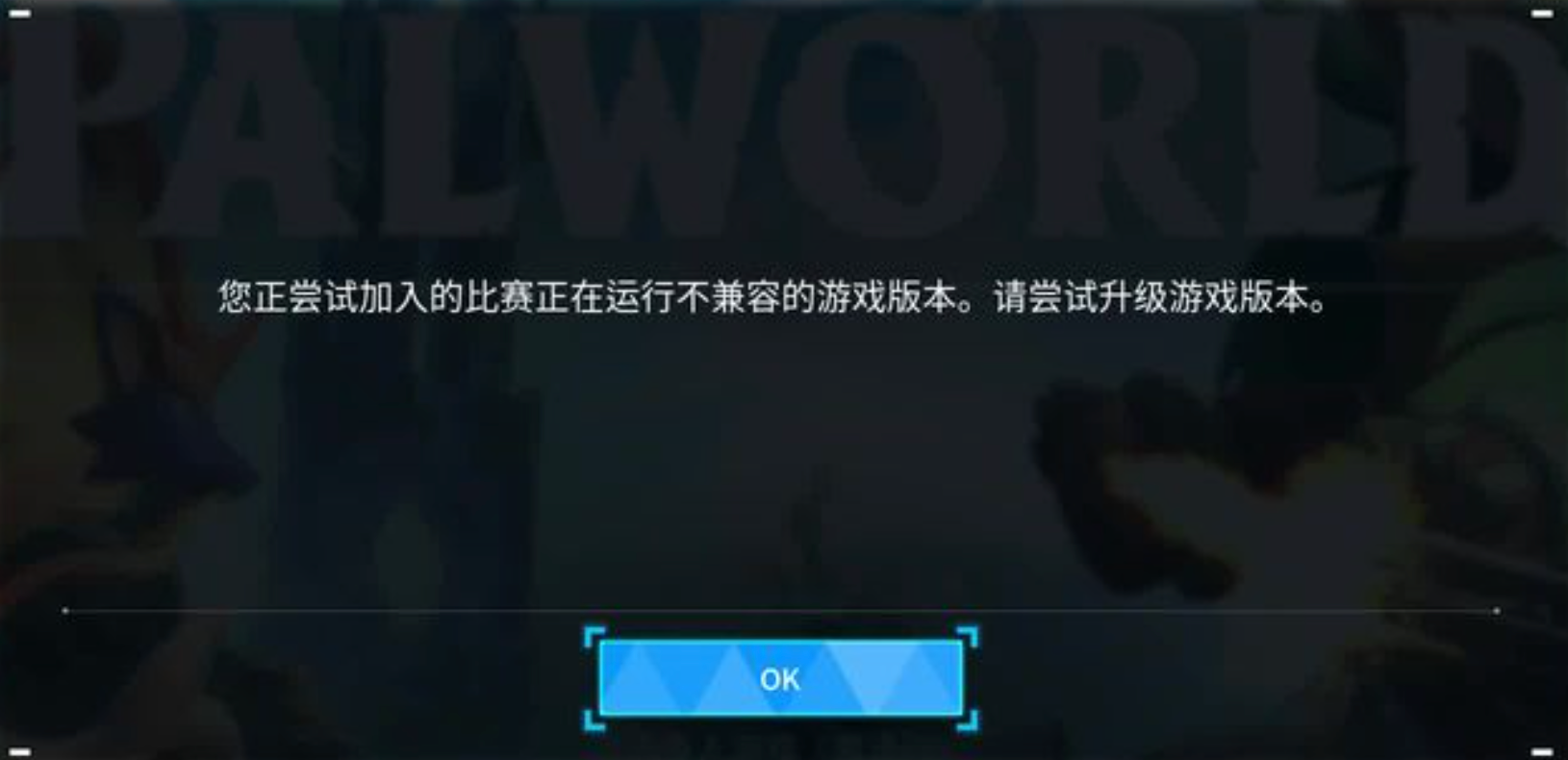

Можно ли открыть частный сервер Phantom Beast Palu одним щелчком мыши? Супер простой урок для начинающих! (Прилагается метод обновления сервера)

[Играйте с Phantom Beast Palu] Обновите игровой сервер Phantom Beast Pallu одним щелчком мыши

Maotouhu делится: последний доступный внутри страны адрес склада исходного образа Docker 2024 года (обновлено 1 декабря)

Кодирование Base64 в MultipartFile

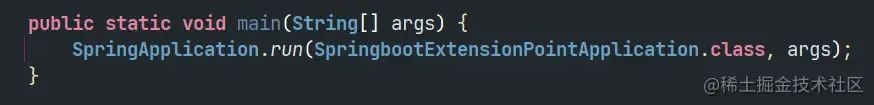

5 точек расширения SpringBoot, супер практично!

Глубокое понимание сопоставления индексов Elasticsearch.