Начало работы с операциями Quartus II [просто для понимания]

Использование Quartus для проектирования FPGA просто включает в себя следующий процесс:

- Новое строительство,написать код

- Скомпилировать проект,Найти ошибки

- Назначить контакты,Перекомпилировать

- Скачать конфигурацию,к оборудованию

Чтобы гарантировать правильность проекта, после компиляции обычно требуется проверка моделирования, а затем его загрузка в оборудование. Существует два метода моделирования: – Функциональное моделирование – Моделирование времени

Создайте новый проект и напишите код

–Создать папку проекта Создайте новую папку на своем компьютере, например E:\Lianxi_1. Все файлы проекта будут храниться в этой папке для удобства управления. Один проект соответствует одной папке. –Новое строительство Открыть Квартус II,File->New Project Мастер... как показано ниже: Сначала выберите рабочий каталог: выберите только что созданную пустую папку. Второй — заполнить название проекта. Оно должно быть осмысленным. Например, если вы хотите создать 38-битный декодер, имя проекта должно называться decoder3_8. Не используйте китайский язык. Третий — это имя объекта проектирования верхнего уровня, которое используется по умолчанию.

↓ Далее... Как показано ниже, добавьте существующий файл исходного кода. Если нет, нажмите «Далее».

↓ На рисунке ниже выберите модель FPGA в соответствии с номером модели, напечатанным на вашем чипе FPGA. Например, модель чипа, которую я использую, выглядит следующим образом: Семейство: Циклон II Устройство: EP2C5T144C8

↓ Далее... Как показано ниже, выберите инструменты синтеза, моделирования и временного анализа. Если вы выберете здесь «Нет», это означает использование инструментов, поставляемых с Quartus. Примечание: Четвертый Версии после 9.1 больше не поставляются со встроенными инструментами моделирования, и для моделирования необходимо установить такое программное обеспечение, как Modelsim.

↓ Далее.. На рисунке ниже представлен обзор ранее заданной информации. Если все верно, нажмите «Готово».

- написать код

↑ Создайте новый файл VerilogHDL, напишите код,при сохранении,Имя файла должно соответствовать имени объекта, определенному в модуле.。Прямо сейчас,Сохраните decoder3_8.v в папку вашего проекта.

module decoder3_8 (data_out, data_in ) ;

input [2:0] data_in;

output [7:0] data_out;

reg [7:0] data_out;

always @(data_in)

begin

case (data_in )

3'b000: data_out=8'b11111110;

3'b001: data_out=8'b11111101;

3'b010: data_out=8'b11111011;

3'b011: data_out=8'b11110111;

3'b100: data_out=8'b11101111;

3'b101: data_out=8'b11011111;

3'b110: data_out=8'b10111111;

3'b111: data_out=8'b01111111;

default: data_out=8'bxxxxxxxx;

endcase

end

endmoduleСохранить как decoder3_8.v Установите этот исходный файл в качестве файла верхнего уровня, как показано ниже: В Навигаторе проекта в окне навигации → нажмите «Файлы». Щелкните правой кнопкой мыши файл decoder3_8.v. Установить объект верхнего уровня

Затем щелкните Иерархию архитектуры проекта, чтобы проверить, является ли архитектура верхнего уровня текущим файлом верхнего уровня. Примечание. В проекте может быть несколько файлов исходного кода. Но только один из них является файлом верхнего уровня, представляющим проект верхнего уровня, который может ссылаться на другие исходные файлы в каталоге проекта.

Скомпилируйте проект и найдите ошибки

компилировать:Processing–>Start Compilation Если компиляция не удалась, ниже появится красное сообщение. Внимательно проверьте синтаксис. Дважды щелкните красное сообщение, чтобы сразу найти место рядом с кодом ошибки. После внесения изменений перекомпилируйте, пока все ошибки не будут исправлены. Компиляция прошла успешно, но синтаксис правильный, но это не значит, что дизайн полностью правильный. Мы можем использовать моделирование, чтобы проверить, соответствует ли конструкция ожидаемой функциональности.

Назначьте контакты, перекомпилируйте

После того, как предыдущий проект будет завершен, начните назначать контакты. Примечание. FPGA имеет множество контактов, и большинство из них можно произвольно назначить входными или выходными. В этом проекте мы можем назначить вход и выход любому назначаемому контакту. Конечно, для завершенной версии аппаратной разработки некоторые кнопки, индикаторы дисплея и т. д. были заранее подключены к ПЛИС, поэтому Назначить контактызависит от оборудованияПринципиальная схемаправильный Назначить контакты。 Назначение вывода: Назначение -> Pin Planner,Как показано на рисунке. После назначения контактов,закрыть окно,Перекомпилироватьпроект。

Загрузите конфигурацию на оборудование

Есть много способов загрузки программ в FPGA. Обычно мы используем USB-Blaster.

–Подключить загрузчик • Подключите USB-разъем USB-Blaster к компьютеру и подключите 10-контактный разъем на другом конце к разъему JTAG на плате FPGA. • Используйте USB-кабель для питания платы FPGA. Если вы впервые используете загрузчик USB-Blaster на своем компьютере, вам необходимо установить для него драйвер: метод:Щелкните правой кнопкой мыши на моем компьютере->Диспетчер устройств->USB-BlasterЩелкните правой кнопкой мыши->Обновить драйвер->найтиQuartusКаталог установкиC:\altera\9.0\quartus\drivers\usb-blaster,Подождите завершения установки. –скачать Меню Инструменты -> Программатор, картинка ниже

В левом верхнем углу нажмите «Оборудование». Setup…->раскрывающийся выборUSBBlaster->Close. Выберите метод загрузки в середине верхней части интерфейса, Режим: JTAG Слева нажмите Старт, чтобы загрузить .sof-файлы. Хорошо, давайте проверим, правильно ли работает оборудование.

Заявление об авторских правах: Содержание этой статьи добровольно предоставлено пользователями Интернета, а мнения, выраженные в этой статье, представляют собой только точку зрения автора. Этот сайт предоставляет только услуги по хранению информации, не имеет никаких прав собственности и не принимает на себя соответствующие юридические обязательства. Если вы обнаружите на этом сайте какое-либо подозрительное нарушение авторских прав/незаконный контент, отправьте электронное письмо, чтобы сообщить. После проверки этот сайт будет немедленно удален.

Издатель: Full stack программист и руководитель стека, укажите источник для перепечатки: https://javaforall.cn/181618.html Исходная ссылка: https://javaforall.cn

Порт запуска проекта Spring Boot часто занят, полное решение

Java вызывает стороннюю платформу для отправки мобильных текстовых сообщений

Практическое руководство по серверной части: как использовать Node.js для разработки интерфейса RESTful API (Node.js + Express + Sequelize + MySQL)

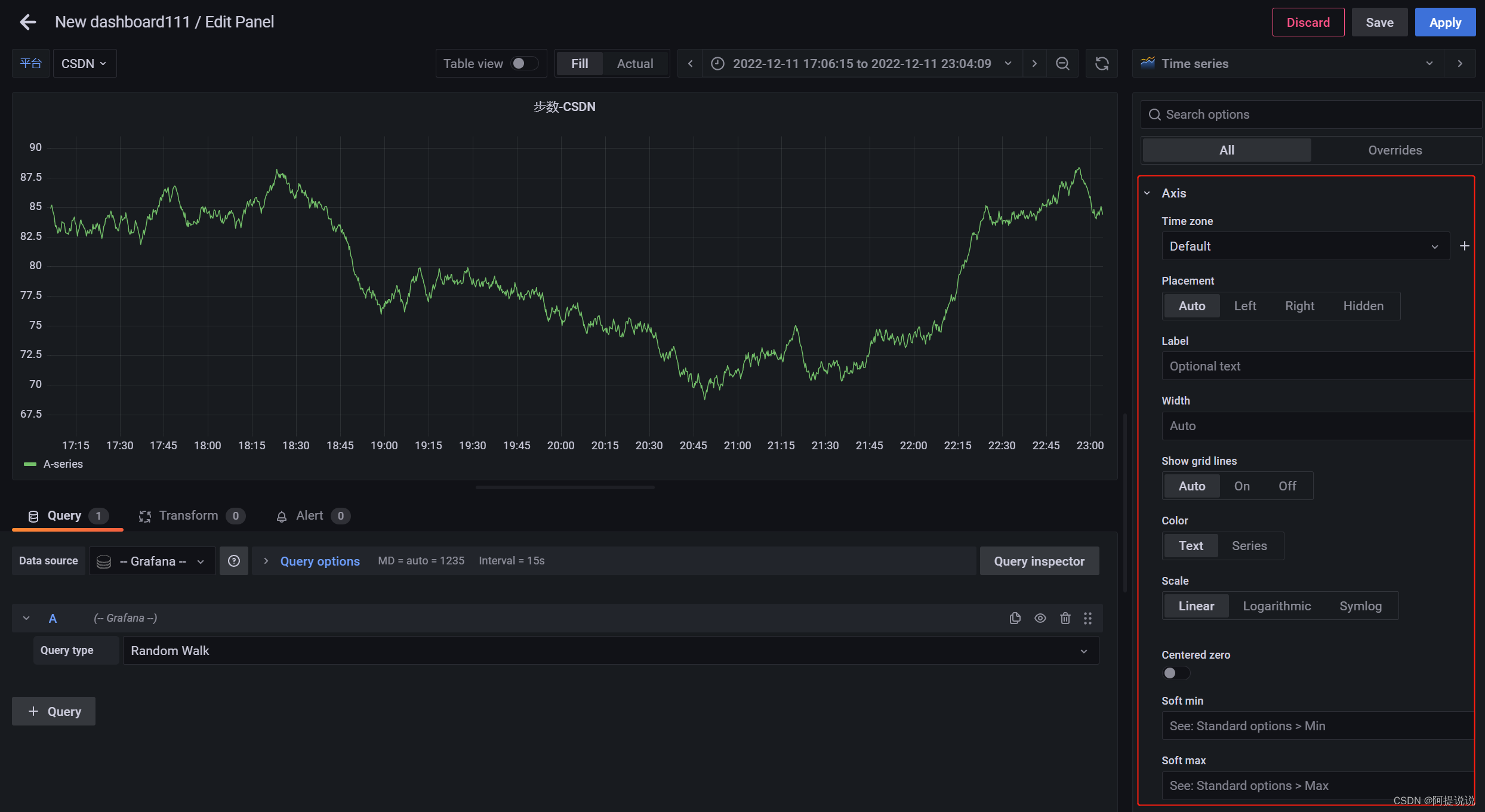

Введение в параметры конфигурации большого экрана мониторинга Grafana (2)

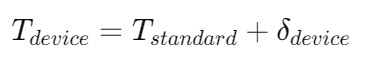

В статье «Научно-популярная статья» подробно объясняется протокол NTP: анализ точной синхронизации времени.

Пример разработки: серверная часть Java и интерфейсная часть vue реализуют функции комментариев и ответов.

Nodejs реализует сжатие и распаковку файлов/каталогов.

SpringBootИнтегрироватьEasyExcelСложно реализоватьExcelлистимпортировать&Функция экспорта

Настройка среды под Mac (используйте Brew для установки go и protoc)

Навыки разрешения конфликтов в Git

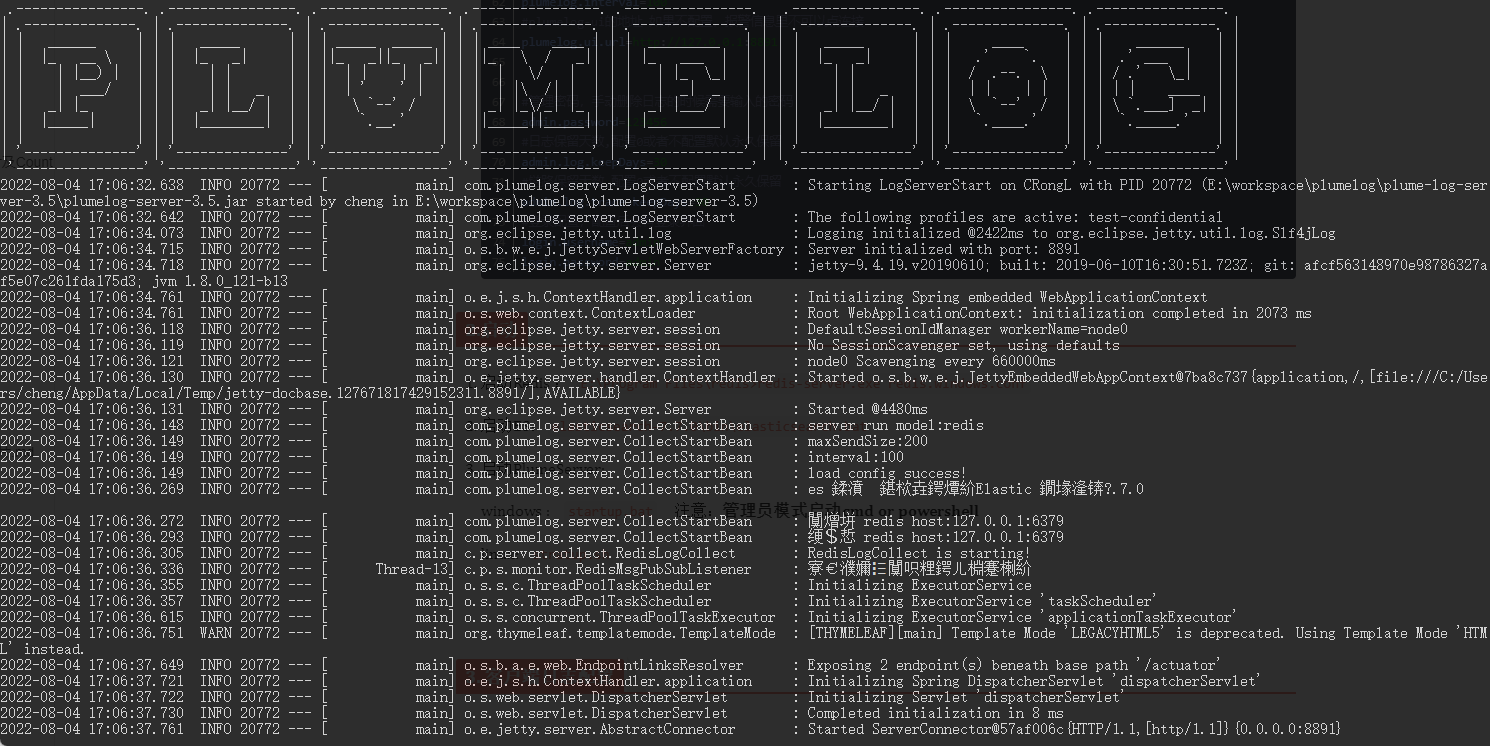

Распределенная система журналов: развертывание Plumelog и доступ к системе

Артефакт, который делает код элегантным и лаконичным: программирование на Java8 Stream

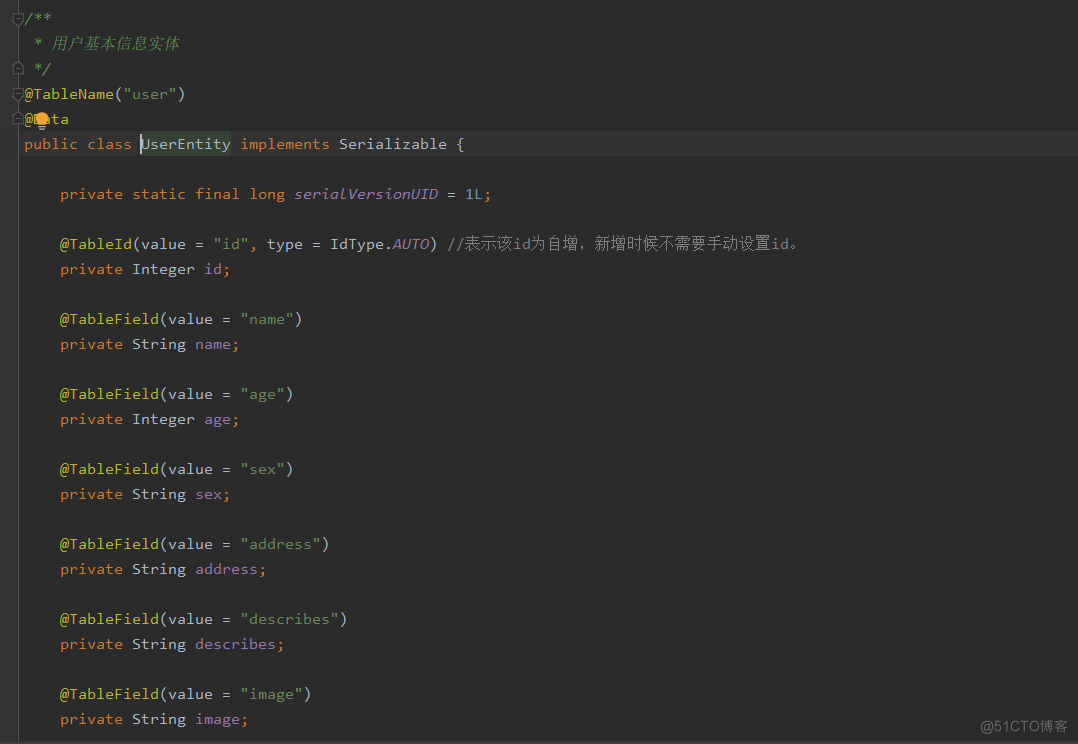

Spring Boot(06): Spring Boot в сочетании с MySQL создает минималистскую и эффективную систему управления данными.

Как использовать ArrayPool

Интегрируйте iText в Spring Boot для реализации замены контента на основе шаблонов PDF.

Redis реализует очередь задержки на основе zset

Получить текущий пакет jar. path_java получает файл jar.

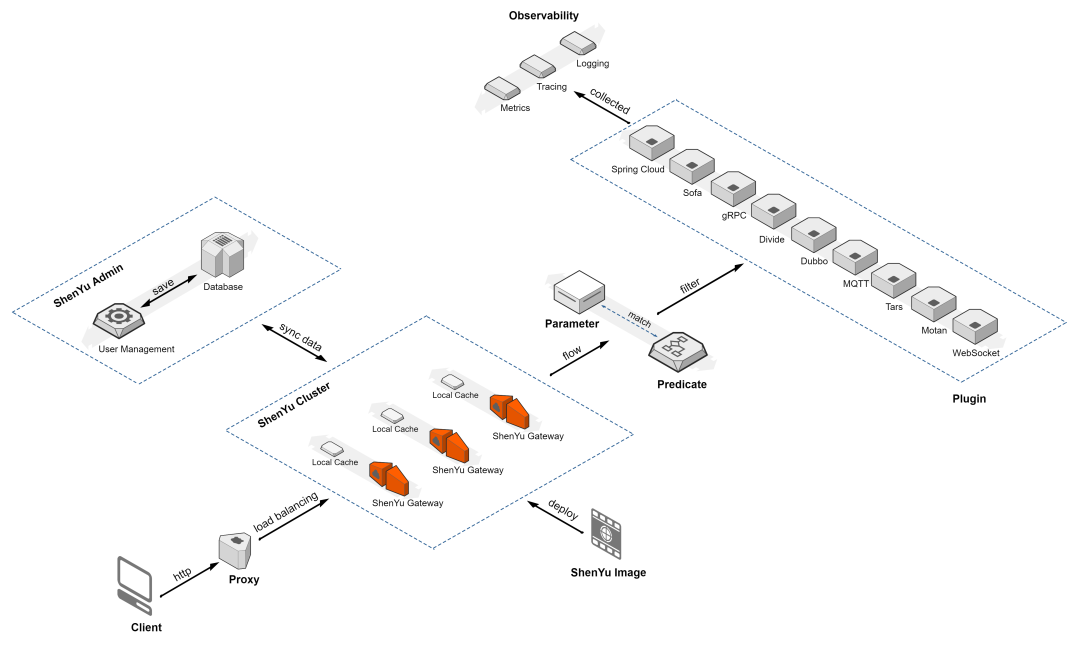

Краткое обсуждение высокопроизводительного шлюза Apache ShenYu

Если вы этого не понимаете, то на собеседовании даже не осмелитесь сказать, что знакомы с Redis.

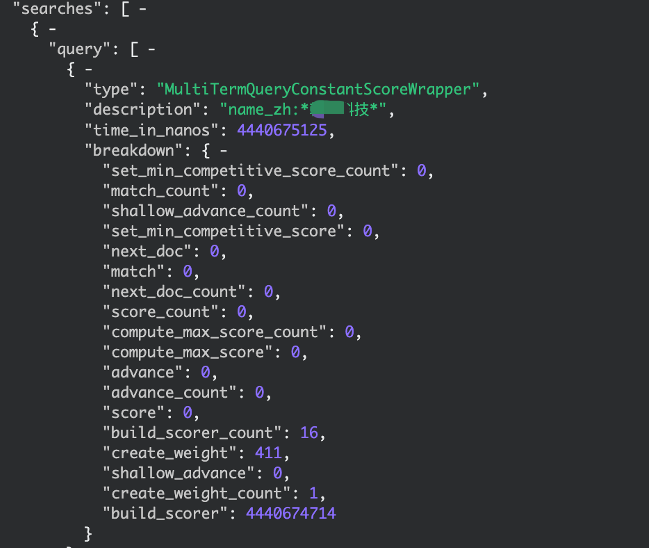

elasticsearch медленный запрос, устранение неполадок записи, запрос с подстановочными знаками

По какому стандарту взимается плата за обслуживание программного обеспечения?

IP-адрес Получить

【Java】Решено: org.springframework.web.HttpRequestMethodNotSupportedException

Native js отправляет запрос на публикацию_javascript отправляет запрос на публикацию

.net PDF в Word_pdf в Word

[Пул потоков] Как Springboot использует пул потоков

Подробное объяснение в одной статье: Как работают пулы потоков

Серия SpringCloud (6) | Поговорим о балансировке нагрузки

IDEA Maven может упаковать все импортное полностью красное решение — универсальное решение.