Можно ли вызвать явление фиксации во время испытаний на устойчивость к электростатическому разряду?

Давайте сначала поймем, что такое феномен фиксации. Прежде чем подробно остановиться на эффекте фиксации, давайте взглянем на концепцию фиксации.

Определение: В схеме CMOS,Есть паразитизмизтриодPNPN,Они влияют друг на друга вVDDиGNDсоздание пути с низким сопротивлением между,Создать большой ток,Вот что сгорает чипэффект фиксации (вместе сICРазмеры функций становятся все меньше и меньше,Интеграция становится все выше и выше,Эффект блокировки становится все более и более вероятным ;)

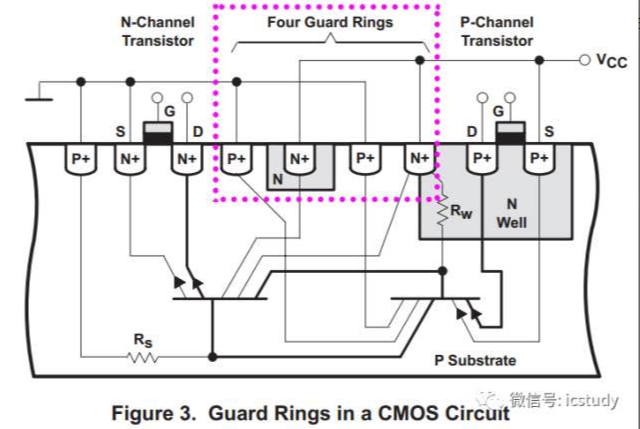

См. первое слово «паразитный транзистор» pnp npn из определения. Давайте посмотрим на их принципы работы, чтобы лучше понять защелку.

Функция транзистора: основная функция ламп контроля тока — усиление тока.

Открытые условия

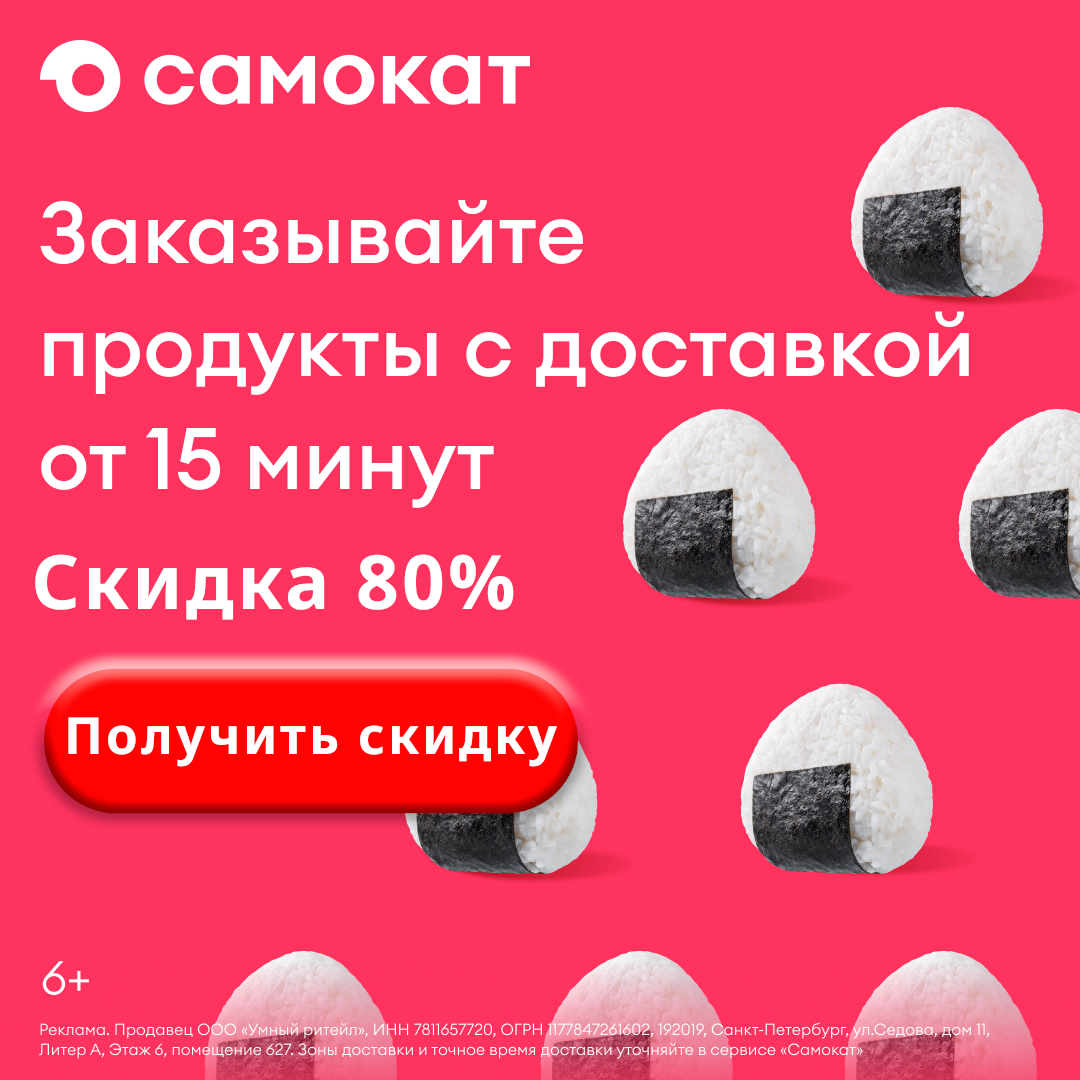

дляPNP-транзисторс точки зрения,Если вы хотите сделать PNP-транзистор токопроводящим,Такбазаиизлучатель(эмиссионный переход)Положительный уклон(Vbe=-0.7),То есть: потенциал базы(N) ниже потенциала эмиттера (P).,(Это прямое смещение эмиттерного перехода) Также необходимо, чтобы потенциал базы(N) был выше потенциала коллектора (P).,(Обратное смещение коллекторного перехода Vcb=-0,7. Классический метод подключения показан на рисунке).

дляNPN-транзисторс точки зрения,Если вы хотите сделать NPN-транзистор проводящим,Тогда база смещена в прямом направлении с эмиттером (эмиттерным переходом).,То есть: потенциал базы(P) выше потенциала эмиттера (N).,(Это прямое смещение эмиттерного перехода) Также необходимо, чтобы потенциал базы(P) был ниже потенциала коллектора (N).,(Коллекторный переход имеет обратное смещение). Классический метод подключения показан на рисунке.

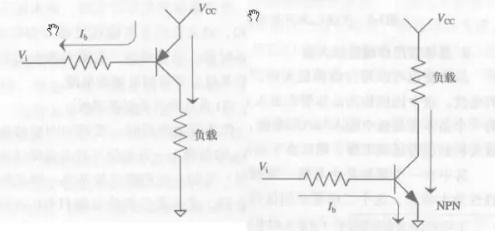

паразитная диаграмма

Q1 — вертикальный PNP BJT, База в порядке, базаколлекционеру(collector)из Получить доступный номерсто раз;

Q2 — односторонняя NPN БЮТ, основание — P substrate,коллекционеруиз Получить доступный номердесять раз;

Rwell — паразитное сопротивление nwell, его значение может достигать 20𝑘Ом; Rsub — сопротивление подложки, его значение колеблется от сотен до нескольких Ом;

QPNP и QNPN образуют структуру npnp для формирования схемы кремниевого выпрямителя (SCR).

В условиях сильного электрического поля, высокого напряжения или аномального тока эти паразитные структуры могут активироваться, вызывая феномен запирания.

Условие триггера

- Когда оба BJT включены, между VDD и GND создается путь с низким импедансом;

- Произведение коэффициентов усиления двух контуров обратной связи транзистора больше 1 (𝛽1×𝛽2≥1).

Когда никакое внешнее вмешательство не вызывает срабатывания,Два BJT находятся в состоянии отсечки.,ток коллекторадаC-Bизобеспечить регрессток утечкисоставляют,Текущий выигрыш очень мал,в это времяLatch upне будет производить。(Утечка определенно существует, это просто вопрос размера.)

когда один изBJTизток коллектораКогда внешнее вмешательство внезапно возрастает до определенного значения,В это время эмиттерный переход BJTиз смещен в прямом направлении.,Текущий отзыв о другом BJT,финальныйиз Причины петли обратной связииз Ток необходимо умножить на коэффициент усиления. 𝛽1×𝛽2 , это триггер SCR. В результате два BJT включаются за счет запуска, и между VDD и GND формируется низкоомный путь (VSS Latch). Из этого возникает вверх.

если( 𝛽1×𝛽2≥1 ) соблюдено, два BJT будут продолжать выдавать высокий ток насыщения даже без Условие триггераиз времени.

Резкое увеличение тока коллектора

существоватьэффект фиксации Явление (фиксации) коллектор паразитного PNP-транзистора будет нарушено внешними помехами и возникнет турбулентность. Коллектор Большой ток возникает, когда коэффициент усиления достигает определенного значения。

При высоких температурах из-за повышенной утечки легко сработать паразитный кремниевый управляемый выпрямитель (Silicon Controlled Выпрямитель, SCR) начинает генерировать LU Эффект, поэтому вы можете выбрать нормальную температуру или высокую температуру (в зависимости от максимальной рабочей температуры или Tj технических характеристик продукта). Зависит от температуры)Два видатестсреда,AEC Нормыдапринудительная высокая температуратест

Когда внешнее возмущение (например, электрическое поле, электростатический разряд и т.п.) воздействует на транзистор избаза,вызывая увеличение напряжения между базой и эмиттером,паразитическийPNPтранзисторизэмиссионный переход Воля Положительный уклон。Это приводит кЭмиттерная область инжектирует большое количество дырок в базовую область.,Эти отверстия будут диффундировать в область коллектора.,собран коллекционером,Таким образом образуется больший изток коллектора.потому чтоPNPтранзисторизбазав целомдаNловушка,Коллектор представляет собой подложку П-типа.,Когда напряжение между лункой N и подложкой P достаточно велико,Это запустит описанный выше процесс.

Когда чип начинает работать, VDD изменяется, вызывая nwell и P substrateмеждуПаразитная емкость (емкость PN-перехода)производить достаточноизтекущий,Когда скорость изменения VDD достигает определенного уровня,Вызовет блокировку.

• Когда сигнал ввода-вывода выходит за пределы диапазона VDD-GND (VSS), в микросхеме генерируется большой ток, который также запускает тиристор.

• Электростатическое напряжение ESD может привести к попаданию небольшого количества носителей заряда из схемы защиты в лунку или подложку, что также может вызвать срабатывание SCR.

• Когда одновременно работает много драйверов, нагрузка слишком велика, мощность и земля внезапно меняются, и можно открыть биполярный транзистор тиристора.

• Хорошо. Боковой ток утечки слишком велик.

Предотвратить метод фиксации

Допинг

Используйте тяжелый субстрат для допинга.,Уменьшить значение Rsub,Уменьшите усиление контура обратной связи.

Используйте легкий эпитаксиальный слой допинга для предотвращения бокового тока. утечкис портретаPNPк подложке с низким сопротивлениемизряд。

дизайн макета

- Просверлите больше контактных отверстий и держите их как можно ближе к активной зоне (уменьшите Rwell, Rsub).

- Использовать охрану кольца (с одной стороны снижает Rwell и Rsub, с другой стороны не дает носителям добраться до BJTбазы)

- NMOS расположен близко к GND, PMOS — близко к VDD и хранится на достаточном расстоянии, чтобы уменьшить вероятность срабатывания SCR.

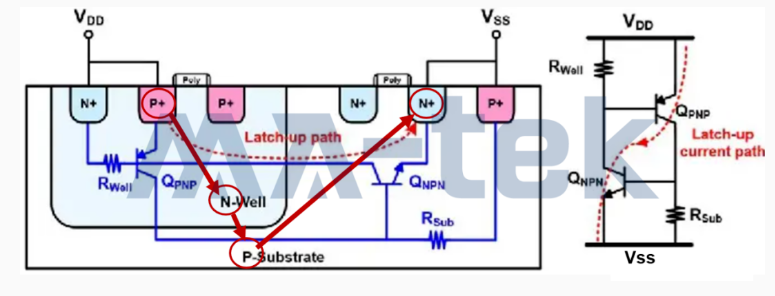

Использование Guardring:

1. Multi-sub GuardRing: кольцо P+ окружает NMOS и подключено к GND; кольцо N+ подключено к PMOS и подключено к VDD; Использование защитного кольца с несколькими несущими может снизить сопротивление Rwell и Rsub и предотвратить попадание основных несущих в базу.

2. Minority GuardRing: Кольцо N+, выполненное в N-лунке, окружает NMOS и подключено к VDD. Кольцо P+ окружает PMOS и подключено к GND; Использование защитных колец неосновных носителей может уменьшить защелкивание, вызванное введением неосновных носителей в лунку или субстрат.

Предотвратите прямое смещение перехода EB паразитного транзистора и предотвратите генерацию начального тока.Например, входное напряжение превышаетVCC,Положительное отклонение узла EB может вызвать фиксацию.

Уменьшите усиление петли положительной обратной связи.уменьшатьпаразитическийтранзисторизувеличение иRw/RsСопротивление может эффективно уменьшить коэффициент усиления контура.。

Распространенный метод, указанный здесь, — установка защитного кольца. Существует два типа защитных колец:

Несколько колец дополнительной защиты могут снизить Rw/R,

Кольцо защиты неосновных несущих может собирать неосновные несущие и уменьшать коэффициент усиления β паразитного транзистора.

Пример соединительной схемы Vbe

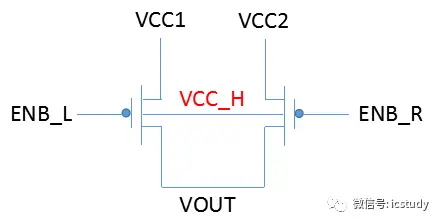

Мы знаем этих двоихPMOSсуществоватьCMOSВ процесседануждатьсяНезависимый N Wellиз,

И потенциал этой N Well должен быть выше, чем истока и стока (Drain/Source) PMOS, чтобы предотвратить включение PN-перехода.

Тогда давай сделаем это сейчас N Well Выберите напряжение (в целях экономии площади эти два PMOS будут размещены на одном и том же месте). N Well середина), Поскольку иногда VCC1 больше, чем VCC2, иногда VCC1 меньше, чем VCC2, поэтому N Well Вы не можете использовать VCC1 или VCC2, но Нужно подключитьСамый высокий потенциал VCC_H。

Когда схема переключается из рабочего режима в режим ожидания, VCC_H обычно разряжается. Если на VCC1, VCC2 или VOUT имеется большая емкость, VCC_H может быть ниже, чем VCC1, VCC2 или VOUT при разряде, что приводит к проводимости PN-перехода. Говоря о защелке выше, мы уже знаем, что VCC1, VCC2 и VOUT можно рассматривать как эмиттеры (E) паразитного PNP-транзистора, а VCC_H можно рассматривать как базу (B) паразитного PNP-транзистора. Проводимость PN-перехода эквивалентна прямому смещению EB-перехода, что может вызвать защелкивание и повреждение схемы.

Столкнувшись с потенциальными рисками блокировки, помимо сокращения времени существования неосновных носителей за счет легирования золотом и других методов в процессе, мы также можем использовать методы схемы и компоновки для решения проблемы, основанные на принципе блокировки.

(1) В процессе проектирования схемы мы можем замедлить скорость разряда VCC_H, чтобы VCC_H всегда был выше, чем другие потенциалы. Вы также можете увеличить путь выпуска VCC1, VCC2 и VOUT, чтобы сток/источник PMOS предшествовал выпуску скважины. Основная идея состоит в том, чтобы предотвратить включение PN-перехода (EB-переход смещен в прямом направлении).

(2) В процессе реализации компоновки мы можем уменьшить коэффициент усиления паразитного транзистора путем добавления защитных колец с несколькими несущими (уменьшить Rs/Rw) и защитных колец неосновных несущих (уменьшить коэффициент усиления паразитного биполярного транзистора). Вы также можете держать этот N Well подальше от других цепей, чтобы снизить риск блокировки.

Использование схемных методов для решения защелки требует дополнительных схем управления, а методы компоновки увеличивают площадь компоновки (часто эти PMOS имеют очень большие размеры, а дополнительная площадь компоновки — это деньги). Что касается того, какой метод использовать или оба, это зависит от реальной ситуации в проекте.

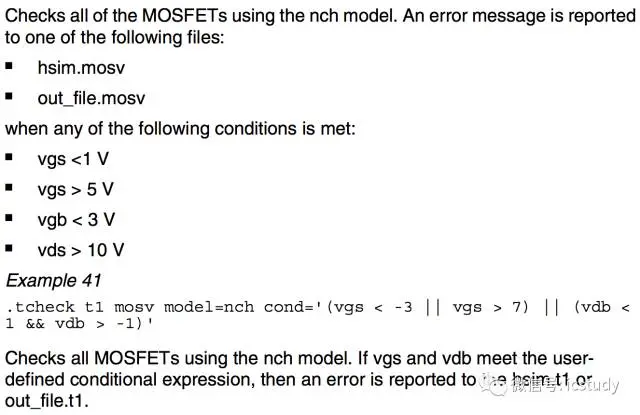

Наконец, позвольте мне поделиться очень практичным методом проверки:

Как правило, мы потратили много усилий на выбор потенциала каждой скважины во время проектирования схемы. Однако, чтобы предотвратить ошибки, нам все равно нужно сосредоточиться на проверке того, является ли PN-переход проводящим на этапе проверки моделирования. Некоторые инструменты моделирования схем, такие как HSIM, могут отслеживать относительную взаимосвязь между напряжениями на каждом выводе MOS. Пока схема на рисунке выше добавлена в испытательный стенд для проверки того, превышают ли Vsb и Vdb PMOS прямое напряжение PN-перехода, можно проверить модули схемы с риском защелкивания.

Методы ESD-тестирования

Предположим, что чип имеет AGND1, AGND2, DGND, AVCC1, AVCC2, DVCC и общий ввод-вывод. Здесь, на примере ALL до AGND1 (+), описание выглядит следующим образом:

первый шагвсемизpinСначала измерьте этоIV характеристика:

Все источники питания и заземление (включая AGND1, AGND2, DGND, AVCC1, AVCC2, DVCC) подключены к «земле», добавляют прямое и обратное напряжения к общему входу-выходу и измеряют ток (обычно сила I по умолчанию для машины MK2, измерение В). если вы хотите принудительно указать величину V, я должен быть особо упомянут). Если он подключен к определенному источнику питания или «земле», то все остальные источники питания и GND подключаются к «земле», а затем в прямом и обратном направлении. напряжения добавляются к источнику питания или GND для измерения тока;

Шаг 2Правильно, кромеAGND1 За исключением контактов, подайте положительные импульсы ESD на все контакты;

Шаг 3Слишком много борьбыESDпульсиз Чипировать всеpinИзмерьте еще разIVхарактеристика,

Метод должен быть таким же, как и на первом этапе (нужно ли также отдельно измерять AGND1 для ВАХ? В настоящее время ВАХ AGND1 не будет измеряться, поскольку это не вывод Zap, если только ВАХ не измеряются отдельно). после завершения всего измерения. Об этой необходимости также необходимо указать отдельно);

Шаг 4даконтраст

Для ВАХ, измеренных на первом и третьем этапах, если разница между ВАХ определенного штыря превышает 30%, штырь считается отказом от электростатического разряда (здесь это означает, что ВАХ превышает стандарт оценки и также должен пройти через DC в соответствии с определением спецификации). Для принятия окончательного решения используются параметры и функциональные тесты. Большинство клиентов по-прежнему будут полагаться на IV FAIL для анализа и улучшения.

При проведении испытаний на устойчивость к электростатическому разряду может произойти защелкивание. феномен。Latch-upда Что-то вродеCMOSУникально для схемизпаразитическийэффект,Может привести к выходу из строя цепи,Или даже сжечь чип. Конкретное объяснение заключается в следующем:

- Взаимосвязь между ESD-тестированием и Latch-up

- Эффект электростатического разряда:ESDтест Путем моделирования электростатического разрядаизпроцесс,Подайте высокое напряжение на интегральную схему. Эти импульсы высокого напряжения могут проникнуть через внутреннюю защитную структуру чипа.,И спусковая защелка-феномен.

- Стандарты и методы испытаний:HBM(Human Body Модель) и CDM (за дополнительную плату) Device Model)да Два видаобщийизESDтест Модель。Эти Модель Используйте конкретныеизтестинструмент,Например, инструмент MK2test.,для моделирования и применения напряжения высокого давления.

- Анализ результатов испытаний:ESDтест Отчеты часто включаютpre-stressиpost-stressизI-Vизгиб。еслитестназадизгибитестпрежде чем разница превысит30%,будет считаться недействительным. Этот сбой может быть вызван фиксацией.

- Метод тестирования с защелкой

- Текущий тест:В основном включают положительные Текущий (ток стока) и отрицательный Текущий (протянуть электрический ток). Эти тесты определяют, генерируется ли аномальный ток при подаче высокого напряжения на вход/выход.

- испытание напряжением:основнойда Перенапряжение на выводах питаниятест,Наблюдайте за работой чипа при максимальном рабочем напряжении.

- Настройка температуры окружающей среды:нормальная температура или высокая температурасредапродолжить дальшетест,Потому что высокие температуры чаще вызывают защелки-феномен.

- Риск триггера блокировки при тестировании ESD

- проникновение высокого напряжения:ESDтестсредний прикладнойиз Высокое напряжение может проникнуть через защитные конструкции,Непосредственно активируйте паразитическую структуру, необходимую для фиксации.

- Аномальные колебания тока:тестпроцесссерединатекущийиз Быстрые изменения также могут активироватьпаразитическийтриод,Подведите к защелке-феномен.

- Оборудование и факторы окружающей среды:тестоборудованиеизточностьитестсредаиз Стабильность также повлияетlatch-upизвероятность возникновения。

- Анализ случая и профилактические меры

- Реальные случаи:много интегральных схемсуществоватьESDтестпостоянный ущерб после,Большинство из них связано с непринятием эффективных мер защиты от блокировки.

- Оптимизация дизайна:существовать Что следует учитывать на этапе проектированияlatch-upзащита,Например, добавление защитных диодов, снижение паразитного сопротивления и другие меры.

- Корректировка плана тестирования:Разумное планированиетестплан,Постепенно увеличивайте испытательное напряжение.,В то же время отслеживайте текущие изменения, чтобы предотвратить возникновение зависаний.

Подводя итог, можно сказать, что испытание выдерживаемым напряжением электростатического разряда действительно несет в себе риск возникновения явления фиксации. Это происходит главным образом потому, что импульсы высокого напряжения могут активировать паразитные структуры, присущие КМОП-схемам, образуя пути с низким импедансом и вызывая продолжение протекания больших токов. Поэтому крайне важно принять соответствующие защитные меры на этапах проектирования и тестирования, чтобы обеспечить стабильность и надежность схемы.

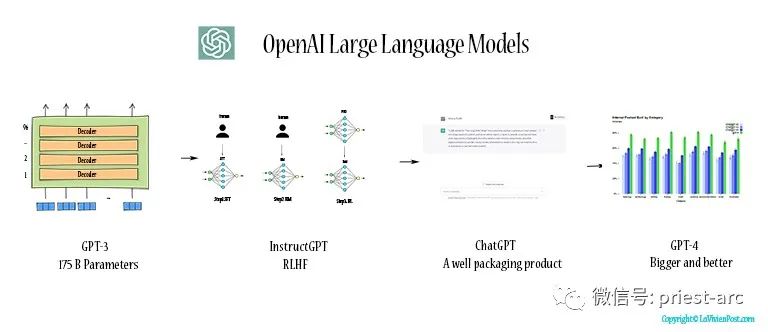

Углубленный анализ переполнения памяти CUDA: OutOfMemoryError: CUDA не хватает памяти. Попыталась выделить 3,21 Ги Б (GPU 0; всего 8,00 Ги Б).

[Решено] ошибка установки conda. Среда решения: не удалось выполнить первоначальное зависание. Повторная попытка с помощью файла (графическое руководство).

Прочитайте нейросетевую модель Трансформера в одной статье

.ART Теплые зимние предложения уже открыты

Сравнительная таблица описания кодов ошибок Amap

Уведомление о последних правилах Points Mall в декабре 2022 года.

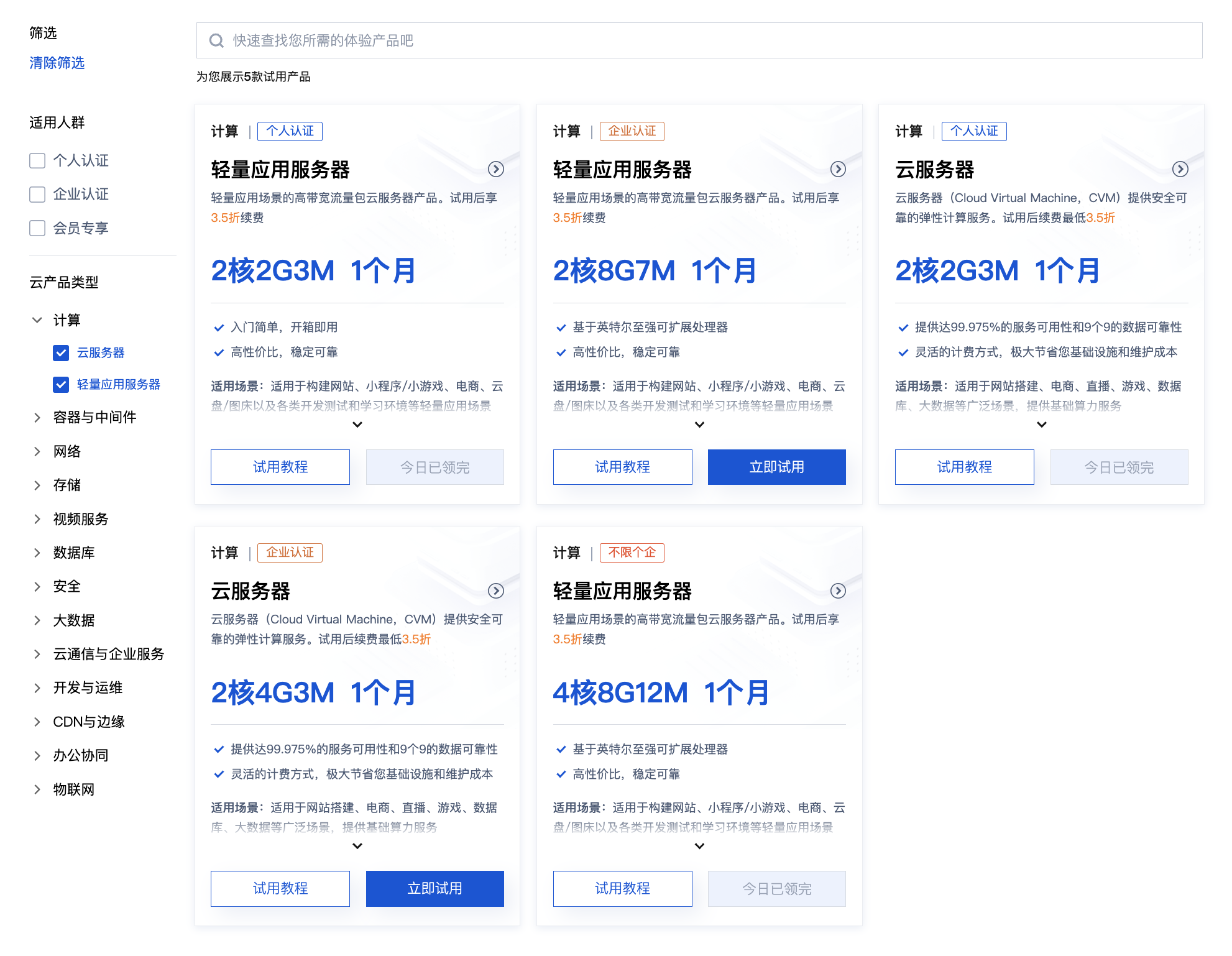

Даже новички могут быстро приступить к работе с легким сервером приложений.

Взгляд на RSAC 2024|Защита конфиденциальности в эпоху больших моделей

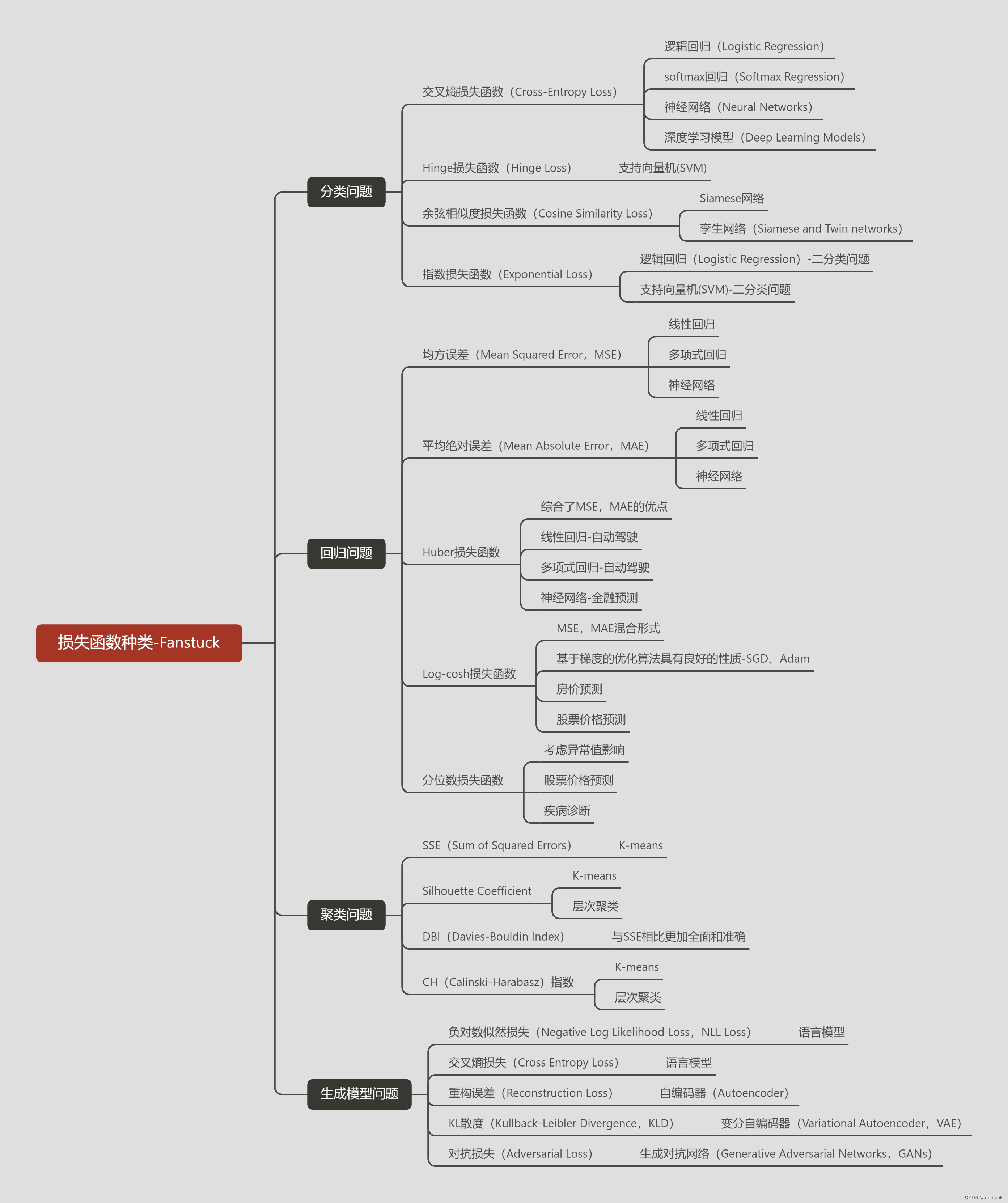

Вы используете ИИ каждый день и до сих пор не знаете, как ИИ дает обратную связь? Одна статья для понимания реализации в коде Python общих функций потерь генеративных моделей + анализ принципов расчета.

Используйте (внутренний) почтовый ящик для образовательных учреждений, чтобы использовать Microsoft Family Bucket (1T дискового пространства на одном диске и версию Office 365 для образовательных учреждений)

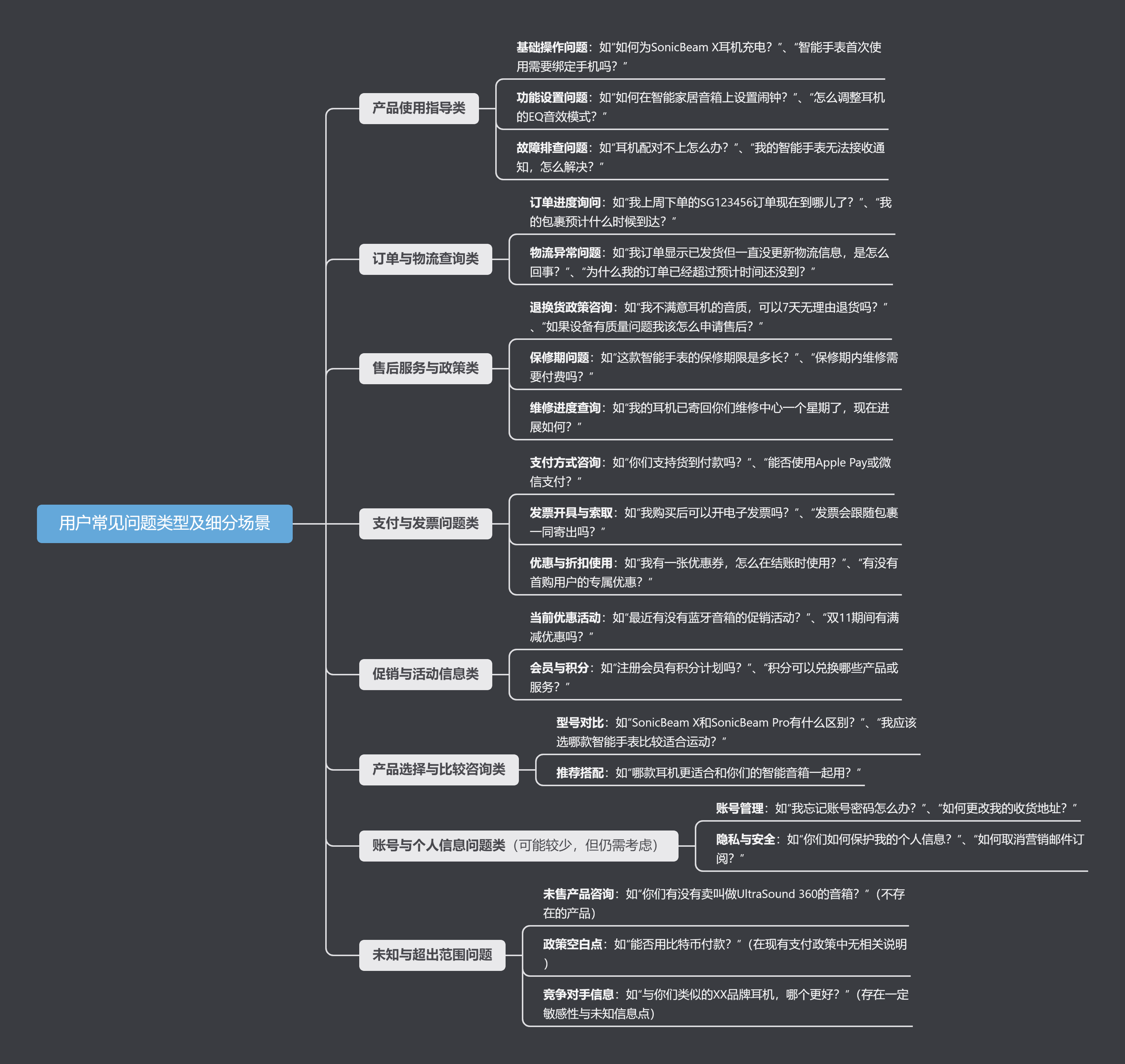

Руководство по началу работы с оперативным проектом (7) Практическое сочетание оперативного письма — оперативного письма на основе интеллектуальной системы вопросов и ответов службы поддержки клиентов

[docker] Версия сервера «Чтение 3» — создайте свою собственную программу чтения веб-текста

Обзор Cloud-init и этапы создания в рамках PVE

Корпоративные пользователи используют пакет регистрационных ресурсов для регистрации ICP для веб-сайта и активации оплаты WeChat H5 (с кодом платежного узла версии API V3)

Подробное объяснение таких показателей производительности с высоким уровнем параллелизма, как QPS, TPS, RT и пропускная способность.

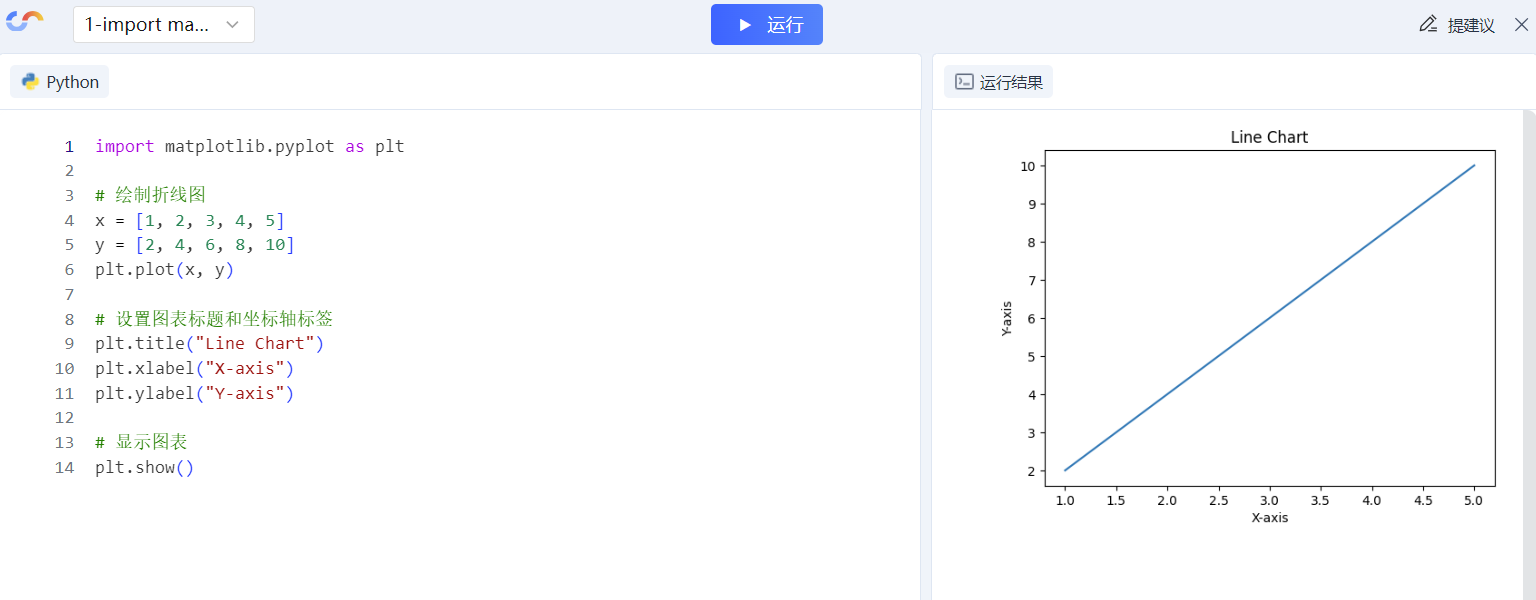

Удачи в конкурсе Python Essay Challenge, станьте первым, кто испытает новую функцию сообщества [Запускать блоки кода онлайн] и выиграйте множество изысканных подарков!

[Техническая посадка травы] Кровавая рвота и отделка позволяют вам необычным образом ощипывать гусиные перья! Не распространяйте информацию! ! !

[Официальное ограниченное по времени мероприятие] Сейчас ноябрь, напишите и получите приз

Прочтите это в одной статье: Учебник для няни по созданию сервера Huanshou Parlu на базе CVM-сервера.

Cloud Native | Что такое CRD (настраиваемые определения ресурсов) в K8s?

Как использовать Cloudflare CDN для настройки узла (CF самостоятельно выбирает IP) Гонконг, Китай/Азия узел/сводка и рекомендации внутреннего высокоскоростного IP-сегмента

Дополнительные правила вознаграждения амбассадоров акции в марте 2023 г.

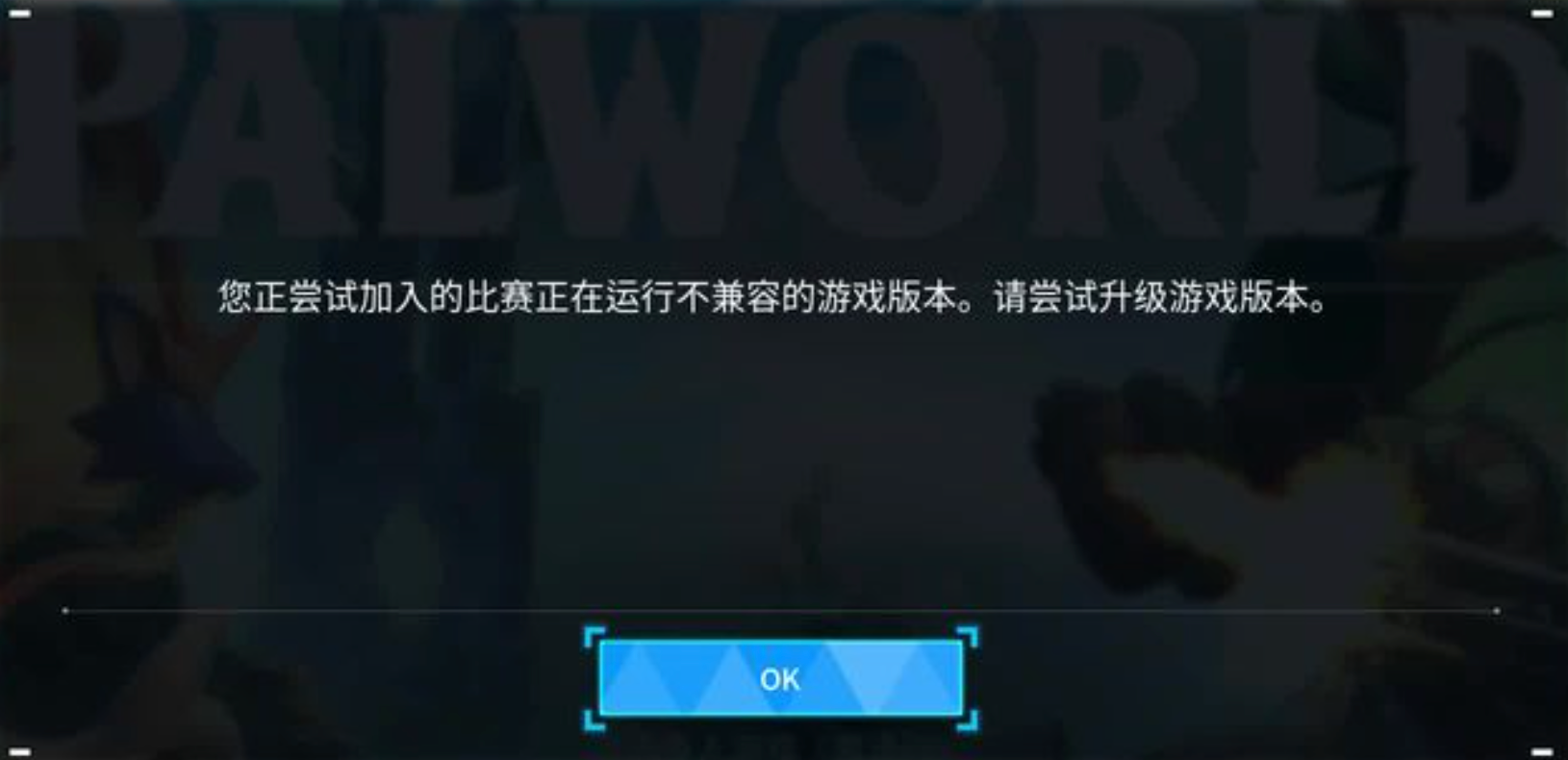

Можно ли открыть частный сервер Phantom Beast Palu одним щелчком мыши? Супер простой урок для начинающих! (Прилагается метод обновления сервера)

[Играйте с Phantom Beast Palu] Обновите игровой сервер Phantom Beast Pallu одним щелчком мыши

Maotouhu делится: последний доступный внутри страны адрес склада исходного образа Docker 2024 года (обновлено 1 декабря)

Кодирование Base64 в MultipartFile

5 точек расширения SpringBoot, супер практично!

Глубокое понимание сопоставления индексов Elasticsearch.