Глубокое понимание моделей серверных процессоров, поколений, архитектуры внутрикристальных и межкристальных соединений.

Привет всем, я Фей Ге!

существовать Предыдущие две статьи《индивидуальныйлюди CPU Модели, архитектуры поколений и микроархитектуры》 и «Поговорим о последних годах» CPU В микроархитектуре IO Процесс эволюции скорости》 , Мы представили CPU Правила модели, основные детали конструкции и поколения CPU из Ключевые изменения. В этом разделе перейдем к изсерверу, который больше подходит для нашей работы. CPU Принципиальная часть.

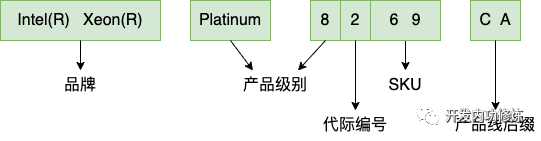

Модель процессора, которую я случайно нашел, — это процессор Intel(R) Xeon(R) Platinum 8260. Что означают цифры в этой модели процессора и какую ценную информацию мы можем из них получить. Давайте воспользуемся этой моделью для интерпретации современных принципов работы серверных процессоров.

1. Правила модели серверного процессора Intel

сервер CPU Хотя в настоящее время на рынке есть arm и RISV-V Архитектура вышла на рынок, но самые популярные бренды все еще x86 Архитектура, в основном производители Intel и AMD Две семьи.

в Intel Запуск модели суббренда для серверного рынка. Ксеон. Сегодня мы в основном фокусируемся на Intel из Xeon CPU Начнем со вступления.

Первая часть — логотип бренда.。Intel(R) Xeon(R) значит из-за этого Intel из Xeon сервер CPU。 Вторая часть CPU уровень。Intel существовать 2017 Несколько лет назад на сервер CPU это использовать E3、E5 и E7 из способа названия. в E3 из означает процессор начального уровня уровня серверов, E5. Он представляет собой средний класс, а E7 — высший класс. Этот метод именования аналогичен методу именования настольных процессоров. i3、i5 и i7, чем больше число, тем выше оценка. Но существовать 2017 лет спустя, начните использовать Платина, Золото, Серебро.

Кроме того, он представляет собой строку уровней, например Platinum и. Первая цифра после из имеет соответствующее отношение из.

- если число 8、9 Оба представляют собой Platinum ряд, позиционируемый как элитный

- если число 6、5 Оба представляют собой Gold ряд, расположенный посередине

- если число 4 означает из есть Silver Серебряный медальный ряд, позиционируемый как сервер начального уровня. CPU

третийчастьизодна цифраозначает из есть CPU из поколения в поколение。Это 2017 Идентификация поколений семейства масштабируемых процессоров началась после года. Чем больше число, тем больше CPU Архитектура новее.

- 1 Представляет первое поколение масштабируемых процессоров, соответствующее кодовое название. Skylake(2017 выпущен в 2016 году) из Архитектурадизайн

- 2 Представляет масштабируемый процессор второго поколения, соответствующее кодовое название. Cascade Lake(2019 выпущен в 2016 году) и Casecade Lake-R(2020 выпущен в 2016 году) из Архитектурадизайн

- 3 Представляет масштабируемый процессор третьего поколения, соответствующее кодовое название. Cooper Lake(2020 выпущен в 2016 году) и Ice Lake(2021 выпущен в 2016 году)из Архитектурадизайн

- 4 Представляет масштабируемый процессор четвертого поколения, соответствующее кодовое название. Sapphire Rapids(2023 выпущен в 2016 году)из Архитектурадизайн

Четвертая часть SKU серийный номер。Это CPU Производители разрабатывают серийные модели, чтобы облегчить управление запасами всей продукции. номер. Это похоже на штрих-коды на продуктах и книгах в супермаркетах. ISBN Число,Удобно запрашивайте и управляйте продуктами и запасами. Вообще говоря,Чем больше индивидуальное значение, тем лучше производительность.,Но не совсем.

Пятая часть — суффикс линейки продуктов.。в C Представительский заказ CPU слот. вопрос Поддерживает жидкостное охлаждение. Н означает из есть Для связи/сети/NFV Оптимизация виртуализации сетевых функций. Т означает из есть может удовлетворить требования длительного использования 10 Ежегодная поддержка жизненного цикла. П Представляет IaaS Оптимизация облачной среды. В Представляет Saas Оптимизация облачной среды.

2. Введение в поколения серверных процессоров

сервер CPU из Межпоколенческого развитияи PC Бытовое использование CPU Процесс из в основном такой же, как из, но метод наименования существования другой. сервер CPU из поколения в поколениеот 2017 из Skylake начинать,Назван в честь первого поколения масштабируемых процессоров. Следующий из поколения в поколение Именование - это всесуществоватьэтотиндивидуальный Обновление на основе。

время | Алгебра | Поколения процессоров | Технология процесса | микроархитектура |

|---|---|---|---|---|

2017 | 1-е поколение | Skylake(server) | 14nm | Skylake |

2019 | 2-е поколение | Cascade Lake | 14nm | Skylake |

2020 | 3-е поколение | Cooper Lake | 14nm | Skylake |

2021 | 3-е поколение | Ice Lake(server) | 10nm | Sunny Cove |

2023 | 4-е поколение | Sapphire Rapids | 7nm | Golden Cove |

в Мы упомянули в началеиз 8260 Относится ко второму поколению, 2019 г. Год выпуска, соответствующее кодовое название Cascade Lake。

существоватьвтороймасштабируемый процессорэтотиндивидуальныймежпоколенческий, используя из 14nm Мастерство. Это поколение включает в себя как серверы ЦП, в том числе физические лица PC ПРОЦЕССОР. для частных лиц PC Процессор принадлежит Core i7 и i9 Ждем модель. К Всерверу приписано Xeon Платина, Ксеон Золото, Ксеон Серебро, Ксеон Бронза.

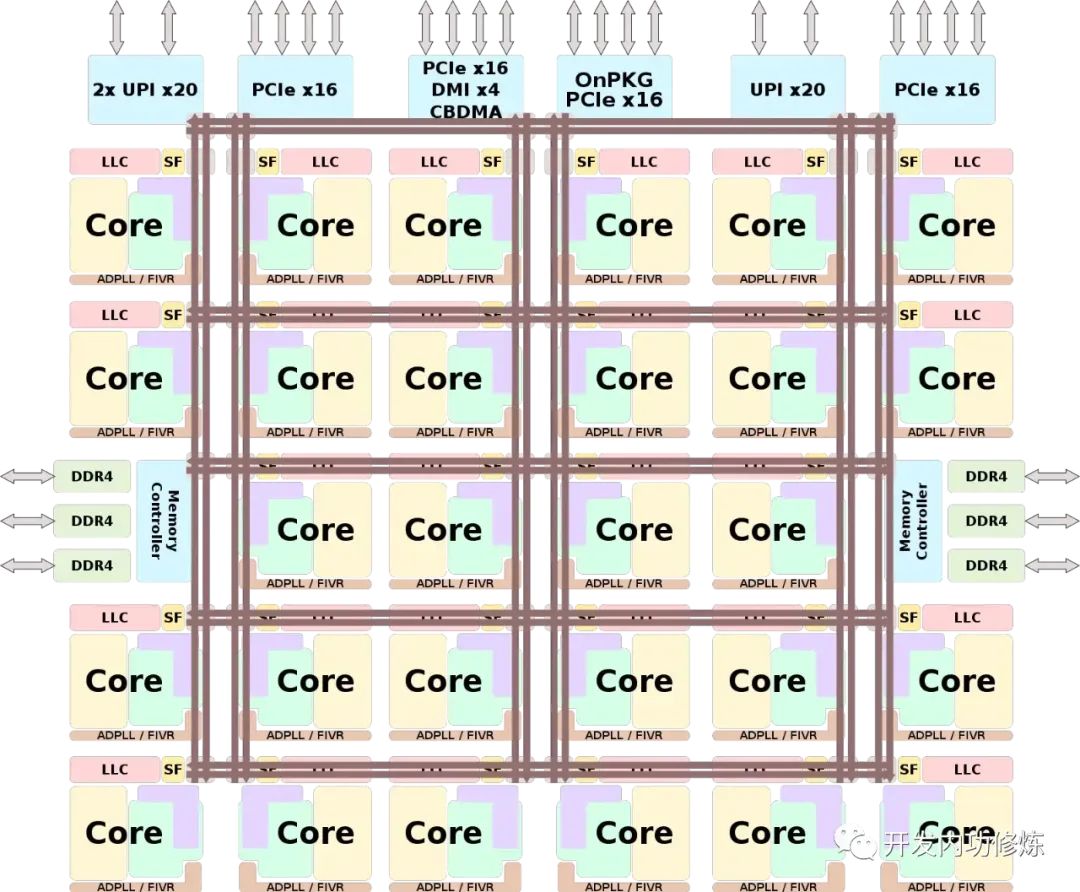

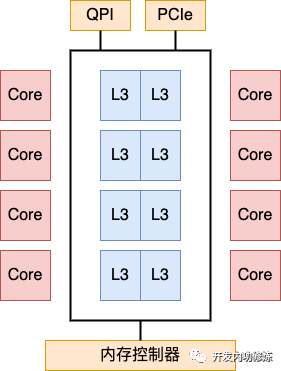

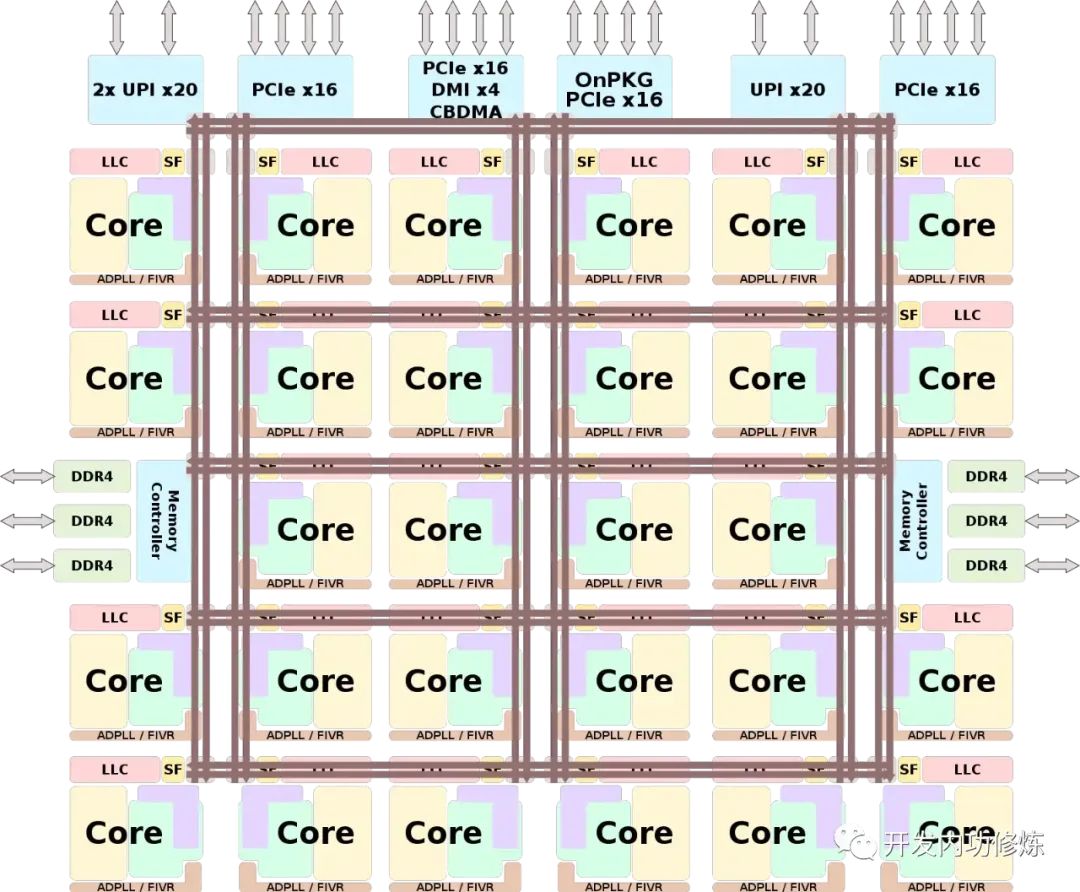

всуществовать Xeon В серии Platinum он может поддерживать до 28 индивидуальныйфизическое ядро Сердце. Ядерное больше индивидуально человек PC CPU Самая большая разница между ними. Изображение ниже 28 физическое ядро CPU Структура чиповой системы следующая.

В основном разделен на три части.

Первый в основном IMC(integrated memory контроллер) контроллер памяти。

Это тот, что на картинке выше Memory Controller。Cascade Lake поддерживатьизсервер Характеристики Память DDR4 2933 МГц. Из рисунка видно, что это такое CPU Два модуля контроллера памяти, каждый контроллер памяти может поддерживать 3 каналы памяти (каналы), каждый канал можно подключить к двум DIMM Модули памяти поддерживают максимальное количество вставок 2*3*2 = 12 карта памяти.

второйиндивидуальныйбольшойчасть То есть каждыйиндивидуальныйфизическое ядро Понятно。

этотиндивидуальныймежпоколенческийсередина Принять изда Mesh Архитектура。существовать Mesh В Архитектуре положить всю изфизику означает положить все изфизическое Ядро устроено согласно ХОРОШО, колонна имеет двумерную структуру. о Mesh Архитектура будет представлена в четвертом разделе нашей жизни.

существовать Каждыйиндивидуальныйнад ядромиз LLC Да, мы часто говорим из L3 уровень кэша, по сути LLC Это кэш последнего уровня (Last Level Cache) по смыслу, название более точное. Стоит отметить, что хотя LLC Оно разделено на существование индивидуальное. В каждом ядре есть кусочек, а индивидуальное целое. CPU Все на из LLC Это все общее.

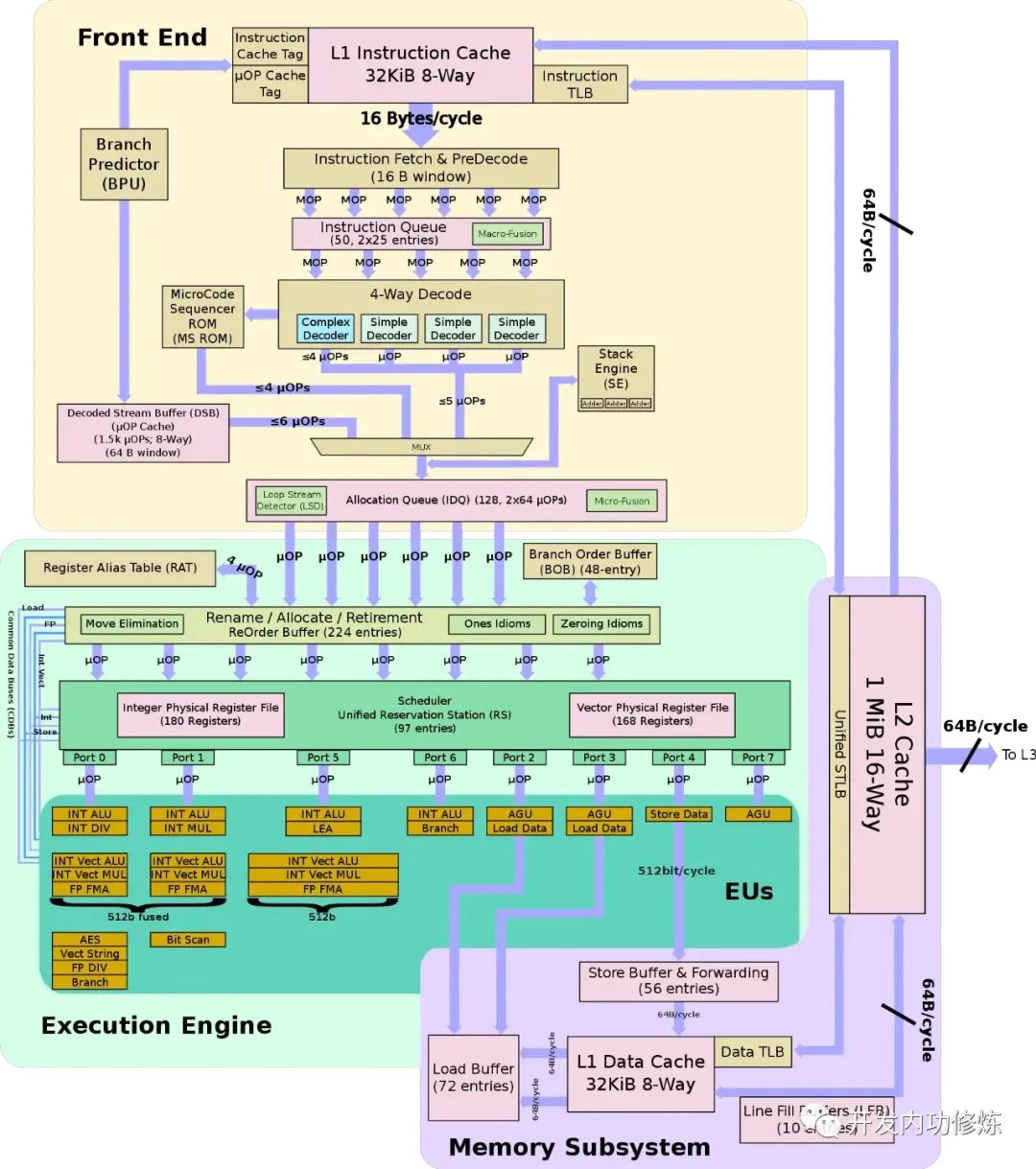

Каждыйиндивидуальныйфизическое внутренний источник энергии индивидуальныйлюди PC CPU Так же, как и ядра Medium и Z, все они используют Skylake микропроцессор Архитектурадизайниз。Каждыйиндивидуальныйфизическое ядроиметь 32 KiB из L1 Кэш инструкций, 32 KiB из L1 Кэш данных, 1 MiB из L2 кэш. Подробнееиз Skylake Схема архитектуры микропроцессора выглядит следующим образом.

Третья по величине часть Notrh Cap часть。

Этот раздел содержит PCIe Шина (используется для подключения видеокарт, жестких дисков и т. д.) и UPI автобус (для нескольких CPU межчиповое соединение).

о шина PCIe,нассуществоватьиндивидуальныйлюди CPU измодель、межпоколенческий Архитектураимикроархитектураупоминается в. Это стандарт компьютерной шины расширения, используемый для подключения высокоскоростных компонентов и высокоскоростных последовательных кабелей. второе поколение Cascade Lake поддерживатьизда PCIe 3.0 Стандартная одноканальная скорость 8 GT/s (984.6 МБ/с). Используется для подключения высокоскоростных устройств, таких как видеокарты или твердотельные накопители.

UPI Автобус используется для нескольких CPU Межчиповое соединение использует из. Ксеон Platinum ряд CPU поддерживать 3 индивидуальный UPI соединять. И низкий уровень Xeon Gold 5xxx、Xeon Silver Просто подождиподдерживать 2 индивидуальный UPI。о UPI Об этом мы поговорим позже отдельно.

3. Сетчатая многоядерная архитектура встроенной шины.

существоватьсервер CPU Архитектурадизайнсередина,Ключевая проблема, которую необходимо решить, — это разумное размещение многоядерных процессоров.,Доступ к Памятьиз с меньшей задержкой. так,Чипу также нужна «шина» для входа в ХОРОШОВзаимовязаны.

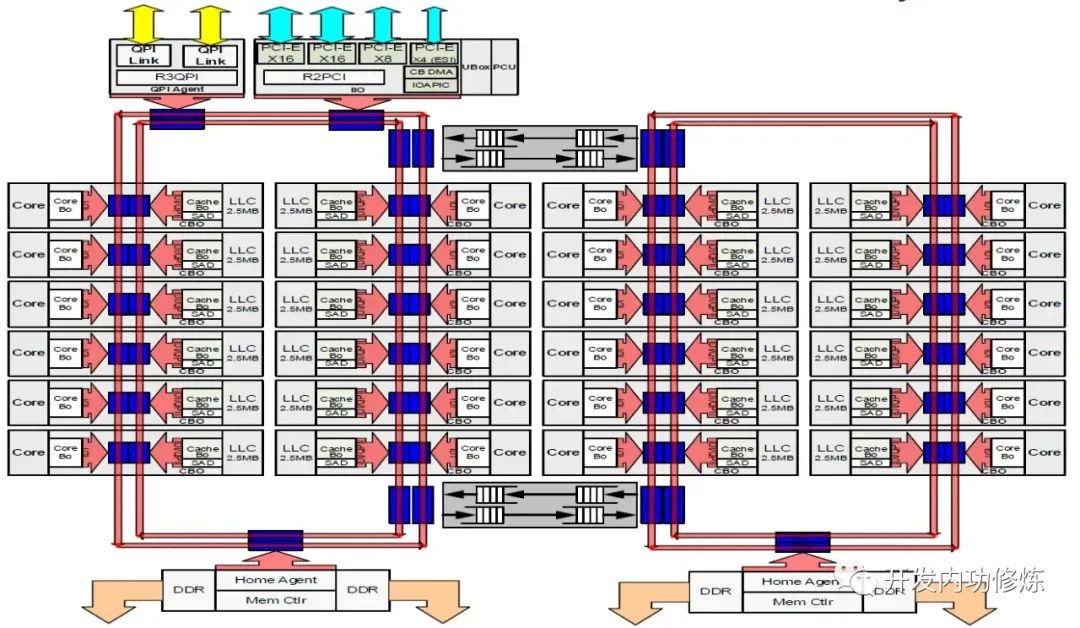

существовать 2017 Годиз Skylake Ранее Интел Метод выборки – кольцевое соединение, также называемое Ring Архитектура。существовать Ring Архитектуравнутри,Все ядра соединены индивидуальным кольцом. Каждый раз каждому ядру нужен доступ к Памятьиз,Всепроходитьэтотиндивидуальныйэтотиндивидуальный Кольцо вокруг ХОРОШО。

Как мы все знаем, дальнейшее развитие сервериз было направлено на мульти- CPU Ядерное направление развития существует. По мере продвижения времени количество ядер увеличивается. Традиция Ring Архитектураизкольцевая структурасередина,Чем больше ядер,Чем больше кольцо,Задержка будет больше, если для доступа к данным Памяти используется кольцо прохождения.

Чтобы уменьшить количество ядер в кольце, Intel Также когда-то существовали элитные CPU серединадля Понятнофаршированный Болееизядерный,дизайн индивидуальной двойной кольцевой конструкции. так,На кольце меньше ядер.,Путь передачи данных короче.

Но даже если оно разделено на два кольца,По-прежнему останется проблема: чем больше ядер, тем больше будет задержка.,А при доступе через кольца одно будет добавлено.индивидуальныйдополнительныйиз CPU cycle из задержки, так что Broadwell Это верно Ring Жизнеустойчивость архитектуры достигнута до предела,но в лучшем случае ее можно только восполнить. 24 индивидуальныйядерный Сердце。

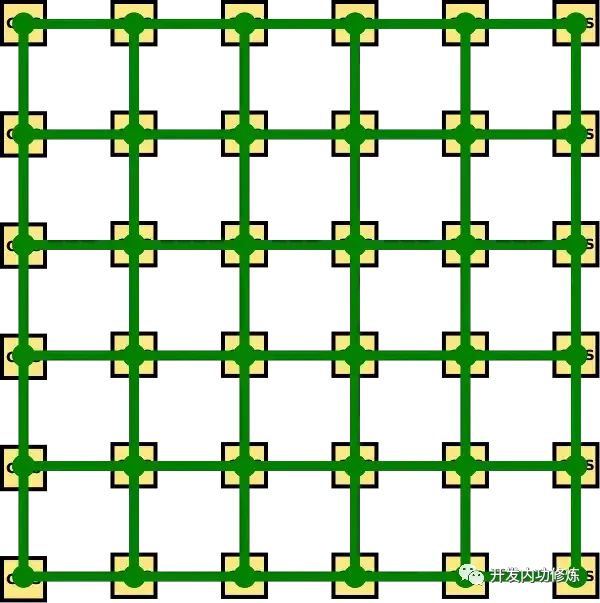

Таким образом, чтобы лучше контролировать задержку при доступе многоядерных процессоров к Память. Интел В 2017 Запущен в 2017 году Skylake принят в Mesh архитектура для проектирования многоядерных процессоров. так называемый Mesh Архитектура, то есть всё изфизическое Ядро устроено согласно ХОРОШО, колонна имеет двумерную структуру. 。

существовать Высочайшая спецификацияиз 28 индивидуальныйфизическое В конструкции атомного чипа принят 5 ХОРОШО 6 Столбец матричной структуры. в 2 В индивидуальной позиции используется буква В для размещения контроллера из Память, упомянутого выше. Далее индивидуальное физическое ставится в каждую позицию индивидуального. ядро。

После того как архитектура Ring превратилась в архитектуру Mesh, внутрикристальная шина также превратилась из одномерной структуры в двумерную.

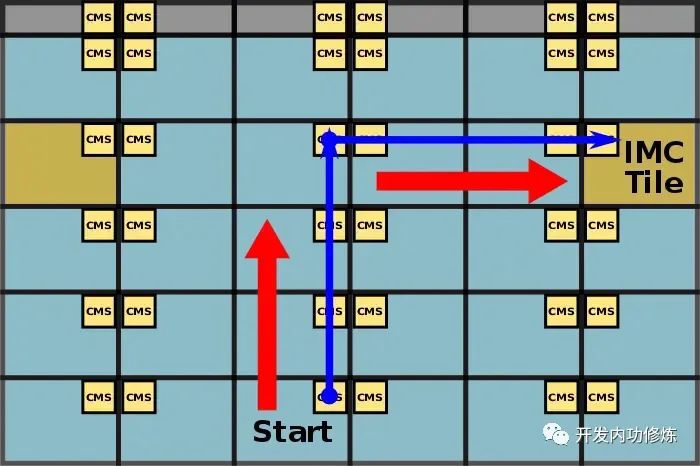

так,когда кто-тоиндивидуальныйфизическое Когда ядросуществовать получает доступ к данным Память, вы можете найти кратчайший путь для связи в этой двумерной структуре. Например, на картинке ниже Start этотиндивидуальный Расположениеизядерныйхочу посетить Память,В это время путь доступа должен идти сначала по красной стрелке вверх.,Затем следуйте по другой индивидуальной красной стрелке вправо, чтобы добраться до элемента управления Память и получить доступ к Память.

С помощью этой индивидуальной двумерной структуры,Путь к Памятьиз будет ниже,Также для существования с низкой задержкой из-за более физического дизайна корпуса. ядропоставлять Понятновозможный。существовать Cascade Lake Межпоколенческий дизайн уже на подходе 28 индивидуальныйфизическое ядро。

обратный сервер CPU Все еще продолжаю использовать Mesh Архитектура,существовать 2021 Выпущен в 2017 году ice lake , он даже больше предназначен для 7 ХОРОШО 8 Столбец матричной структуры, сложенный вместе 40 индивидуальныйфизическое ядро。

о Еще Mesh Введение в архитектуру см. https://en.wikichip.org/wiki/intel/mesh_interconnect_architecture

4. Межчиповая шина UPI для многопроцессорного соединения.

одининдивидуальный CPU Даже если ты постараешься изо всех сил, ты все равно сможешь войти. ядро все еще ограничено. Итак, еще одна идея расширения вычислений — многопроцессорное. соединение,существоватьодинсервер Установите больше наиндивидуальныйфизика ЦП, тем самым достигая расширенной вычислительной мощности.

Ранее мы видели, что каждый индивидуум CPU Все они поддерживают множественные Памятьиз, все могут ввести контроллер Память и слот з Память и з Память в ХОРОШО связь. Но современный изсервер – это, как правило, не просто индивидуальный ПРОЦЕССОР. Поэтому возникает вопрос: А. CPU Как получить доступ к другому лицу CPU Память из данных на слоте.

Ответ: UPI автобус, это Ultra Path Interconnect изаббревиатура。

существовать 17 Много лет назад CPU , используя из QPI(QuickPath Interconnect) Автобус в ХОРОШО CPU междуизвзаимосвязаны.от 2017 Начало первого поколения масштабируемых процессоров Intel Это быстрее использовать UPI(Ultra Path Interconnect) автобус. УПИ Автобусный родственник QPI автобус, с более высокой скоростью передачи данных по сравнению с 9.6 GT/s повышен до 10.4 GT/s, а энергопотребление еще ниже.

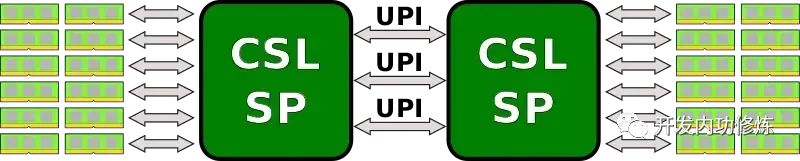

проходить UPI может обеспечить двухпроцессорную, четырехпроцессорную или даже восьмипроцессорную связь между извзаимосвязанными. Platinum Всеподдерживать 3 UPI соединять. Да Xeon Platinum ряд, двухпроцессорный способ подключения следующий

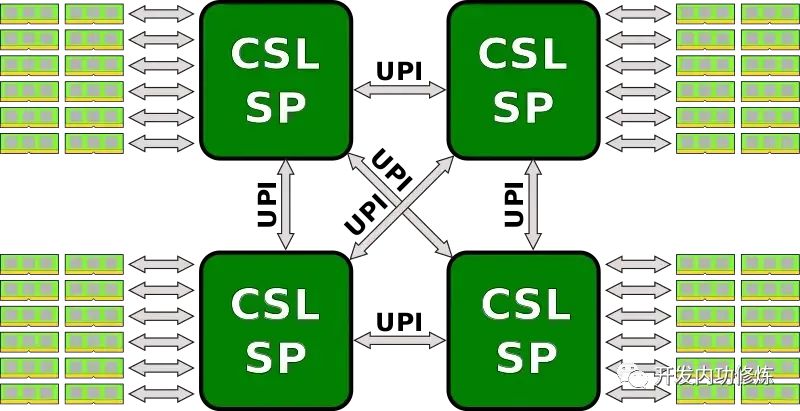

Четырехъядерный процессориз Способ подключения следующий

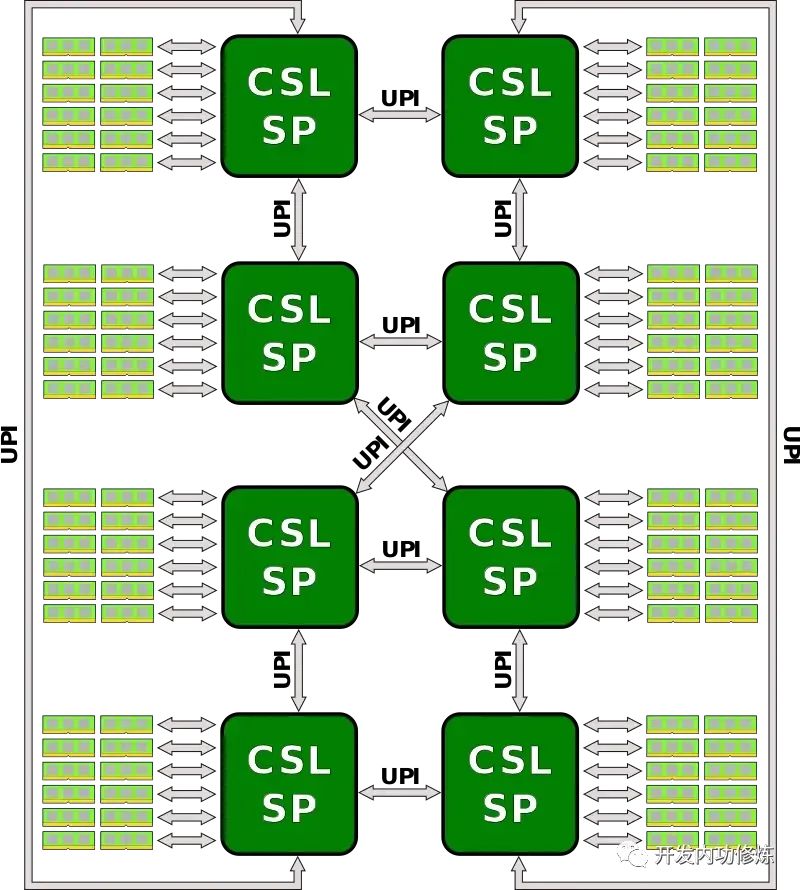

Восемь процессоров подключены следующим образом:

Intel проходить UPI шина, что значительно улучшает масштабируемость мультипроцессора. Но хотя Intel Поддержка имеет до восьми процессоров, и наиболее часто используемыми в отрасли по-прежнему являются двухпроцессорные процессоры. UPI взаимосвязаны.

Подвести итог

существуют. В этом разделе мы используем наиболее часто используемые из Intel(R) Xeon(R) Platinum 8260 модельиз CPU В качестве введения в сервер CPU Соглашение об именовании измоделей, процесс разработки каждого отдельного поколения и встроенная шина. Mesh архитектура,кинозал ссылку УПИ.

Intel изсервер CPU от 2017 В начале года было принято новое соглашение об именах поколений. 2017 год Годиз skylake Будучи первым поколением, в настоящее время он находится в четвертом поколении. существуют В каждом поколении Platinum Они все топовые CPU модель, за которой следует Gold、Silver。

в 8260 Это масштабируемое устройство второго поколения. CPU, код генерации Cascade Озеро. Мы нашли это по структурной схеме чипа. В основном включает в себя контроллер Память, различные индивидуальнофизические ядро、шина PCIe、UPI автобус и т.п.часть.

Чтобы лучше достичь большего изфизического качества с низкой задержкой из ядро,8260 Принять из Mesh Архитектура организовать все изфизическое ядро。существовать Mesh В Архитектуре положить всю изфизику означает положить все изфизическое Ядро устроено согласно ХОРОШО, колонна имеет двумерную тип.. Может более эффективно контролировать соединения ядро задерживается при доступе к Память.

Помимо внутрифильмового дизайна ещё изфизика CPU Помимо идеи, еще одним способом расширения вычислительной мощности является расширение вычислительной мощности одного компьютера. CPU。И ещеиндивидуальный CPU междудапроходить UPI Автобус в ХОРОШОвзаимосвязаныиз。проходить Автобус,Один сервер может реализовать до восьми независимо связанных ЦП.

Пожалуйста, перешлите эту статью своим одноклассникам/коллегам/друзьям, чтобы они учились вместе!

Не удалось установить программное обеспечение Mitsubishi. Возможно, возникла проблема с реестром.

Разрешение ошибок проекта SpringBoot 3 mybatis-plus: org.apache.ibatis.binding.BindingException: неверный оператор привязки

Более краткая проверка параметров. Для проверки параметров используйте SpringBoot Validation.

Поиграйтесь с интеграцией Spring Boot (платформа запланированных задач Quartz)

Несколько популярных режимов интерфейса API: RESTful, GraphQL, gRPC, WebSocket, Webhook.

Redis: практика публикации (pub) и подписки (sub)

Подробное объяснение пакета Golang Context

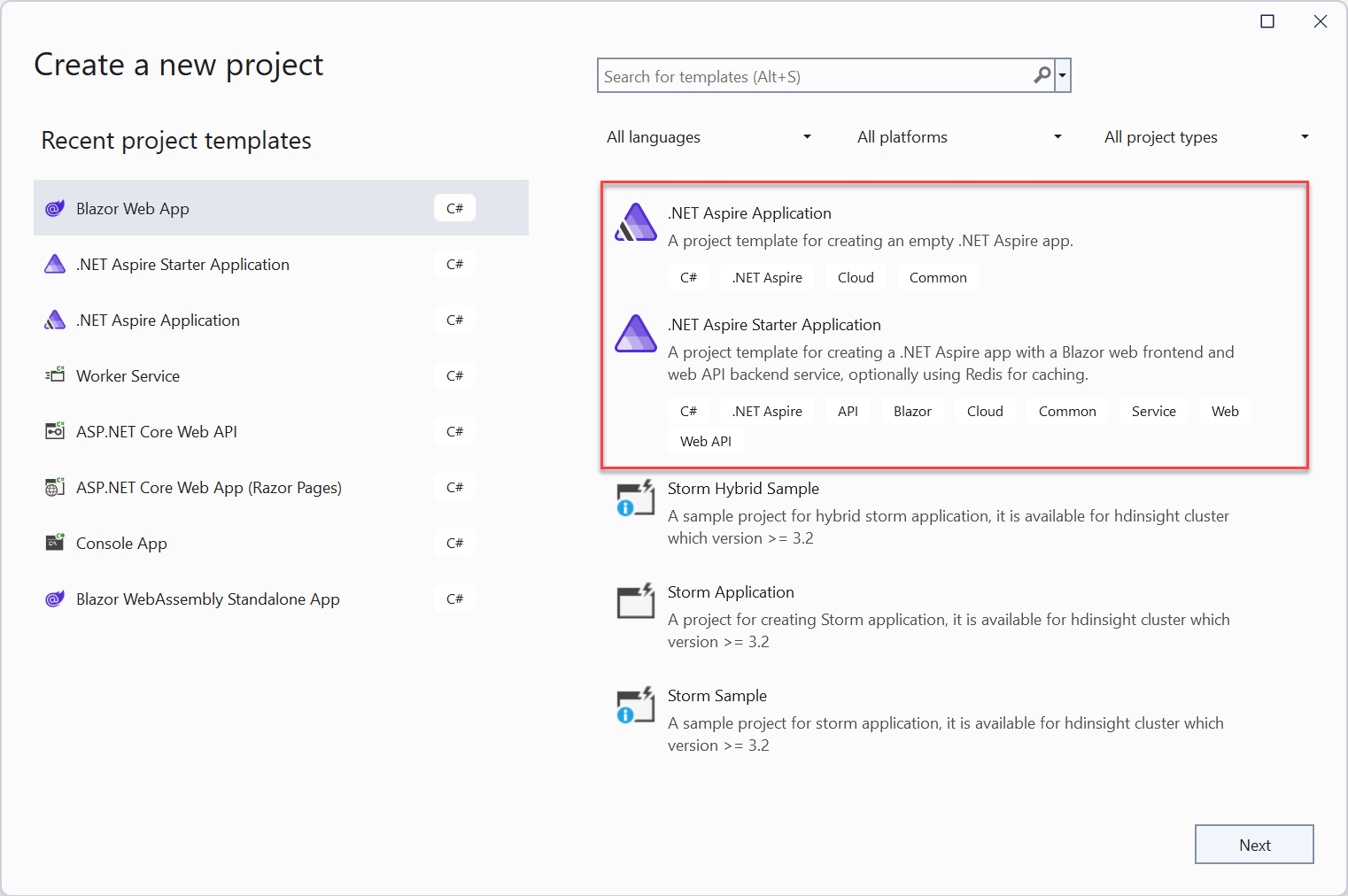

Краткое руководство: создайте свое первое приложение .NET Aspire

Краткое обсуждение метода пакетной вставки MyBatis: обработка 100 000 фрагментов данных занимает всего 2 секунды.

[Инструмент] Используйте nvm для управления переключением версий nodejs, это так здорово!

HTML можно преобразовать в word_html для отображения текстовых документов.

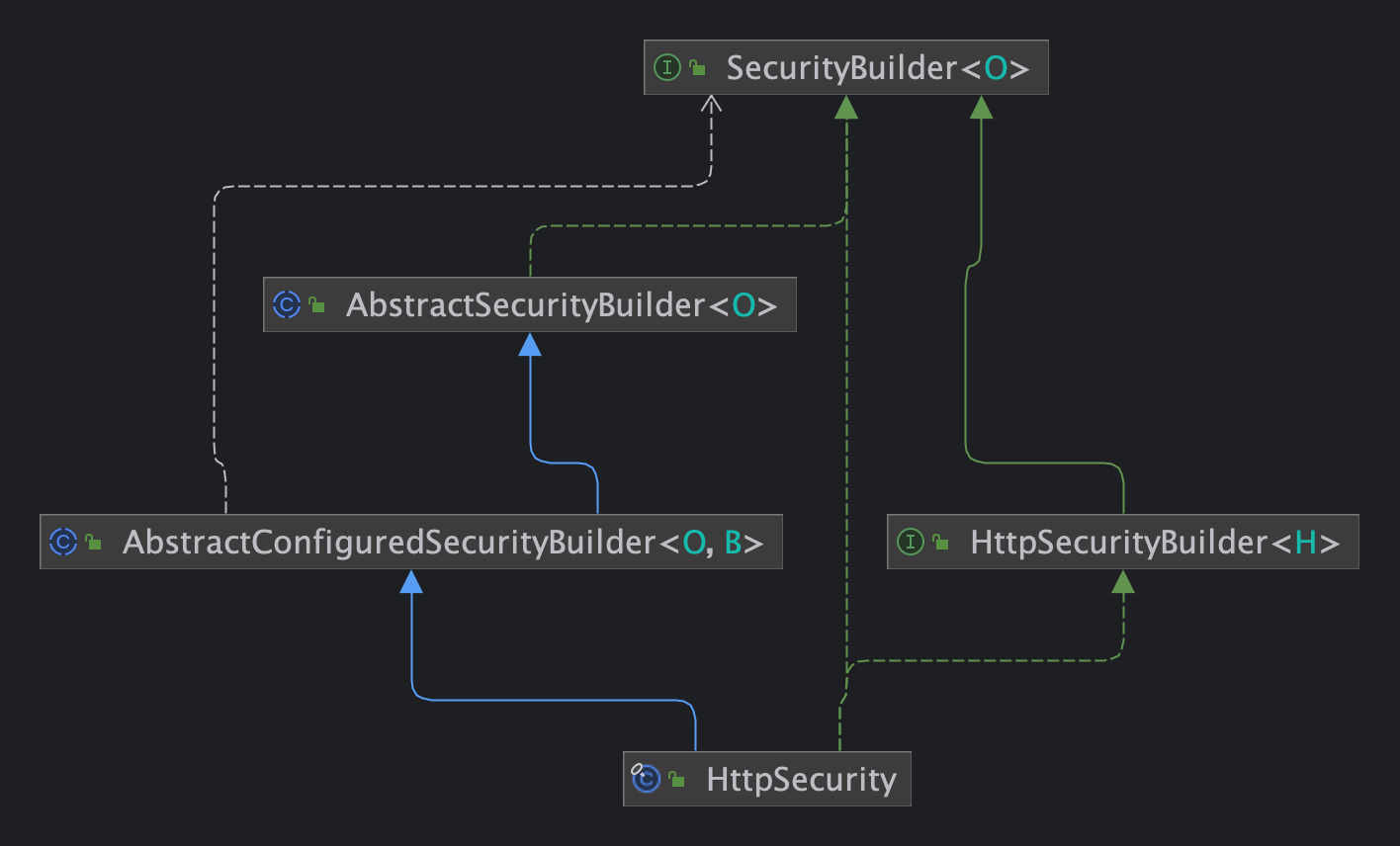

Статья Spring Security 6.x для быстрого понимания принципов настройки

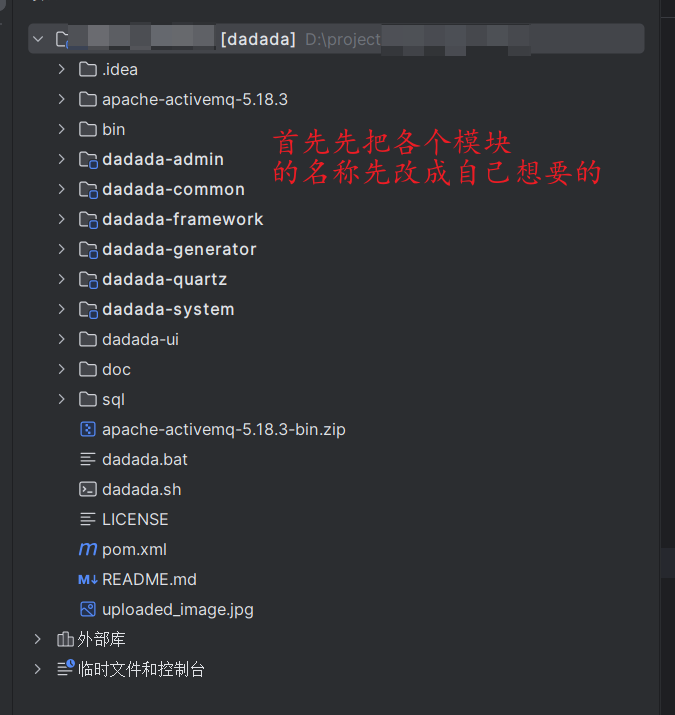

Не забудьте изменить имя каждого модуля RUOYI один раз, чтобы избежать мошенничества ~~~

Научите вас шаг за шагом, как интегрировать систему обслуживания клиентов Hunyuan AI Q&A от 0 до 1.

Подробное объяснение Gzip: принципы и применение алгоритмов сжатия.

Скачать Tomcat - ссылка для скачивания на официальном сайте tomcat7, tomcat8, tomcat9

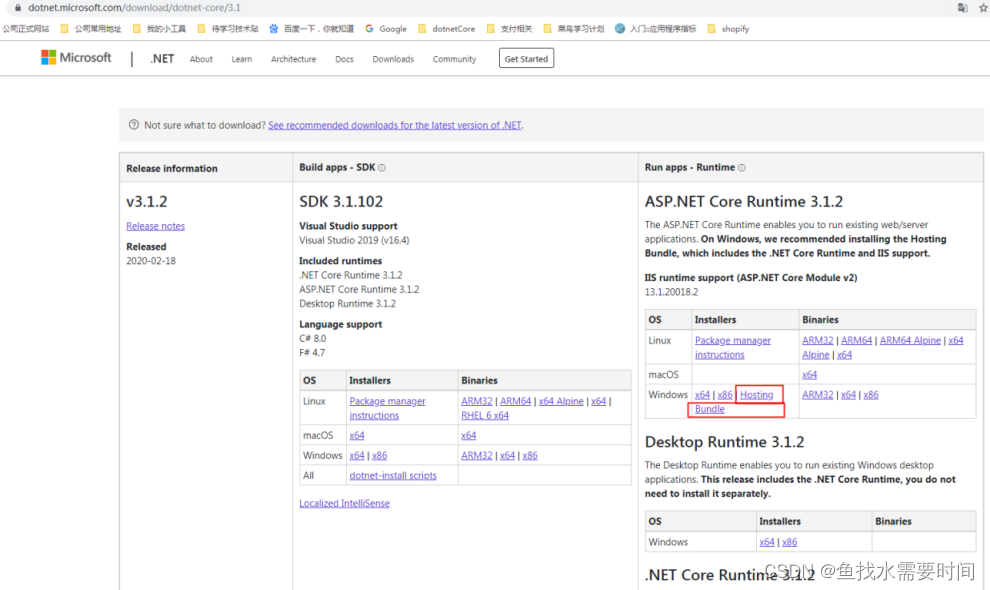

Развертывание IIS.NetCore

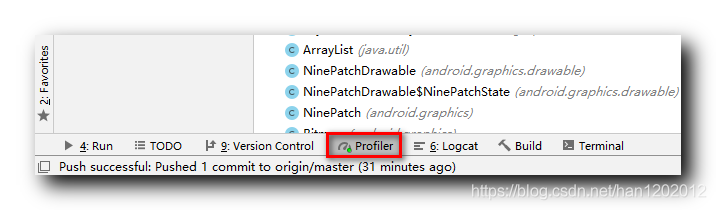

[Оптимизация памяти Android] Общие функции инструмента Android Profiler (мониторинг памяти | снимок памяти)

Встроенная в Springboot пользовательская конфигурация временного каталога, связанного с Tomcat.

Краткое руководство по началу работы с Element-UI

Руководство пользователя ГОРМ

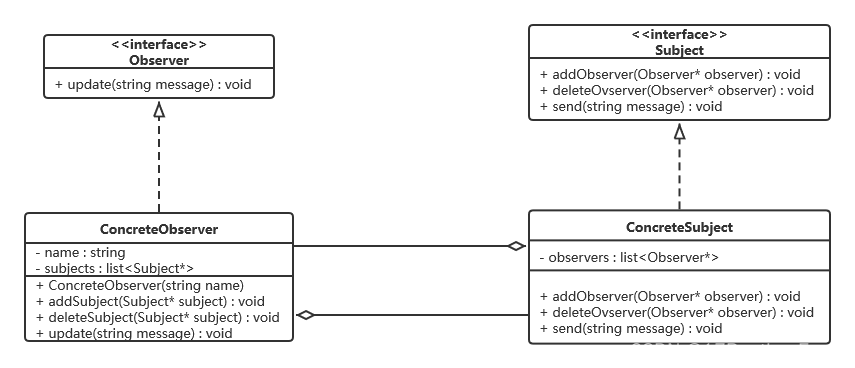

Одна статья для понимания артефакта развязки внутренних компонентов Spring Event (событие Spring)

Java перехватывает строку после определенного символа_java, как перехватить строку

Давайте кратко поговорим о технологии копирования на записи.

Выполнение собственных условий SQL-запроса в MyBatis Plus

Напоминание о выпуске общедоступной учетной записи WeChat (интерфейс сообщения шаблона общедоступной учетной записи WeChat)

5 шагов для установки среды протокола

Наиболее полные коды состояния HTTP

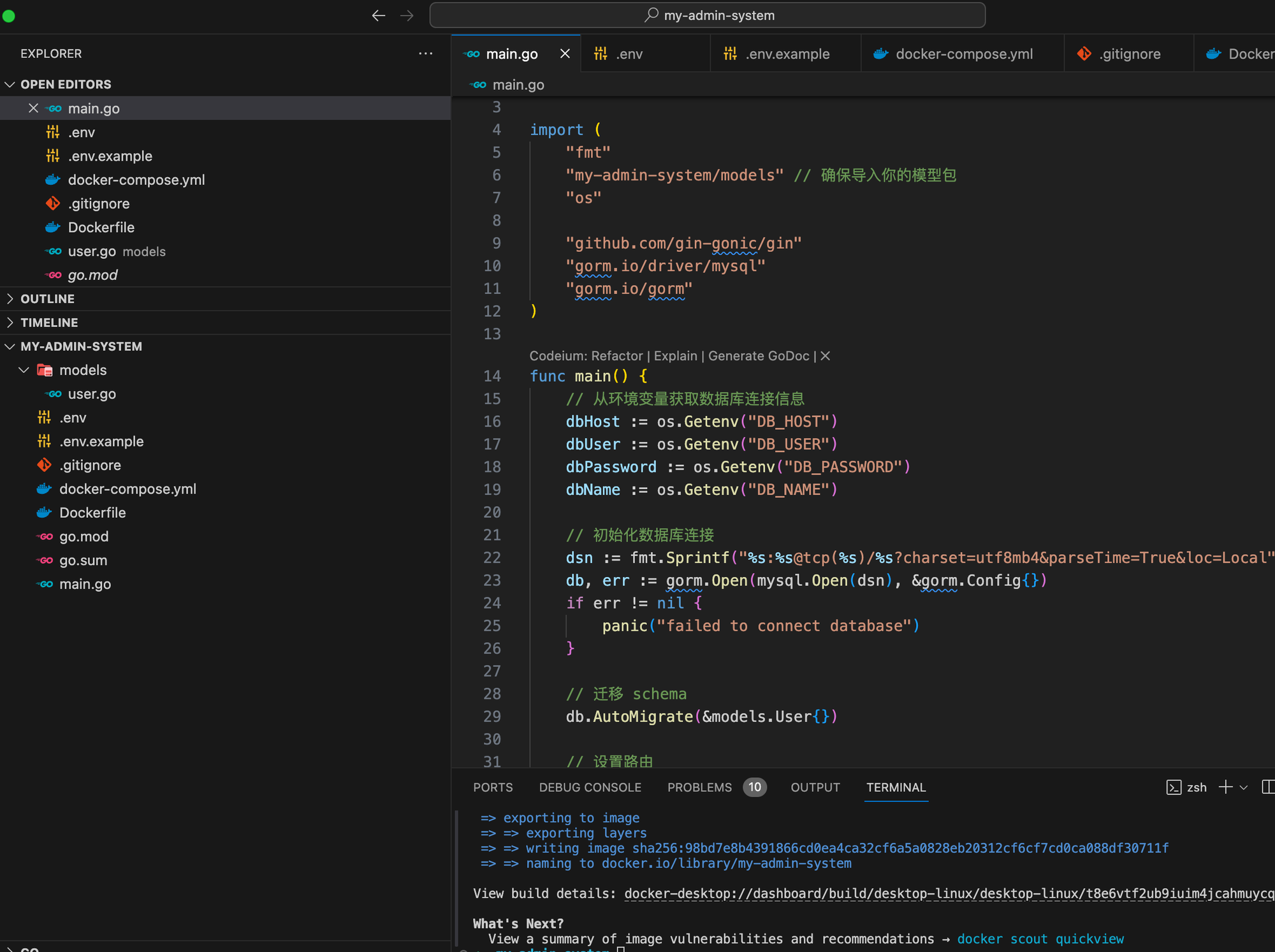

На основе языка Go мы шаг за шагом научим вас внедрять структуру системы управления серверной частью.