Дешевая архитектура FPGA+MCU-T-FPGA

Я хотел бы поделиться платой разработки, которая мне очень нравится. В последнее время я прочитал много книг по разработке FPGA (я не написал несколько строк кода), но это не влияет на мое понимание.

Эта плата обладает гибкостью FPGA и универсальностью MCU, главным образом потому, что она очень дешевая! ! ! Также сделал небольшую несущую плату.

Можно подключиться к:

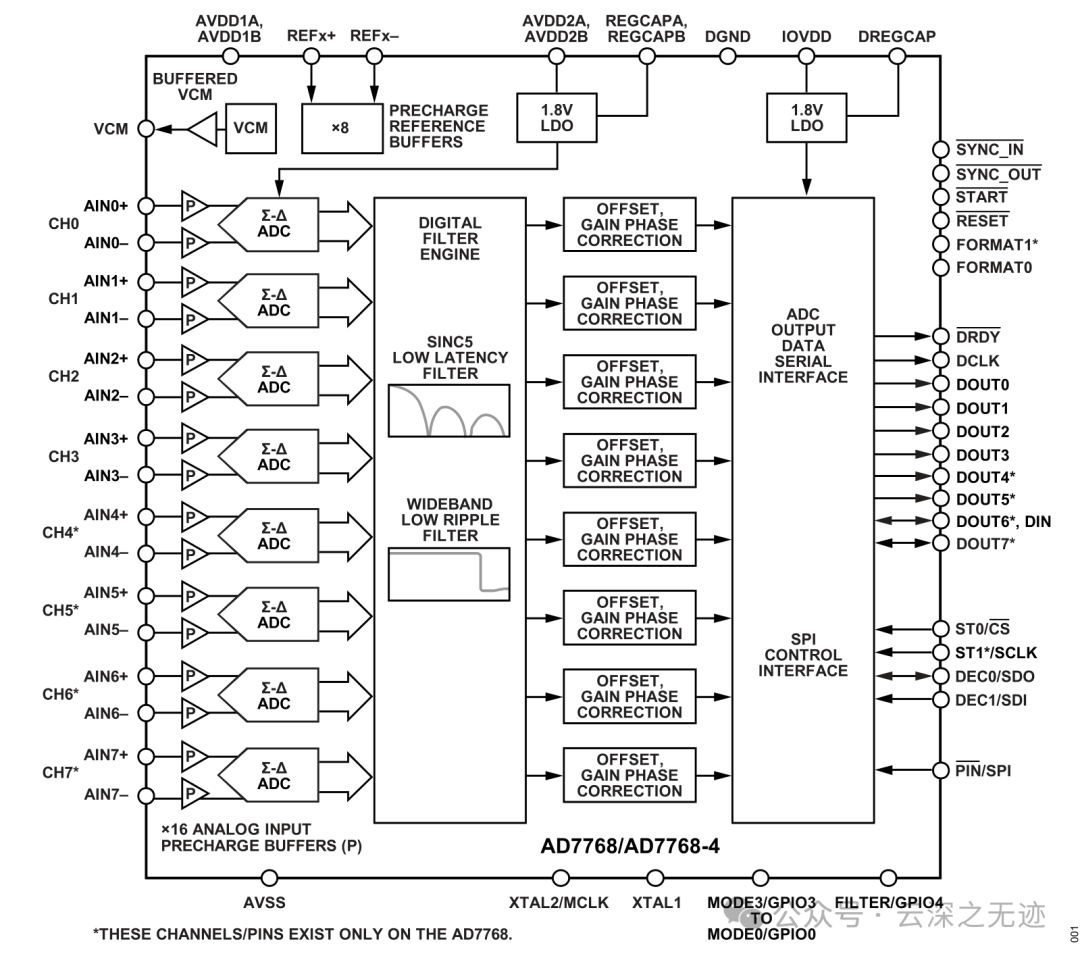

Например, такой АЦП после обработки отправляется в ESP32.

Но как это сказать. . . Протокол, который выходит из FPGA, должен быть разработан вами самостоятельно. Возможно, это самая интересная часть.

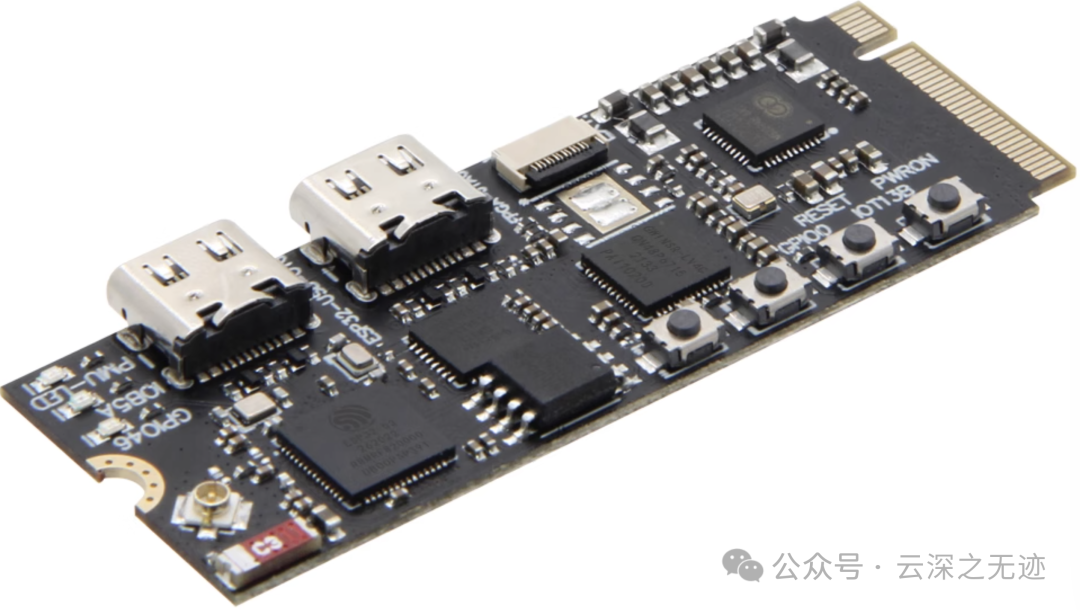

Это макет устройства выше, аккуратный и элегантный.

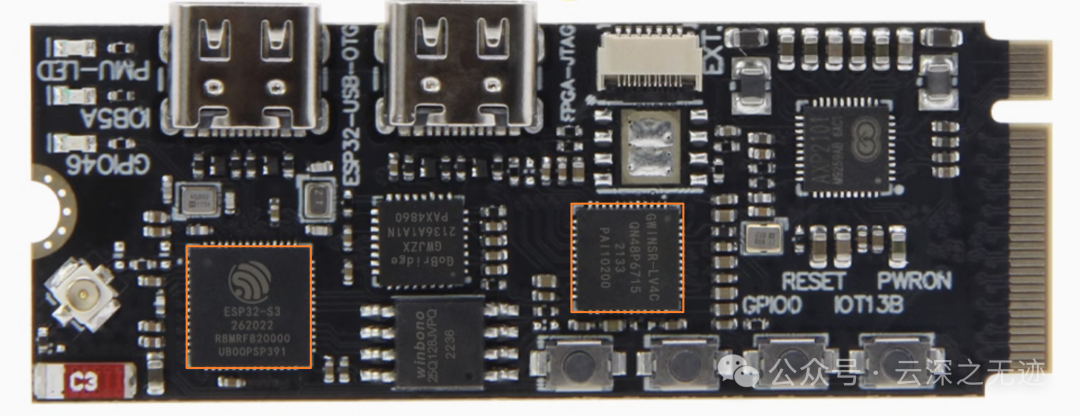

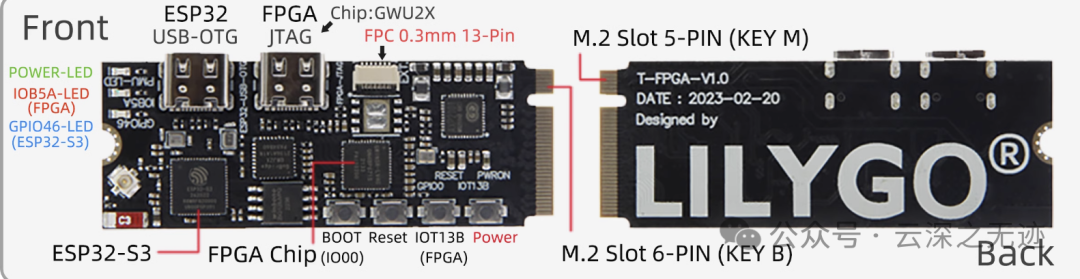

Разложенные на плоской поверхности, есть несколько заметных крупных кусков.

Разработанный в форме М2, он может быть легко заменен различными опорными пластинами, что делает его более гибким.

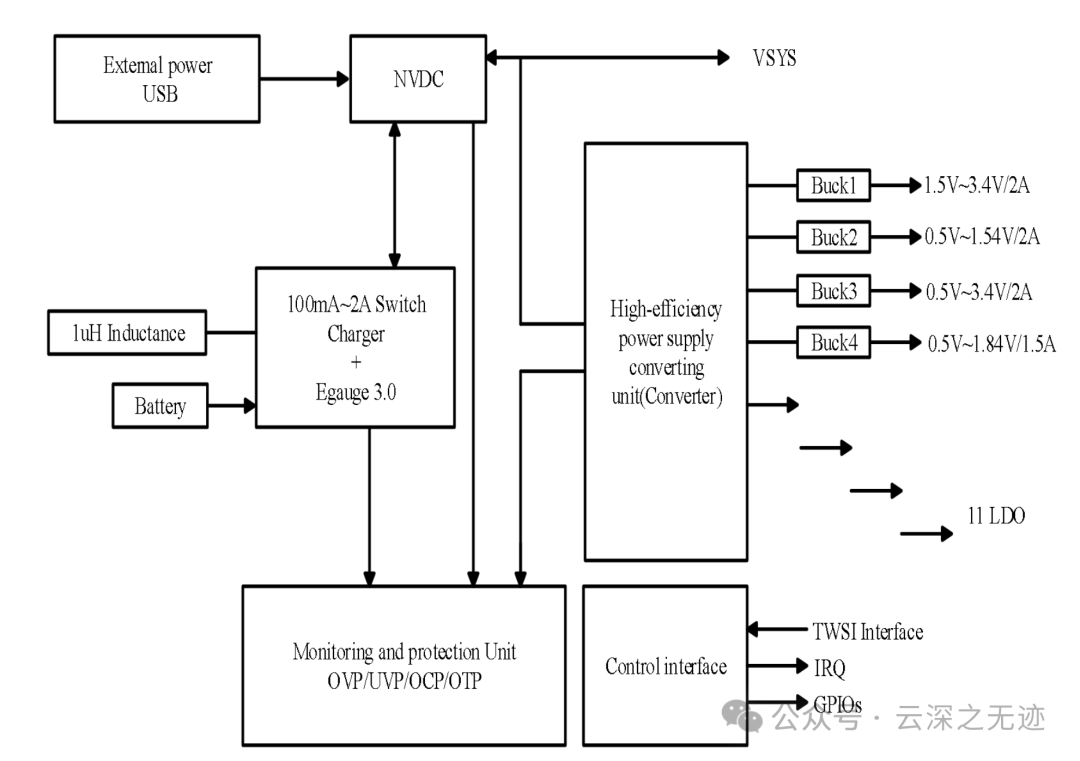

Этот с автономным питанием

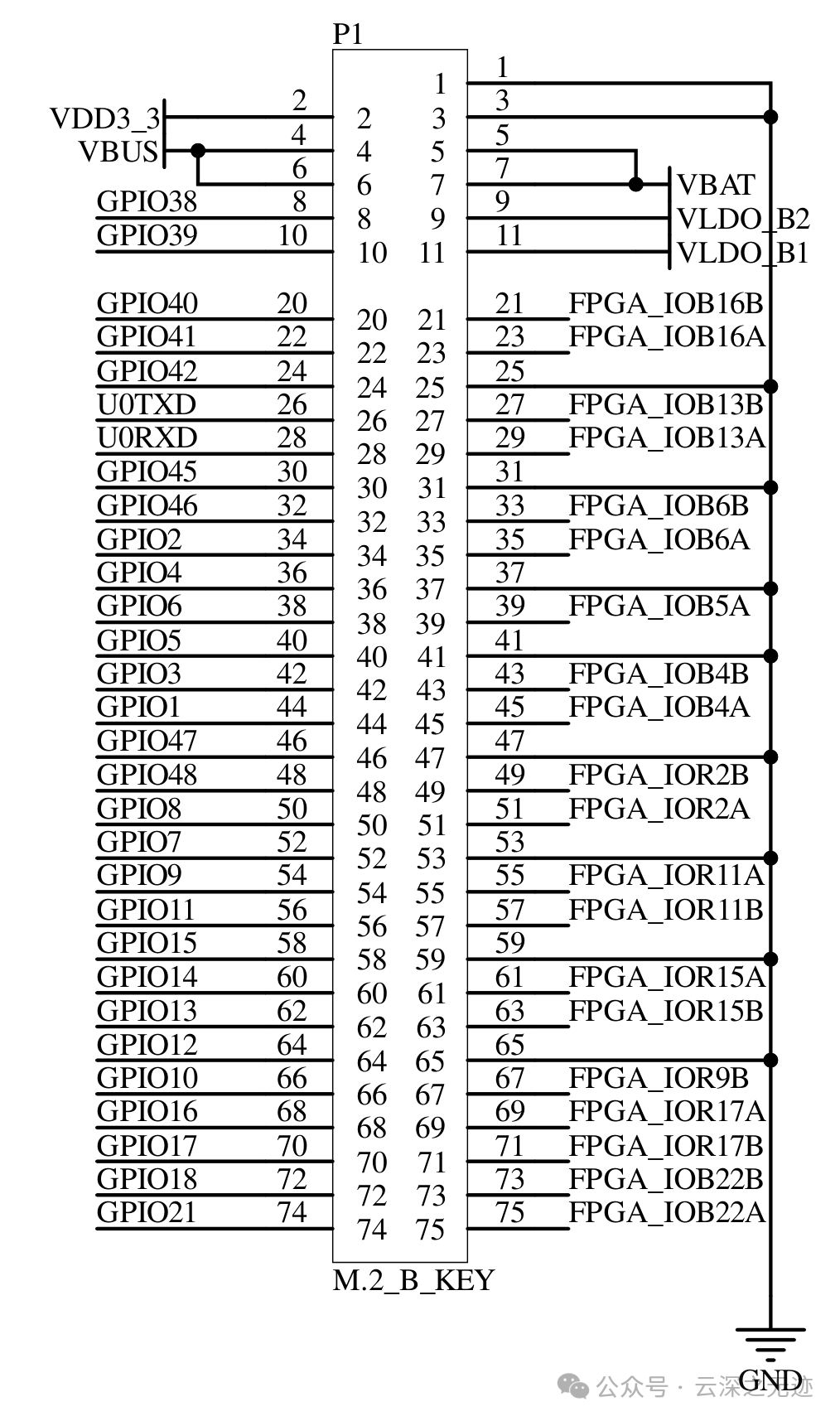

Много ИО

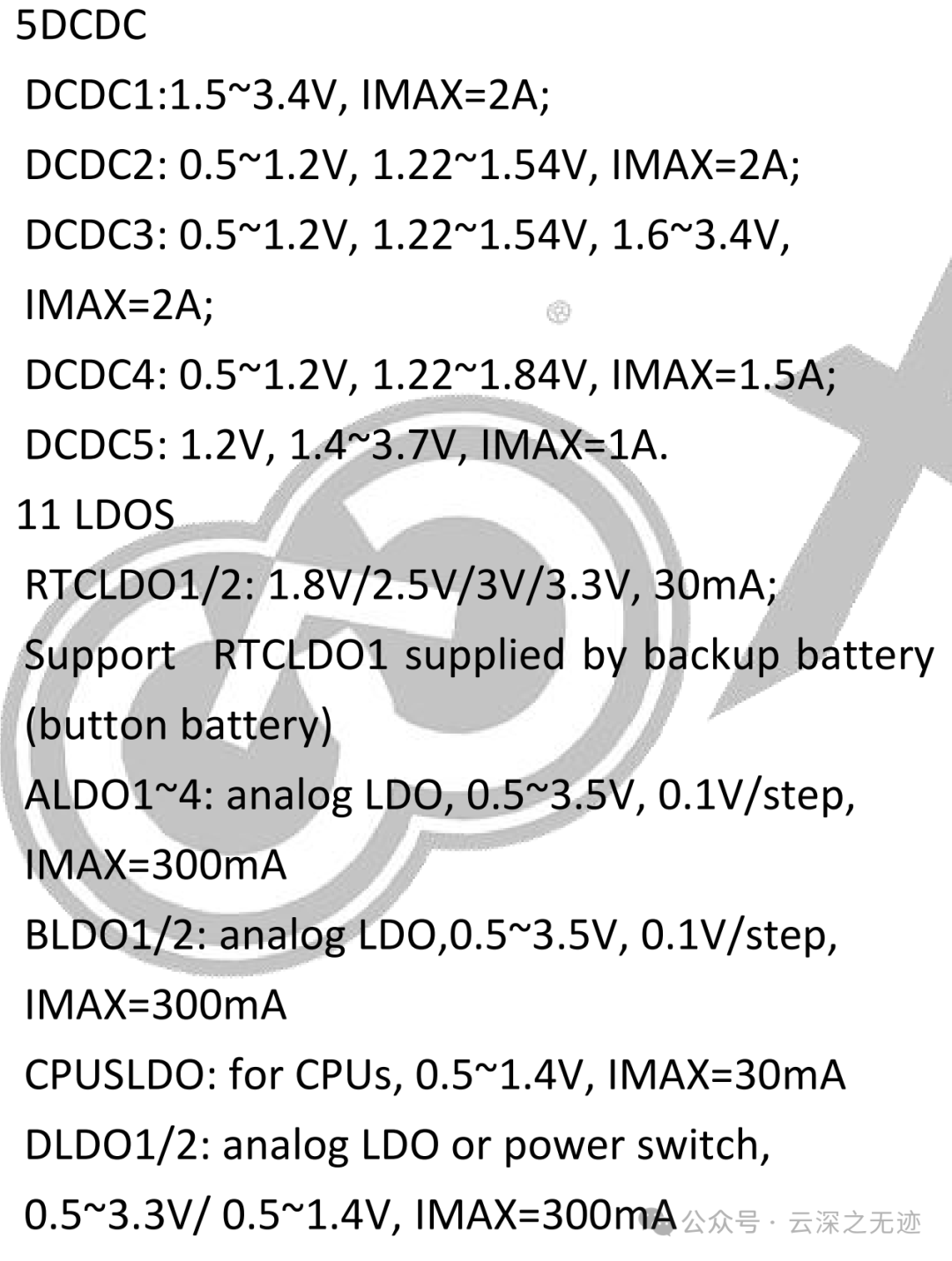

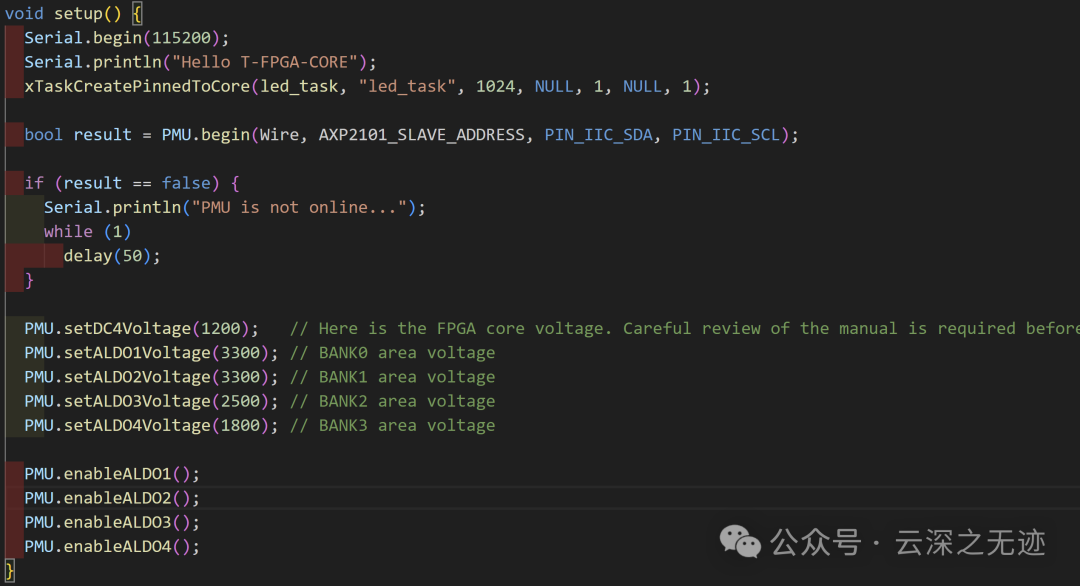

Потому что в FPGA слишком много типов блоков питания,Поэтому я добавил индивидуальный PMIC,Есть многоLDOиDCDC。Одна штука = 3 штуки (чип питания nPM1300)Для ежедневного использования вы можете посмотреть этоиндивидуальный。

Программирование переключения источников питания

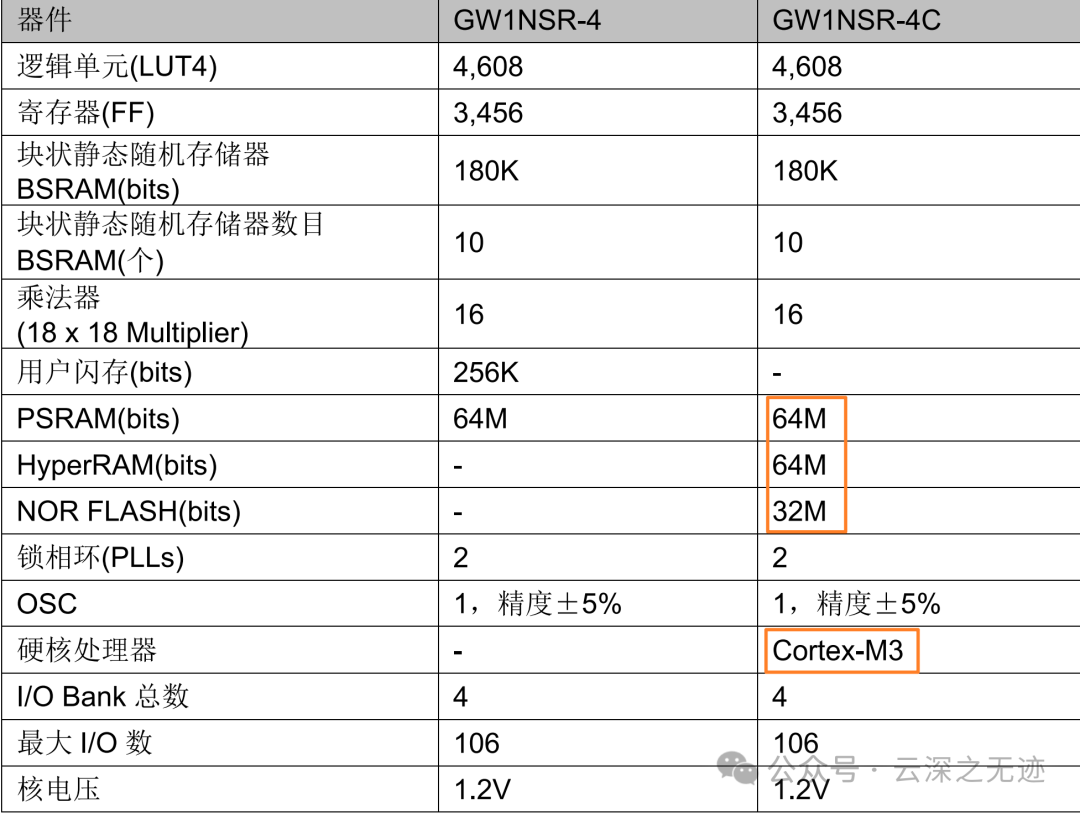

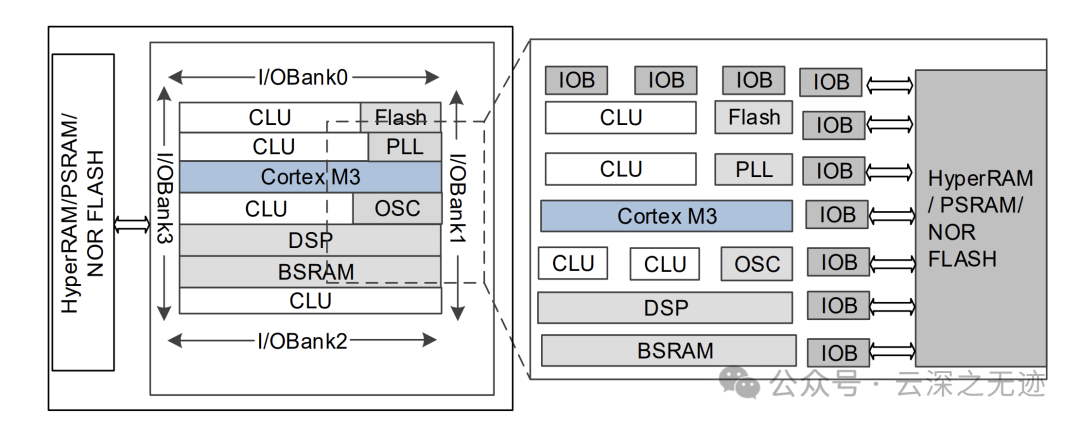

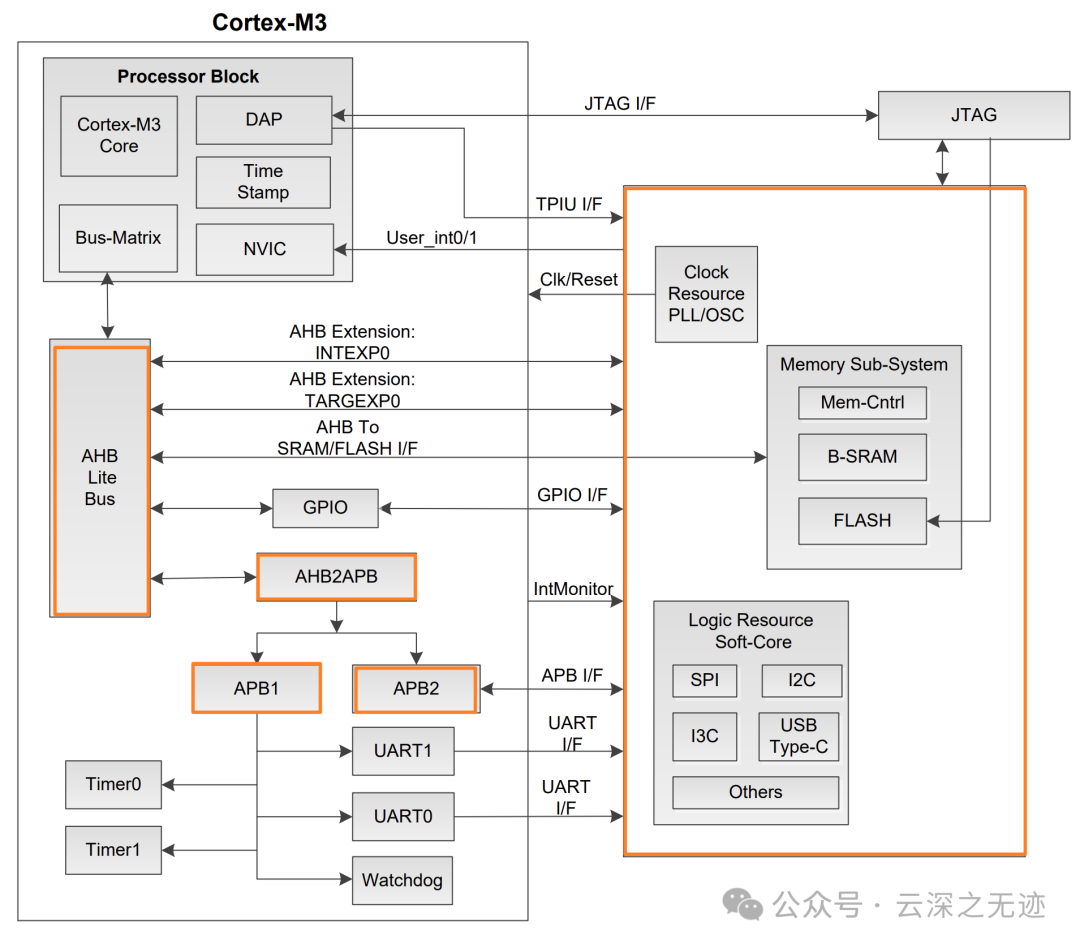

В этой ПЛИС имеется жесткое ядро M3.

По сути, M3 Core есть, но внешняя периферия тоже является логическими ресурсами в FPGA.

Вот и все, каждая разделена на две стороны

Шина APB2 подключается напрямую к ресурсам FPGA.

Блочная статическая оперативная память (BSRAM) продуктов FPGA серии GW1NSR расположена внутри устройства рядами, причем одна BSRAM занимает 3 позиции CLU внутри устройства. BSRAM предоставляет два метода использования, но эти два метода нельзя использовать одновременно.

Один используется в качестве ресурса SRAM для процессорной системы Cortex-M3 в устройствах SoC для чтения и записи данных памяти. Емкость BSRAM составляет 16 Кбит, а общая емкость — 128 Кбит (GW1NSR-4/4C).

Второй используется в качестве пользовательских ресурсов хранения. Емкость BSRAM составляет 18 Кбит, а общая емкость — 180 Кбит (GW1NSR-4/4C).

DSP расположен внутри устройства рядами, и каждый ресурс DSP занимает 9 ячеек CLU. Каждый DSP содержит два макроблока, каждый макроблок содержит два пресумматора (предварительные сумматоры), два 18-битных умножителя (мультипликаторы) и блок арифметических/логических операций с тремя входами (ALU54). А еще можно сделать модуль фильтра.

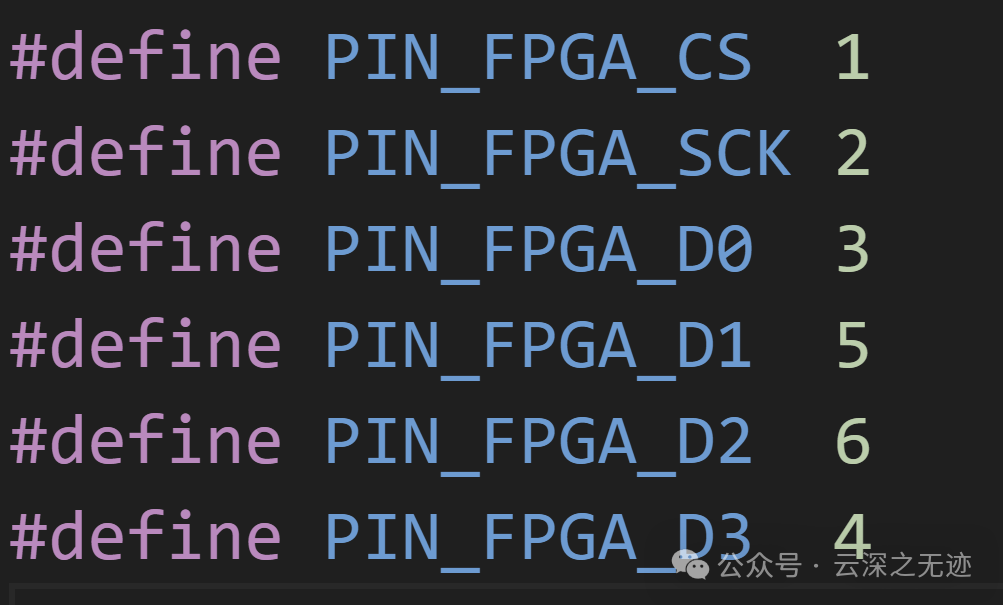

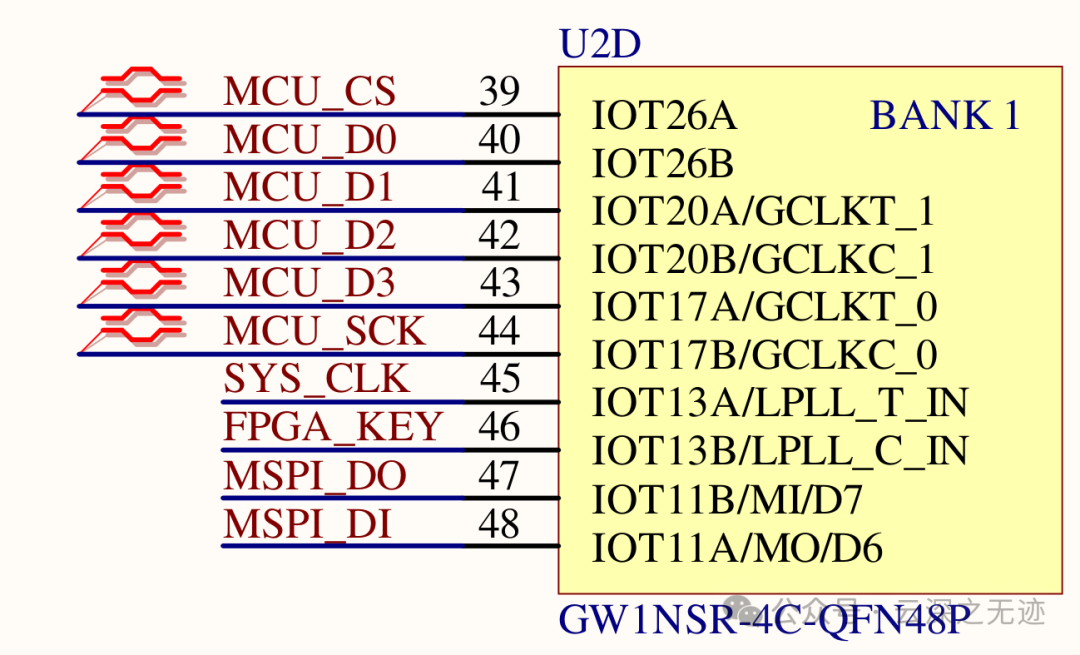

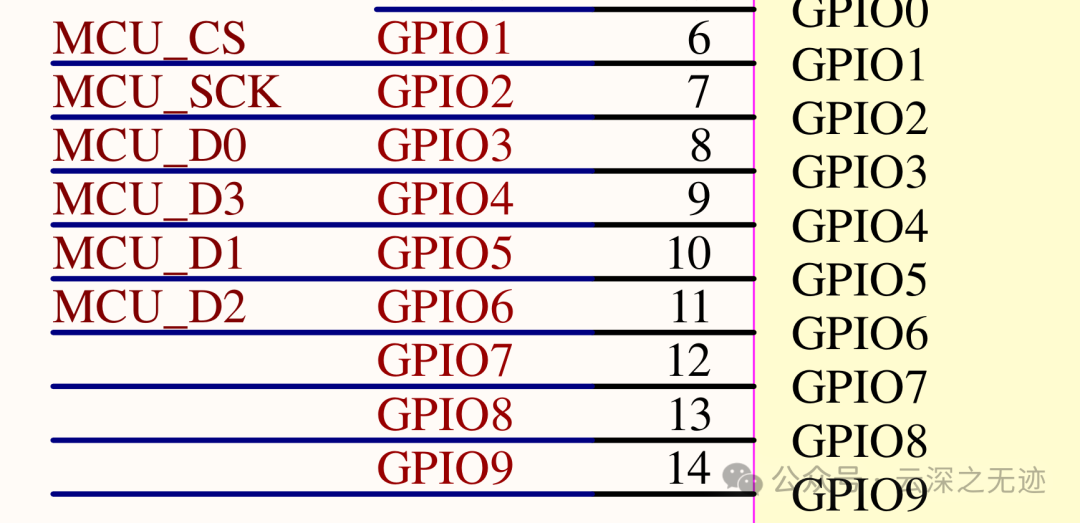

FPGA и MCU соединены между собой с помощью 6 линий передачи данных. При его использовании сначала позвольте 32 управлять PMIC для питания FPGA, а затем подключите Arduino к Oita.

определение

Будьте осторожны при подключении к Интернету

То есть 4 линии передачи данных, часы и выбор чипа.

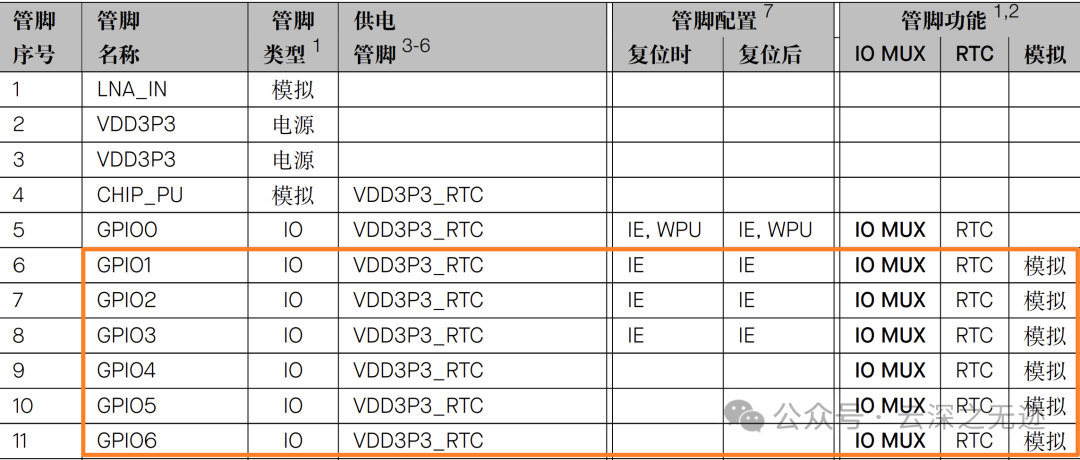

Это действительно выбор не нарушать контакты MCU.

код напряжения

https://www.espressif.com/sites/default/files/documentation/esp32-s3_datasheet_cn.pdf

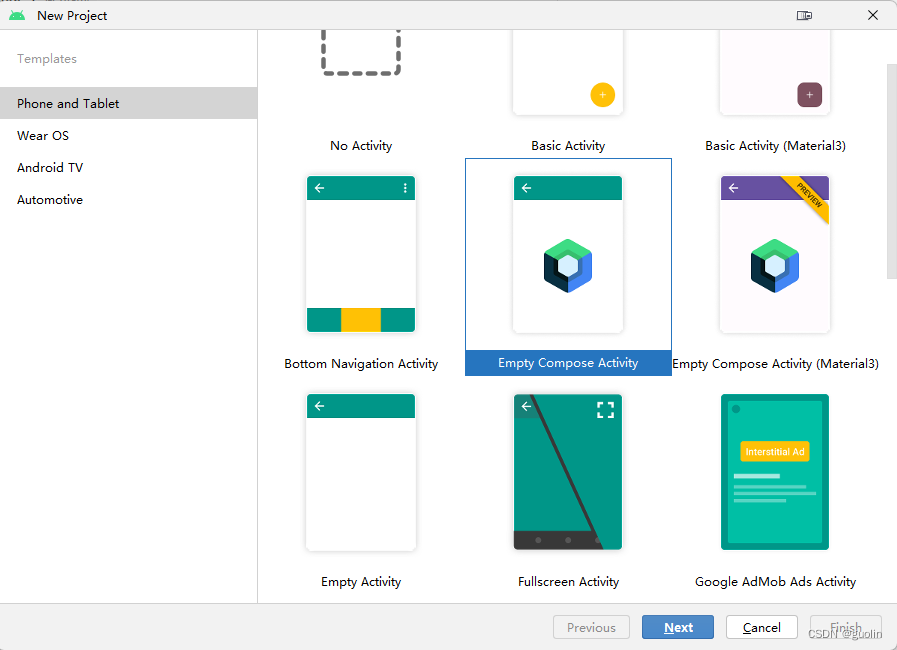

Учебное пособие по Jetpack Compose для начинающих, базовые элементы управления и макет

Код js веб-страницы, фон частицы, код спецэффектов

【новый! Суперподробное】Полное руководство по свойствам компонентов Figma.

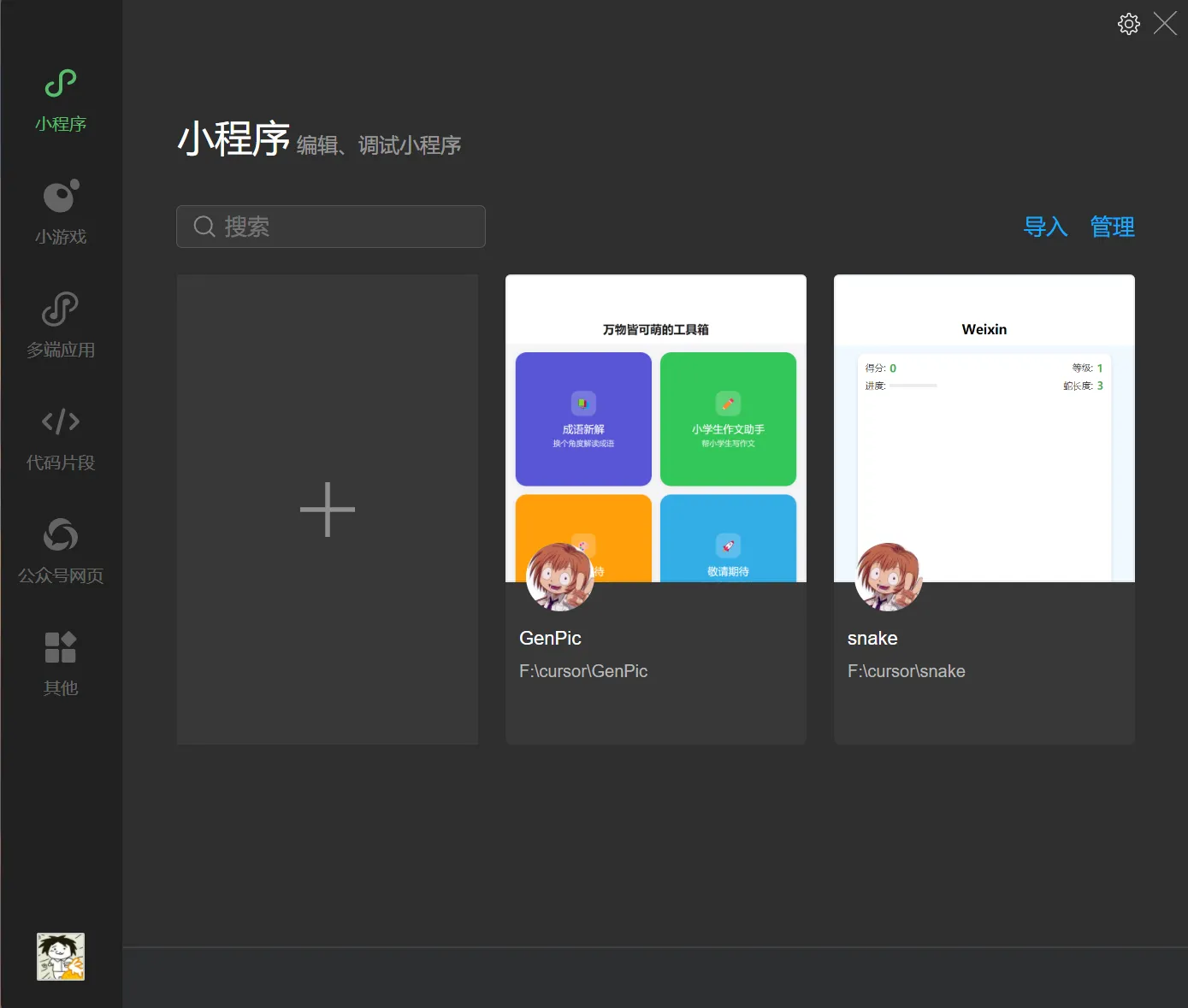

🎉Обязательно к прочтению новичкам: полное руководство по написанию мини-программ WeChat с использованием программного обеспечения Cursor.

[Забавный проект Docker] VoceChat — еще одно приложение для мгновенного чата (IM)! Может быть встроен в любую веб-страницу!

Как реализовать переход по странице в HTML (html переходит на указанную страницу)

Как решить проблему зависания и низкой скорости при установке зависимостей с помощью npm. Существуют ли доступные источники npm, которые могут решить эту проблему?

Серия From Zero to Fun: Uni-App WeChat Payment Practice WeChat авторизует вход в систему и украшает страницу заказа, создает интерфейс заказа и инициирует запрос заказа

Серия uni-app: uni.navigateЧтобы передать скачок значения

Апплет WeChat настраивает верхнюю панель навигации и адаптируется к различным моделям.

JS-время конвертации

Обеспечьте бесперебойную работу ChromeDriver 125: советы по решению проблемы chromedriver.exe не найдены

Поле комментария, щелчок мышью, специальные эффекты, js-код

Объект массива перемещения объекта JS

Как открыть разрешение на позиционирование апплета WeChat_Как использовать WeChat для определения местонахождения друзей

Я даю вам два набора из 18 простых в использовании фонов холста Power BI, так что вам больше не придется возиться с цветами!

Получить текущее время в js_Как динамически отображать дату и время в js

Вам необходимо изучить сочетания клавиш vsCode для форматирования и организации кода, чтобы вам больше не приходилось настраивать формат вручную.

У ChatGPT большое обновление. Всего за 45 минут пресс-конференция показывает, что OpenAI сделал еще один шаг вперед.

Copilot облачной разработки — упрощение разработки

Микросборка xChatGPT с низким кодом, создание апплета чат-бота с искусственным интеллектом за пять шагов

CUDA Out of Memory: идеальное решение проблемы нехватки памяти CUDA

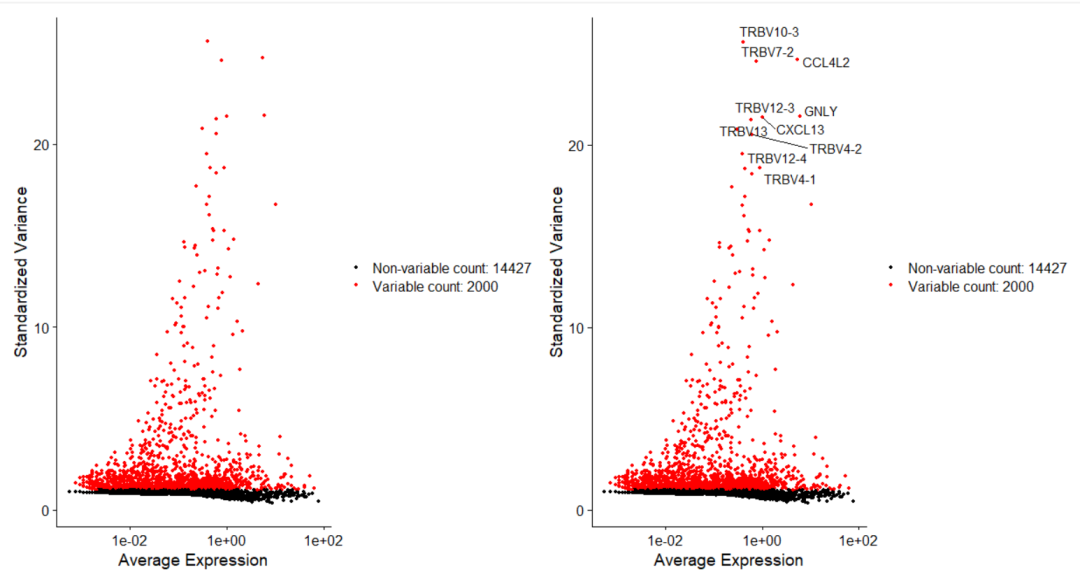

Анализ кластеризации отдельных ячеек, который должен освоить каждый&MarkerгенетическийВизуализация

vLLM: мощный инструмент для ускорения вывода ИИ

CodeGeeX: мощный инструмент генерации кода искусственного интеллекта, который можно использовать бесплатно в дополнение к второму пилоту.

Машинное обучение Реальный бой LightGBM + настройка параметров случайного поиска: точность 96,67%

Бесшовная интеграция, мгновенный интеллект [1]: платформа больших моделей Dify-LLM, интеграция без кодирования и встраивание в сторонние системы, более 42 тысяч звезд, чтобы стать свидетелями эксклюзивных интеллектуальных решений.

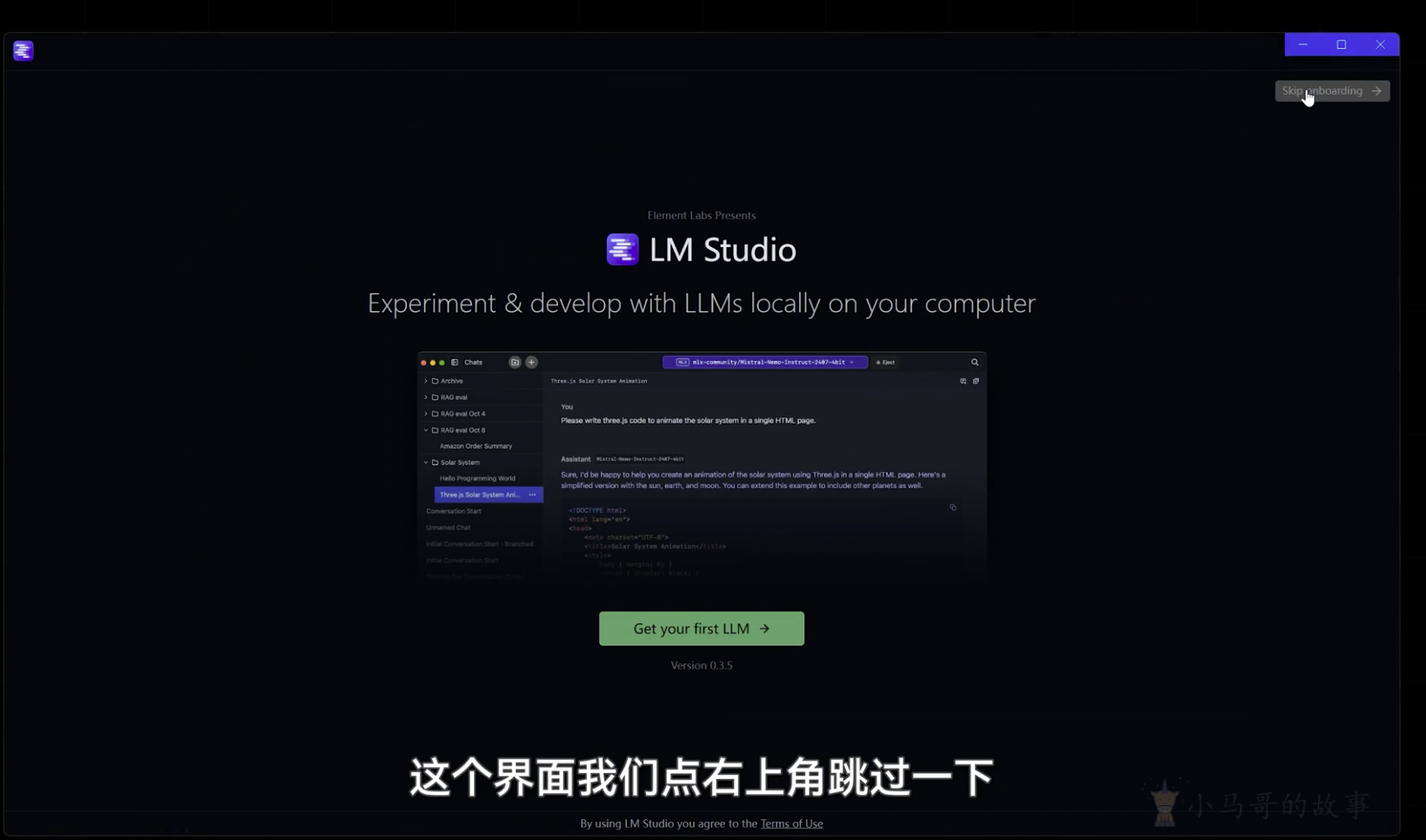

LM Studio для создания локальных больших моделей

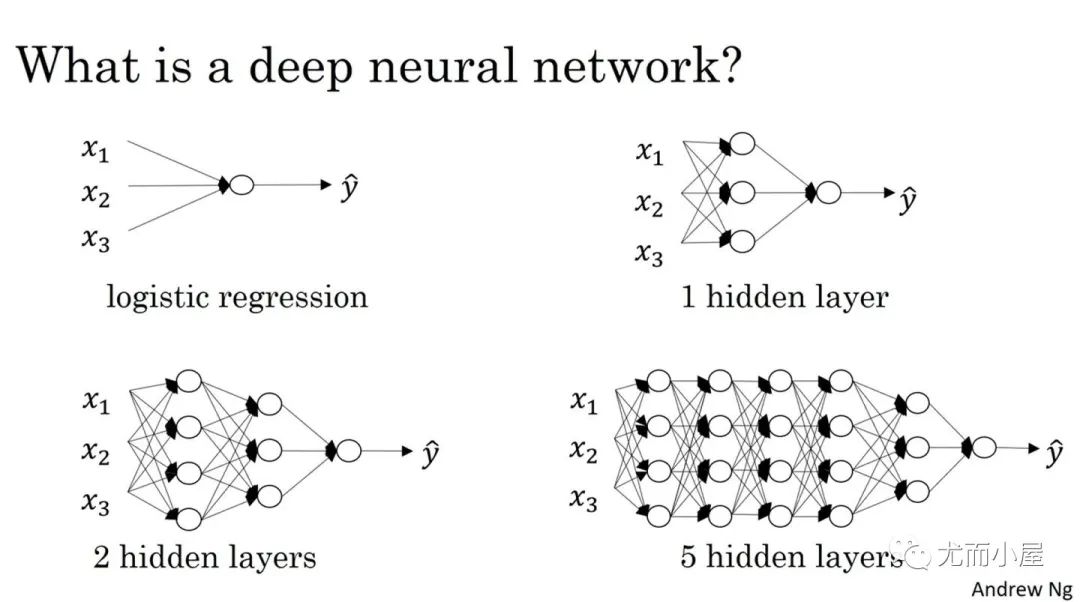

Как определить количество слоев и нейронов скрытых слоев нейронной сети?